作者:羅迪·厄克哈特(Roddy Urquhart)

大多數(shù)集成電路包括至少一個處理器內(nèi)核和一些嵌入式軟件。對于更復雜的片上系統(tǒng) (SoC),可能有運行主軟件和操作系統(tǒng)的應(yīng)用程序處理器以及多個專門的子系統(tǒng)處理通信、安全性和傳感器等功能。處理要求差別很大,有多種處理器 IP 內(nèi)核可供選擇。處理器 IP 供應(yīng)商通常通過顯示 PPA 數(shù)字(性能、 功耗和面積)相互競爭,但此類指標需要上下文信息,并且可能具有誤導性。 那么, 設(shè)計人員在選擇處理器 IP 內(nèi)核時需要考慮哪些事項呢?

指令集架構(gòu) (ISA)

選擇處理器最重要的考慮因素之一是指令集架構(gòu)。30年前,許多集成設(shè)備制造商擁有自己的微控制器架構(gòu),市場被許多指令集架構(gòu)分割。 然而 ,在當時 ,電腦市場由X86架構(gòu)主導,X86不但擊敗了所有挑戰(zhàn)產(chǎn)品 ,而且開發(fā)了大量的應(yīng)用軟件。

隨著 20 世紀 90 年代處理器 IP 公司的出現(xiàn),越來越多的半導體公司采用第三方處理器IP, Arm 成為手機和嵌入式的主導架構(gòu)。這導致許多公司開發(fā)的產(chǎn)品具有與競爭產(chǎn)品相同的處理器內(nèi)核,這限制了芯片產(chǎn)品的差異化。然而,隨著Arm ISA的廣泛使用,一個令人印象深刻的軟件生態(tài)系統(tǒng)被開發(fā)出來。

數(shù)十年來,Arm一直被視為獨立于半導體公司之外,提供某種“瑞士中立性”。軟銀公司(SoftBank)的收購破壞了這種中立性,這意味著Arm不再獨立。這一點因Arm和Arm中國之間的緊張關(guān)系而加劇。如果Nvidia的收購通過,Arm將由持牌人擁有,完全失去任何中立的假象。許多半導體公司會因為競爭對手半導體公司的關(guān)鍵技術(shù)而感到不安。

在選擇 ISA 時,您需要考慮許多事項。其中三項最重要,包括:

a)復雜性

b)軟件生態(tài)系統(tǒng)

c)開放和中立

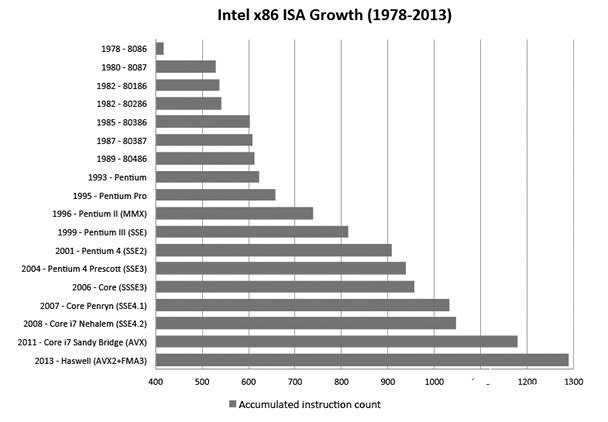

多年來,人們在增加ISA復雜性和減少ISA復雜性方面都做出了努力。坎皮納斯大學的一項研究表明,在1986年至2013年之間,X86架構(gòu)增長了3倍多。Arm 的 ISA 也發(fā)生了類似的增長。

來源 - ISA Aging: A Case Study(《指令集架構(gòu)老化:一項案例研究》),坎皮納斯大學

相反,加州大學伯克利分校的 RISC 項目始于 1980 年,當時只使用了 32 條指令,但利用流水線設(shè)計和寄存器窗口實現(xiàn)性能。這個概念被太陽微系統(tǒng)公司商業(yè)化為SPARC。1981 年,斯坦福大學 MIPS 項目開發(fā)了一個小型 ISA,包含 16 位和 32 位指令的組合。

最近,加州大學伯克利分校的克爾斯特·阿薩諾維奇(Krste Asanovi?)開始了“3個月項目(3-month project)”,目的是開發(fā)一個干凈利落的 ISA。這樣做是因為專有 ISA 具有局限性,包括:

?專利保護 – 成本

?ISA 所有權(quán)與處理器設(shè)計之間的聯(lián)系 – 單一供應(yīng)商

?許多 ISA 的復雜性 – 通常不需要

?ISA 可能會隨著其擁有公司而消亡 – 風險會隨時間而變

這成為開放的 RISC-V ISA 標準。

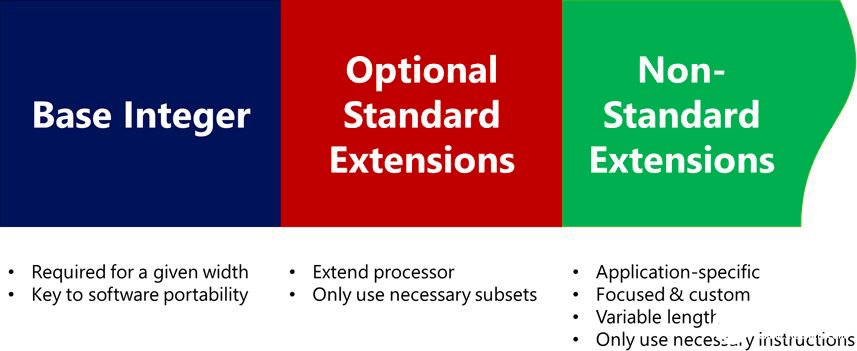

RISC-V 的一個關(guān)鍵特征是它不是通用的 ISA。它認識到不同的應(yīng)用需要不同程度的 ISA 復雜性。其中有一個非常小的基本指令集(只有 47 個指令的 32 位處理器),然后是一系列可根據(jù)需要使用的可選標準擴展。最后,還有用于創(chuàng)建非標準自定義指令的預配。

與專有商業(yè) ISA 不同,RISC-V 使您能夠?qū)?ISA 與其設(shè)計需求相匹配。 例如,來自 Arm 的高端 Cortex-A 處理器將具有 800 多個指令,但它們都是必需的嗎?使用 RISC-V 時,您可使用基本 ISA 加上具體所需的擴展,如 [G] 和 [P]。

軟件的可用性是一個關(guān)鍵的考慮因素。某些軟件僅在有限數(shù)量的 ISA 上可用,例如,安卓到目前為止僅移植到 Arm 和 MIPS。對于嵌入式軟件 ,許多軟件都有源代碼,因此可以移植到幾乎任何 ISA,而有些有二進制代碼。對于Arm來說,二進制形式的軟件有很多選擇,但對于其他專有的 ISA,選擇范圍小得多。

使用 RISC-V,如果將嵌入式軟件編譯到基本指令集或標準擴展(如 RV32IMC)的通用組合,那么不管目標處理器是什么,它都可以輕松以二進制形式交付。

最后,考慮 ISA 的開放性很有用。專有架構(gòu)通常與單個公司聯(lián)系在一起,因此依賴于該公司的運行狀況和生存能力。如果Arm和MIPS由半導體公司所有,其他開發(fā)集成電路的公司就不再認為它們是中立的。

RISC-V 開放 ISA 由獨立的 RISC-V 國際組織所有,而不是由單個公司擁有。因此,因此,即使提供RISC-V處理器IP的公司資不抵債,也可以選擇其他RISC-V內(nèi)核供應(yīng)商。投資針對 RISC-V 內(nèi)核的軟件是一種低風險選擇。

性能

看看任何處理器 IP,您會發(fā)現(xiàn)其供應(yīng)商強調(diào) PPA(性能、功率和面積)數(shù)字。從理論上講,它們應(yīng)為比較不同的處理器IP內(nèi)核提供一個公平的競爭環(huán)境,但實際上 情況更為復雜。 讓我們考慮一下什么是“性能”。

首先要考慮的是,您關(guān)心性能的哪些方面?您更關(guān)心所需的絕對吞吐量(每秒性能),還是更關(guān)心每 MHz 的性能?在機器視覺等持續(xù)運行且需要使用復雜算法的應(yīng)用中,您很可能會關(guān)心絕對吞吐量。但是,如果您有一個低占空比的無線傳感器節(jié)點,當節(jié)點喚醒時,您將希望它在盡可能少的時鐘周期內(nèi)處于活動狀態(tài)。這意味著您將關(guān)心每 MHz 實現(xiàn)的計算量。

大約 40 年前,計算機以MIPS(每秒數(shù)百萬條指令)為基礎(chǔ)進行比較,但問題是——什么是“指令”? 各種指令在復雜性和架構(gòu)上有很大的不同,因此,在CISC處理器中的一個操作通常比在RISC處理器中需要的周期更少。MIPS 只有在將產(chǎn)品與類似體系結(jié)構(gòu)進行比較時才有所幫助,有些人稱之為“毫無意義的性能指數(shù)”!

另一個要考慮的事項是您最關(guān)心的計算類型。這是整數(shù)操作嗎?如果是,是哪些操作?還是表示浮點計算?在過去,MFLOPS(每秒百萬個浮點操作)是一種受歡迎的衡量標準。但同樣,什么是“操作”?

如今,綜合基準已普遍用于處理器 IP 內(nèi)核。它們具有以下特征:

a)它們相對較小,便于攜帶,

b)它們代表常用的相關(guān)應(yīng)用,

c)它們透明且可重復,

d)它們可以公平地應(yīng)用于一系列處理器,

e)它們將基準結(jié)果表示為單個數(shù)字。

過去 36 年來流行的基準是 Dhrystone 基準。其名稱取自與一度流行的“惠斯登基準”(Whetstone benchmark)相比較的文字游戲。惠斯登基準通專注于浮點操作,而 Dhrystone 則專注于整數(shù)和字符串操作。Dhrystone 基準結(jié)果通常被引用為 DMIPS(Dhrystone 分數(shù)除以名義上的 1MIPS 機器的分數(shù))。該基準測試一直受到批評,因為現(xiàn)代編譯器可以優(yōu)化部分工作,這意味著它部分測試的是編譯器,而不是處理器性能。

對于浮點,Whetstone 目前很少使用, 有時也會使用 LINPACK 等替代方法。LINPACK 涉及使用浮點數(shù)對矩陣進行 LU 分解。結(jié)果用 MFLOPS 表示。

自 2009 年以來,另一個流行的嵌入式應(yīng)用綜合基準是 EEMBC 的 CoreMark? ,CoreMark?旨在開展代表嵌入式整數(shù)處理需求的操作。其中包括列表處理、矩陣操作、有限狀態(tài)機和 CRC。

由加州大學伯克利分校的戴夫·帕特森(Dave Patterson)領(lǐng)導的一個小組批評了所有的合成基準,轉(zhuǎn)而建議Embench作為使用真實程序的替代方案。隨著該行業(yè)的進一步發(fā)展,時間會告訴我們這種做法是否會贏得業(yè)內(nèi)的關(guān)注,但計劃采用浮點基準令人鼓舞。

正如您所看到的,那里有許多不同的基準測試系統(tǒng),每個系統(tǒng)都適合度量略有不同的性能類型。那么,在為項目選擇處理器IP時,如何評估性能呢? 如果您的嵌入式軟件具有與綜合基準類似的操作,則該基準可能會快速簡單地為您提供有用的初始指導。但是,此類基準通常以 MHz 報價,例如 CoreMark/MHz。如果您在按周期尋找良好效果,每兆赫數(shù)字值通常是低功率應(yīng)用的一個好指標。但是,如果您正在尋找高絕對性能,這可能是誤導。相反,您應(yīng)該考慮說,按您的目標時鐘頻率可實現(xiàn)的 CoreMarks。

如果您的主要問題是浮點性能,請記住 DMIPS 和 CoreMark 是整數(shù)基準。您最好根據(jù)浮點基準(如Whetstone或 LINPACK)比較內(nèi)核; 然而,這些基準相當舊。

最后,強烈建議將時間投入在處理器內(nèi)核上運行逼真的軟件,以此評估內(nèi)核是否為您提供所需的性能。即使綜合基準測試給了你快速的指示,也沒有什么可以替代使用真正的應(yīng)用軟件。如果您正在查看 RISC-V,那么可了解計算瓶頸在哪里的分析軟件也會評估添加自定義指令是否可以提高性能。

復雜性

處理器內(nèi)核越復雜,面積和功耗越大 。但是,增加復雜性并不是單一維度,因為處理器可能在不同的方面更為復雜。在選擇處理器 IP 內(nèi)核時,為項目選擇正確的復雜類型非常重要。

思考復雜性的方法包括:

-字長

-執(zhí)行單元

-特權(quán)/保護

-虛擬內(nèi)存

-安全功能

通常,字長越小,內(nèi)核越小,功率越低,但情況并非總是如此。8 位內(nèi)核(如 8051)在柵極數(shù)上與最小的 32 位內(nèi)核相當,但功耗通常更差。8 位內(nèi)核需要更多的內(nèi)存訪問,每個時鐘周期的計算更少,需要的周期更多,因此需要更多的動態(tài)功率來完成計算。

處理器內(nèi)核在執(zhí)行單元的復雜性方面差異很大。最簡單的是基本的單個ALU(算術(shù)邏輯運算單元),需要通過簡單的指令實現(xiàn)許多常見操作,例如使用 shift and add算法來實現(xiàn)乘法。因此,內(nèi)核具有硬件乘法器和除法器是司空見慣的事。在需要良好的浮點性能時,添加硬件浮點單元將顯著提高性能。此選項可用于 Codasip 的 Bk3 和 Bk5 RISC-V 內(nèi)核,但代價是內(nèi)核尺寸約擴大為兩倍。

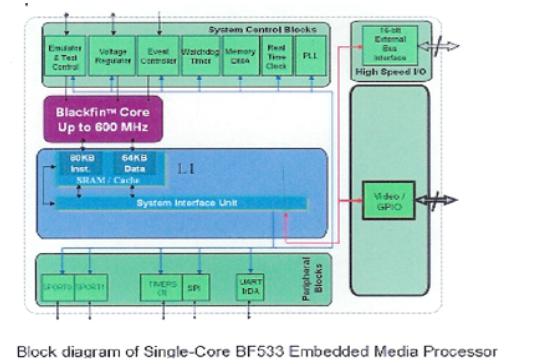

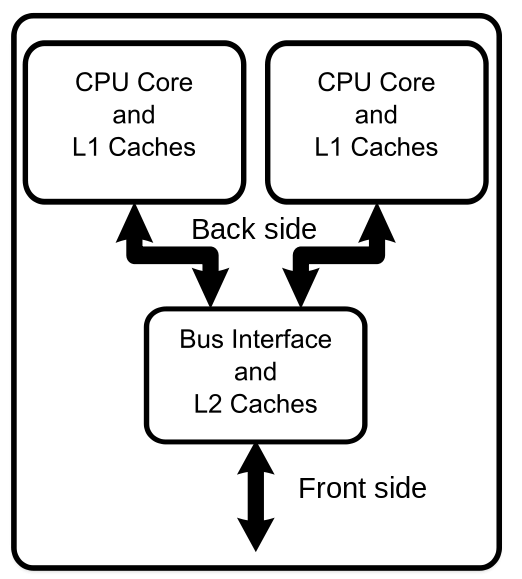

到目前為止,我們已經(jīng)假設(shè)了一次執(zhí)行一個指令的標量處理單元和一個計算線程。Superscalar 體系結(jié)構(gòu)具有指令級并行性,能夠獲取多個指令并將它們發(fā)送到不同的執(zhí)行單元。例如,西部數(shù)據(jù) EH1 和 EH2 SweRV 內(nèi)核有兩個執(zhí)行單元。處理一個線程的雙發(fā)射內(nèi)核處理理論上可以使單發(fā)射內(nèi)核的性能翻倍。

但是,線程可能會使兩個執(zhí)行單元暫時處于非活動狀態(tài)。如果存在兩個硬件線程(harts),如果一個線程停止,另一個線程可以繼續(xù)執(zhí)行。

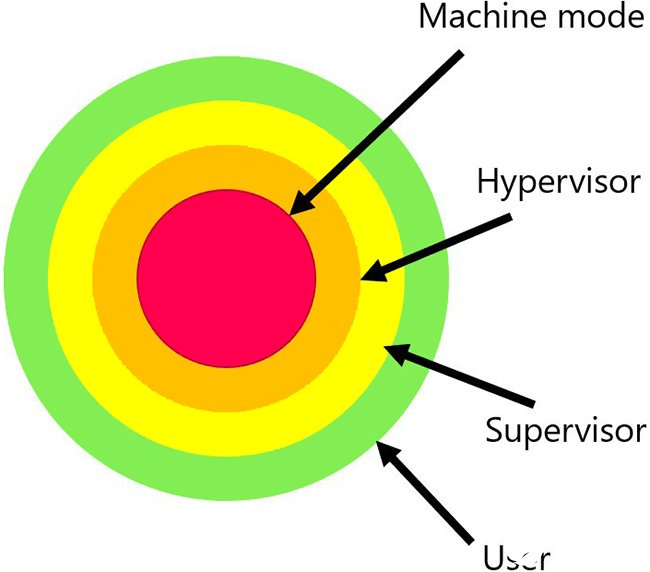

另一個復雜的領(lǐng)域是特權(quán)模式 - 通常模式越多,核心邏輯越復雜。許多嵌入式應(yīng)用程序在機器模式下運行,這意味著其代碼具有對內(nèi)核的完全訪問權(quán)限,就像 Linux 中的根權(quán)限一樣。必須完全信任此類代碼,才能避免負面后果。在更復雜的應(yīng)用中,可能會提供一系列特權(quán),如機器、主管和用戶。普通應(yīng)用將在用戶模式下運行,保護量最大,某些需要更大權(quán)限的軟件將使用主管模式。Linux 需要所有三種模式。 RISC-V 規(guī)范還定義了物理內(nèi)存保護 (PMP),以此防止特權(quán)較低的模式訪問某些內(nèi)存空間。

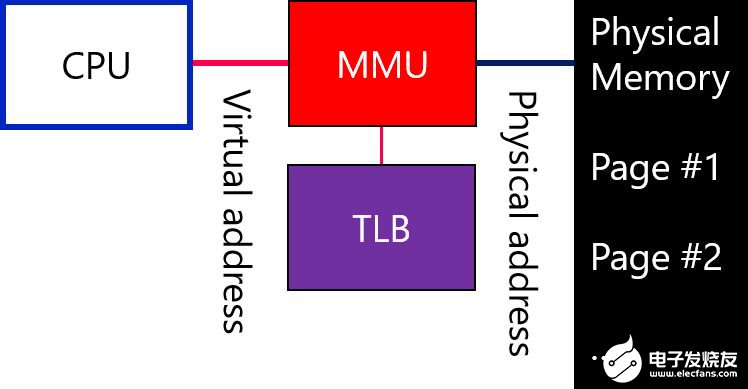

虛擬內(nèi)存還需要額外的處理器資源,如內(nèi)存管理單元 (MMU) 和轉(zhuǎn)譯后備緩沖器 (TLB)來處理將虛擬內(nèi)存地址轉(zhuǎn)換為物理地址。這會在不提高處理器吞吐量的情況下,在面積和功耗方面帶來額外的成本。然而,虛擬內(nèi)存對于使用豐富的操作系統(tǒng)(如 Linux)很有必要,這些操作系統(tǒng)能夠使用更復雜的軟件。

最后, 硬件安全功能增加了邏輯。這可能以向存儲器提供電子加密/解密的形式,提供糾錯編碼和篡改檢測塊功能。

因此,選擇處理器內(nèi)核時,要弄清您需要什么樣的執(zhí)行單元、內(nèi)存管理 、特權(quán)和安全。這種組合將決定內(nèi)核的復雜性。

操作系統(tǒng)

對于每個嵌入式產(chǎn)品,軟件開發(fā)人員需要考慮是否需要操作系統(tǒng);如果是這樣,操作系統(tǒng)的類型千差萬別,包括內(nèi)存占用很小的實時操作系統(tǒng),以及具有豐富特性的通用操作系統(tǒng)(如Linux)。

為您的產(chǎn)品選擇適當?shù)牟僮飨到y(tǒng)類型,并因此確定嵌入式處理器所需的功能,很大程度上取決于您是否面臨硬性實時要求。安全關(guān)鍵系統(tǒng)和工業(yè)系統(tǒng)(如防鎖制動系統(tǒng)或電機控制)將具有最大硬響應(yīng)時間。在該頻譜的另一端,如果平均性能足夠,則音頻或游戲設(shè)備等消費類系統(tǒng)可能能夠容忍緩沖。據(jù)說這樣的系統(tǒng)有軟實時要求。

硬實時需求可以通過編寫直接控制底層硬件的所謂裸機軟件來實現(xiàn)。有時,處理器資源非常有限、軟件非常簡單和/或?qū)崟r要求非常嚴格,引入進一步的抽象層會使?jié)M足這些硬實時需求變得復雜時,這時通常會使用裸機編程。這種方法的缺點是,這樣的裸機軟件需要作為一個單一的任務(wù)(加上中斷例程)來編寫,這使得程序員很難在其復雜性增長時維護軟件。

在處理更復雜的嵌入式軟件時,使用實時操作系統(tǒng) (RTOS) 通常比較有利。它允許程序員將嵌入式軟件拆分為多個線程,這些線程的執(zhí)行由RTOS的小而低開銷的“內(nèi)核”管理。使用多線程范式使開發(fā)人員能夠創(chuàng)建和維護更復雜的軟件,同時仍然允許足夠的響應(yīng)。RTOS 通常使用分配給單個線程的“優(yōu)先級”概念進行操作。然后,RTOS 可以“搶占”(暫時停止)優(yōu)先級較低的線程,這樣做有利于那些具有較高優(yōu)先級的線程,以此滿足所需的實時限制。在采用復雜的庫或協(xié)議堆棧(如 TCP/IP 或藍牙)時,通常需要使用 RTOS,因為這種第三方軟件通常已經(jīng)包含多個線程。如今,許多開源和商業(yè)許可的RTOSes可供選擇。

對于一個簡單的RTOS(例如FreeRTOS或Zephyr)來說,嵌入式處理器的要求的確不高。擁有只配置機器模式 (M) 和定時器外設(shè)的 RISC-V 處理器就足夠了。因此,這些 RTOS 可以在任何 Codasip RISC-V 內(nèi)核或西部數(shù)據(jù) SweRV 內(nèi)核上運行。但是,由于機器模式對具有相關(guān)風險的所有內(nèi)存和外圍設(shè)備提供不受限訪問權(quán)限,因此需要嚴密的軟件開發(fā)。通過專門的 RTOS(例如為功能安全(如 SAFERTOS)或安全開發(fā)的 RTOS,可以提供額外的保護。

如果處理器內(nèi)核同時支持機器 (M) 和用戶 (U) 權(quán)限模式,并且具有物理內(nèi)存保護 (PMP),則有可能在受信任代碼(具有不受限訪問權(quán)限)和其他應(yīng)用程序代碼之間建立隔離。使用 PMP,受信任的代碼為應(yīng)用程序代碼的每個部分設(shè)置規(guī)則,并規(guī)定允許訪問內(nèi)存(或外圍設(shè)備 )的哪些部分。例如,PMP 可用于防止第三方代碼干擾應(yīng)用程序其余部分的數(shù)據(jù),或檢測堆棧溢出。因此,使用 PMP 可提高系統(tǒng)的安全性,但代價是需要額外的硬件來支持它。

對于需要更高級用戶界面、復雜 I/O 和網(wǎng)絡(luò)(如機頂盒或娛樂系統(tǒng))的應(yīng)用程序,RTOS 可能過于簡單化。如果有復雜的計算、對完整的進程隔離和多任務(wù)處理的要求、文件系統(tǒng)和存儲支持,或者通過設(shè)備驅(qū)動程序?qū)?yīng)用程序代碼與硬件完全分離,也同樣適用。此類系統(tǒng)通常具有軟實時要求,且最好由通用豐富的操作系統(tǒng)(如 Linux)提供。如前所述,Linux 需要多種 RISC-V 特權(quán)模式(計算機、主管和用戶模式(M、S、U))以及用于虛擬到物理地址轉(zhuǎn)換的內(nèi)存管理單元 (MMU)。此外,與簡單的 RTOS 相比,此類系統(tǒng)的內(nèi)存占用量要大得多。

最后,對于需要硬實時響應(yīng)和 Linux 等豐富操作系統(tǒng)功能的嵌入式系統(tǒng),通常使用兩個通信處理器子系統(tǒng)進行設(shè)計,一個支持 RTOS,另一個運行 Linux。

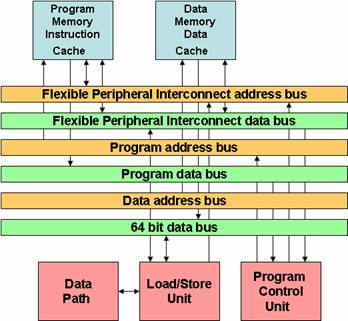

子系統(tǒng)硅面積

設(shè)計中任何部分的面積都會影響硅成本和功耗。在處理器IP供應(yīng)商的PPA編號中簡單地遵循“A”可能會引起誤解。處理器從來都不是孤立的,它是子系統(tǒng)的一部分,另外還包括指令存儲器、數(shù)據(jù)存儲器和外設(shè)。在大多數(shù)情況下,指令內(nèi)存將占主導地位,而處理器面積則不那么重要。

指令內(nèi)存的大小將受目標指令集、編譯器和使用的編譯器切換的影響。在 RISC-V 的情況下,選擇可選的標準擴展和自定義擴展可以極大地影響代碼大小。

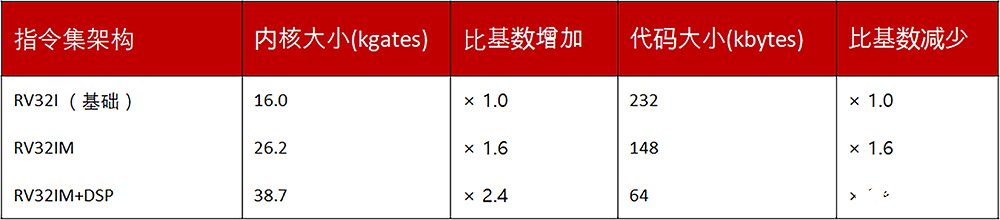

資料來源:《為物聯(lián)網(wǎng)應(yīng)用實施 RISC-V》,Dan Ganousis & Vijay Subramaniam,設(shè)計自動化會議 2017

為了說明這一點,上表顯示了向內(nèi)核和代碼大小添加擴展的效果。在此示例中,Microsemi 使用 Codasip RISC-V Bk3 內(nèi)核實現(xiàn)音頻處理應(yīng)用。從32位基指令集開始,它們的編碼和循環(huán)計數(shù)高得令人無法接受。通過添加乘法 [M] 擴展實現(xiàn)了一些改進,但突破是使用自定義 DSP 指令。這使得編碼大小減少了3.6倍,但與基礎(chǔ)內(nèi)核相比,以增加2.4倍的核心尺寸為代價。在指令內(nèi)存占主導地位的情況下,這是一個很好的權(quán)衡; 此外,性能目標很容易實現(xiàn)。

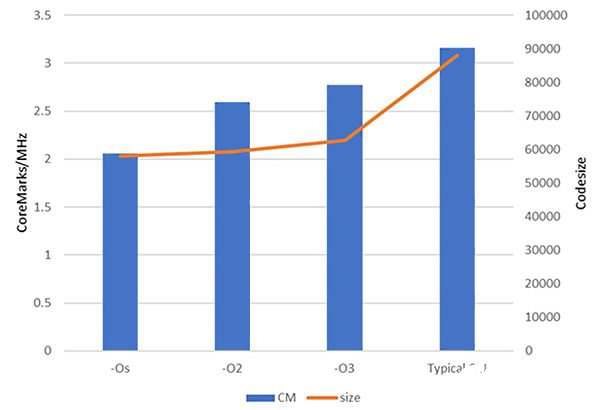

對于典型的供應(yīng)商 PPA 數(shù)據(jù),通常使用一組復雜的編譯器交換機引用一些綜合基準(如 CoreMark/MHz)。但在實踐中,嵌入式軟件可能會使用常見的交換機(如-Os或-O3)進行編譯。

請考慮利用通用的 GCC 編譯器使用不同的交換機編譯 CoreMark 基準。在這種情況下,目標是具有 3 階段流水線的 Codasip RV32IMC RISC-V 內(nèi)核。下圖顯示了不同編譯器設(shè)置的 CoreMark/MHzcodesize和代碼大小度量值。最后一個示例是典型的供應(yīng)商性能數(shù)據(jù),其中許多交換機用于 CoreMark (CM = “-O3 -flto -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=8 -falign-loops=8 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -fno-reg-struct-return -fno-rename-registers --param case-values-threshold=8 -fno-crossjumping -freorder-blocks-and-partition -fno-tree-loop-if-convert -fno-tree-sink -fgcse-sm -fgcse-las -fno-strict-overflow”)。

在此示例中,CoreMark/MHz 分數(shù)隨著交換機從左到右的變化而增長。但是,有趣的是,最復雜的一組交換機在“-O3”上增加了40%的編碼大小,而性能只提高了14%。

并不是每個示例都會這樣運行,但編譯器交換機會影響性能和代碼大小。重要的是要實事求是地了解要使用的編譯器交換機,并確保任何性能基準數(shù)據(jù)的交換機與用于評估代碼大小的交換機相匹配。

許可模式

每個人都熟悉傳統(tǒng)處理器 IP 供應(yīng)商(如 Arm、Cadence 和 Synopsys) 的商業(yè)許可。但是,在討論 RISC-V 開放指令集架構(gòu) (ISA) 時,普遍存在著術(shù)語上的混淆,即通常被描述為“開源”的RISC-V。有些人甚至指責商業(yè)RISC-V IP的供應(yīng)商,如Codasip或Andes不符合RISC-V的精神。但現(xiàn)實是什么?

讓我們簡要地看一下定義。像C、Verilog或HTTP這樣的開放標準是由獨立組織維護的文檔定義的。因此,C 由 ISO 維護,Verilog 由 IEEE 維護,HTTP 由 IETF 維護。這些組織使用一套公正的規(guī)則維護技術(shù)標準。這樣的開放標準通常可自由訪問。

使用開源, 軟件包的源代碼或硬件塊的硬件描述語言源可使用許可證提供。開源許可證從限制性許可證(如非盈利版權(quán)許可證)到許可授權(quán)(如 Apache)各不相同。開源許可證定義使用、研究、修改和分發(fā)代碼的權(quán)利。非盈利版權(quán)許可證將要求任何修改都是開源的,而許可授權(quán)則不開放。

RISC-V是一個開放標準,ISA 不定義任何微體系結(jié)構(gòu)或業(yè)務(wù)模型。因此,RISC-V 微體系結(jié)構(gòu)可以作為商業(yè) IP 許可證或作為開源許可證獲得許可。沒有規(guī)定。

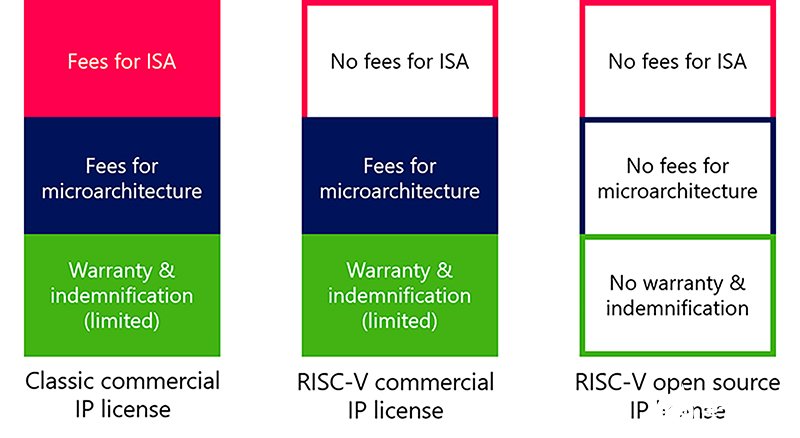

如果我們想到一個經(jīng)典的商業(yè)處理器IP許可證,您一般支付:

-使用供應(yīng)商的 ISA 的權(quán)利,

-使用供應(yīng)商的微觀體系結(jié)構(gòu)的權(quán)利,

-保修,

-供應(yīng)商承諾修復錯誤,

-賠償。

在實踐中,保修通常有時限,賠償有限。但是,對于被許可方,如果發(fā)現(xiàn)錯誤,尤其在日程緊張時發(fā)現(xiàn)的錯誤有價值,供應(yīng)商有一些復設(shè)計的承諾。如果被許可人被指控專利侵權(quán),知識產(chǎn)權(quán)賠償意味著供應(yīng)商將代表被許可人為指控辯護或解決。

經(jīng)典 IP 供應(yīng)商小心翼翼地保護自己的 ISA 以及他們的微觀體系結(jié)構(gòu)。普通許可證將 ISA 的使用與微體系結(jié)構(gòu)捆綁在一起,并且沒有修改可交付結(jié)果的權(quán)利。此類供應(yīng)商很少提供架構(gòu)許可證,允許被許可方在自己的微體系結(jié)構(gòu)中使用ISA,但是這樣的許可要求的費用很高。RISC-V非常具有破壞性的一個原因是,免費開放的ISA是最有價值的可交付產(chǎn)品之一,而且不需要支付許可費。

鑒于 RISC-V 沒有規(guī)定微體系結(jié)構(gòu)或如何獲得許可,因此既有商業(yè)許可,也有開源的 RISC-V IP 內(nèi)核。使用開源許可證時,您無需為微型體系結(jié)構(gòu)支付許可證費用,但您也無法獲得商業(yè)許可證的所有好處。通常,交付物沒有擔保,并要接受“現(xiàn)狀”。同樣,商業(yè)許可證也不存在賠償。如果發(fā)現(xiàn)錯誤,則許可證方或開源社區(qū)需要修復它們。

對于商業(yè)許可的 RISC-V 內(nèi)核,只有費用與微體系結(jié)構(gòu)相關(guān),因為 RISC-V ISA 是免費許可的。有了此許可證,您可以獲得通常與商業(yè)許可證相關(guān)的保修、賠償和錯誤修復承諾。

那么,RISC-V 的哪個選擇正確呢?商業(yè)許可證和開源許可證都有優(yōu)點和缺點。您需要權(quán)衡最適合您的設(shè)計項目。

在Codasip, 我們提供商業(yè)RISC-V IP許可證,并支持采用開源SweRV內(nèi)核。過去,商業(yè)許可證和開源許可證一直被視為激烈的競爭對手。然而, 在軟件界,微軟等公司已經(jīng)接受了這兩種模式。Microsoft 提供商業(yè)許可證,支持開源項目,并且具有基于云的業(yè)務(wù)模型。Codasip 深信,商業(yè)和開源 RISC-V 許可證可以共存并相互補充。

結(jié)論

選擇處理器是一項復雜的任務(wù),需要明確評估您的底層需求。對諸如供應(yīng)商PPA數(shù)據(jù)或基準測試之類的度量進行膚淺的評估可能會產(chǎn)生誤導,并最終導致對處理器的次優(yōu)選擇。

出發(fā)點應(yīng)該是清楚地了解 SoC 項目需要什么。您是希望打開 ISA 還是由單個公司控制?您是否關(guān)心絕對吞吐量或每個時鐘周期的計算量?您面臨的是硬實時需求,還是需要一個豐富的操作系統(tǒng)? 實現(xiàn)計劃性能需要哪些計算單位?您需要在處理器內(nèi)核上運行什么軟件, ISA 和編譯器怎樣組合會讓您實現(xiàn)所需的整個子系統(tǒng)領(lǐng)域?最后,比起避免許可證費, 您更關(guān)心獲得保修, 承諾修復潛在的錯誤和賠償?

審核編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評論