引 言

??? 二乘二取二系統的兩套計算機系統各有兩個CPU,并且所有結構和配件完全相同。兩套系統之間采取雙機熱備份,大幅提高了系統可靠性,在一些領域得到了廣泛應用。基于二乘二取二容錯結構的計算機聯鎖系統在國外已有成熟的應用,如K5B和E132,其良好的可靠性和安全性引起國內業界的廣泛關注。

??? 系統可靠性冗余設計是提高系統可靠性的重要方法,但由于冗余會增加系統成本、體積和重量,因此必須合理地選擇冗余結構和數量。對價格昂貴、重量大、體積大的冗余部分,更應作合理考慮。由于二乘二取二硬件冗余技術是通過多個相同部件完成同一功能,在提高系統可靠性的同時也存在一些不足:

??? ◆增加了系統的成本、結構、重量和所需空間;

??? ◆在某些情況下硬件技術的應用受到限制;

??? ◆對大型復雜系統均采用硬件冗余技術是不可能的。

??? 以上不足將限制二乘二取二冗余技術的應用,Fusion和coreABC的組合為以上問題提供了良好的解決方案。

1 二乘二取二系統

??? 二乘二取二系統有4個CPU,兩個CPU組成一組。每兩個CPU的輸出經比較器表決輸出,兩個CPU和一個比較器表決系統組成一個子系統。兩個子系統具有完全相同的硬件結構,一個為主單元,一個作為備用單元。開機后兩個子系統獨立同步工作,系統取工作單元的輸出為系統輸出。當兩個子系統均正常工作時,系統取主單元的輸出為系統輸出,若備用單元發生故障,系統輸出仍為主單元的輸出,備用單元進入維修狀態。當主單元發生故障時,系統切換至備用單元,此時系統輸出為備用單元的輸出,主單元進入維修狀態;一旦主單元維修完畢,可以正常工作時,則系統切換至主單元,取主單元的輸出為系統輸出。若主單元和備用單元均無法正常工作,則系統故障,系統無法繼續正常工作。除子系統故障時系統自動切換外,系統還具有手動切換的功能。由于兩個子系統具有完全相同的結構和進行完全相同的工作,所以手動切換不影響系統的正常工作。導致系統故障的因素有很多,根據不同的應用場合,需要針對不同的故障進行檢測和維修。二乘二取二系統的工作示意圖如圖1所示。

2 系統的具體實現

??? 在設計時,首先要考慮FPGA門電路的數量,以及嵌入4個軟核所要占用的門陣列資源。其次,要考慮其他硬件資源,比如時鐘、存儲器等。綜合各方面的考慮,本設計選擇Actel的Fusion StartKit數模混合FPGA實現二乘二取二系統。Fusion StartKit數模混合FPGA擁有600萬門門陣列,片內集成了Flash存儲器、RAM、FIFO和模擬模塊;片外提供48 MHz的晶振;支持coreABC軟核的嵌入。

2.1 軟核的嵌入

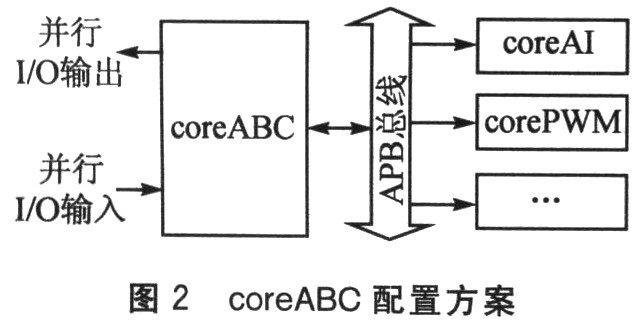

??? coreABC是一種具有高可配置性的軟核,占用資源少,特別適于低端應用。它能夠掛載可編程高級外圍總線(APB),支持APB總線下的外圍設備,通過coreAI直接控制ACM塊,還可配置8位、16位和32位APB接口。可以通過APB總線控制coreAI核,進行電壓、電流采集,以及模數轉換。圖2給出一種配置方案。coreABC可使用軟/硬代碼存儲方式,本設計采用硬代碼存儲方式。硬代碼存儲方式只需占用門陣列資源,而軟代碼存儲方式要占用Flash存儲口資源。由于FPGA片內集成了2個Flash存儲口,嵌入4個核時Flash存儲口資源不足。Actel coreABC的推出對實現可配置的小系統極具意義,它使用很少的系統資源就可搭建起完整的控制單元。

2.2 比較電路的實現

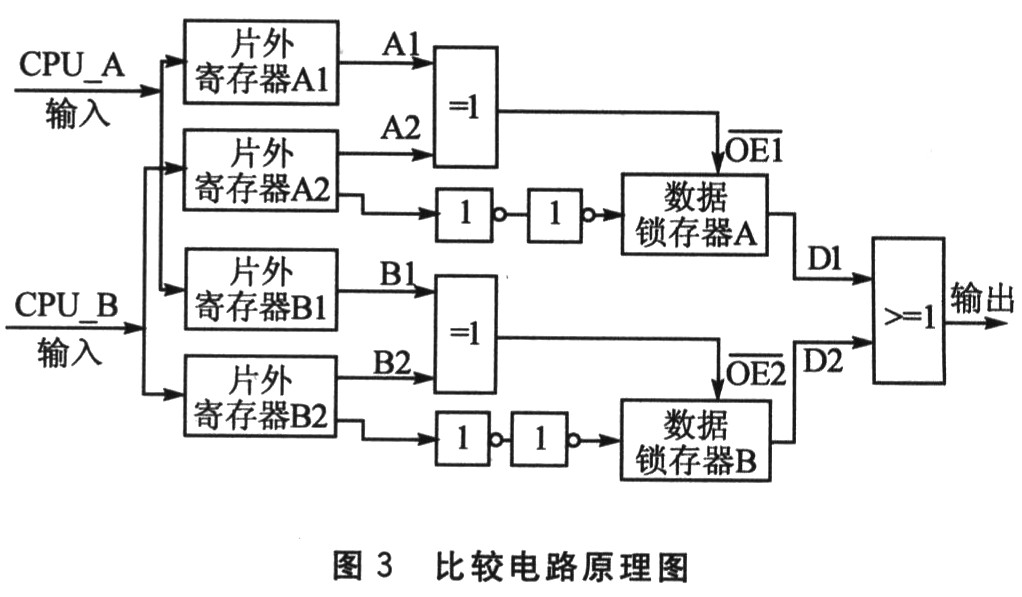

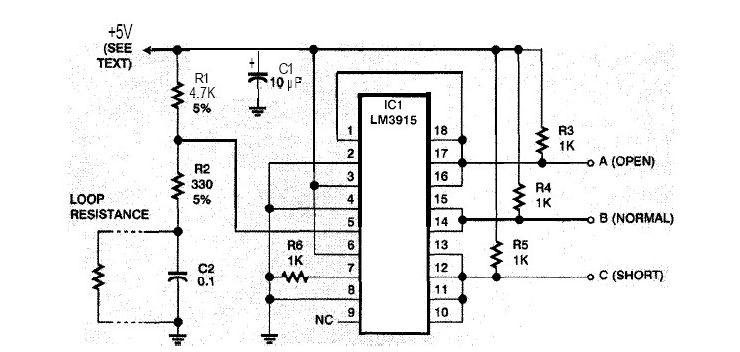

??? 二取二CPU的比較電路采用冗余設計,它主要負責對coreABC軟核的總線信號進行比較判決,保證系統正常運行,其電路圖如圖3所示。比較電路的工作原理為:片外寄存器分別從兩個CPU獲得總線數據信息,經異或模塊OE1=A1+A2,OE2=B1+82進行判斷,分別控制數據鎖存器輸出,并配合時鐘信號控制鎖存器同步輸出;從鎖存器輸出的數據經或電路處理后形成比較結果,即DATA_OUT=D1+D2。若比較結果確認CPU此次運算一致,則系統正常輸出;若比較電路確認CPU運算有誤,則重新進行運算。

??? 此外,在對CPU輸出數據進行比較的同時,比較電路還對CPU是否正常工作進行故障診斷。診斷正常則反饋CPU正常工作信息,使CPU進行下一周期的工作;診斷為故障則反饋CPU錯誤信息,此時系統切換,取另一組子系統的輸出為系統輸出,故障子系統進入維修狀態。這樣確保了系統的可靠性、安全性。

2.3 系統切換

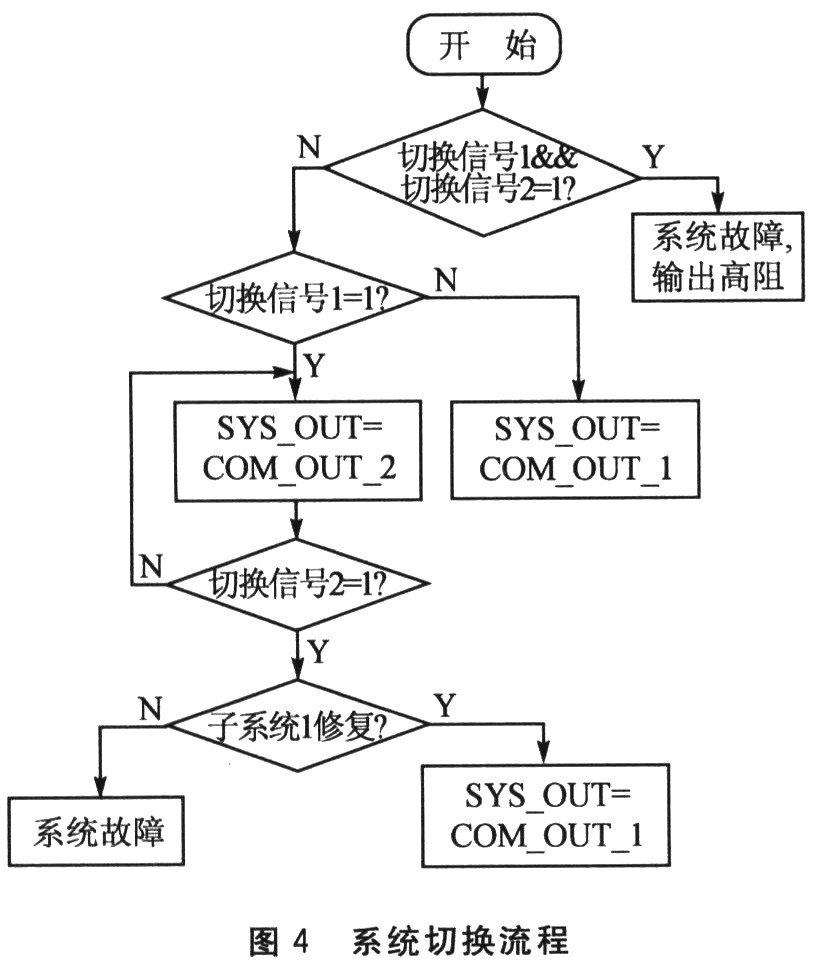

??? 系統切換是二乘二取二系統首要的功能要求,當工作單元出現故障,或者手動切換時,要求進行系統切換。本設計進行了兩組故障檢測。

??? 首先,為每個子系統的兩個coreABC分別設置兩個看門狗定時器,要求兩個coreABC向各自的看門狗發送周期自檢信號。若看門狗在溢出前收到該信號則CPU正常工作,否則溢出,該CPU判為故障。子系統的兩個CPU中,只要有一個出現故障,在備機正常的情況下,系統就進行切換。其次,將CPU輸出結果和子系統輸出結果進行比較,若相同則系統正常,否則系統故障。若備用單元正常,則系統切換,取備用單元輸出為系統輸出。

??? 將主單元和備用單元的看門狗溢出信號分別記為WD_PLUSE_1、WD_PLUSE_2,比較器判決信號記為COM_RESULT_1、COM_RESULT_2,手動切換信號記為SWITCH_1、SWITCH_2。只要系統故障或手動切換時,系統進行切換,由此可得切換信號為:

??? AUTO_RST_1=WD_PLUSE_1 ‖COM_RESULT_1 ‖SWITCH_1

??? AUTO_RST_2=wD_PLUSE_2 ‖COM_RESULT_2 ‖SWITCH_2

??? 系統切換通過以下語句實現:

??? SYS_OUT=(AUTO_RST_1&&AUTO_RST_2)?1'bz:((AUTO_RST_1)?COM_OUT_2:COM_OUT_1);

??? 若主機正常工作,則輸出取主機的比較輸出;若主機故障,在備用單元正常時,則系統切換取備用單元的輸出;若主機修復,則切換到主機工作;若兩個子系統均故障,則系統故障。實現的流程如圖4所示。

??? 對二乘二取二系統結構分析可知,二乘二取二結構同其他冗余方法雙模和三模結構相比,系統的安全性可以在較長時間內保持在一個很高的水平。同時二乘二取二結構的系統可靠性和平均壽命等指標均較高,所以是一種綜合性能比較好的冗余結構。

結 語

??? 本文選擇了合適的開發板資源,提出一種在FPGA中嵌入4個coreABC軟核,實現二乘二取二系統的方法。恰當地利用單芯片有限的資源,嵌入4個coreABC軟核,遵循二乘二取二系統的工作原理,合理實現二取二總線比較判決、故障檢測和二乘系統切換,經綜合后燒入,檢驗系統功能完全正常。

??? 本設計的優勢在于單芯片的功耗更小、電路設計更加便捷、系統可靠性和安全性更高、體積小、易維護和易升級換代,符合現階段我國聯鎖系統向模塊化、智能化、功能多樣化方向發展的要求,大大擴展了嵌入式系統應用的廣度和深度。嵌入式系統在應用領域發展迅速,隨著FPGA技術的進步,單芯片內的邏輯門電路數量更多,軟核的編寫更加成熟。單芯片多軟核的二乘二取二系統具有更強的生命力,它的高可靠性和低成本勢必帶來廣闊的應用空間。

電子發燒友App

電子發燒友App

評論