DSP+FPGA部分 FPGA + DSP結構,DSP采用TMS320C6455,FPGA采用XC5VSX95T-1FF1136T具備CPCI接口,PCI為32bit 33MHzDSP具有千兆網絡DSP

2014-06-24 14:01:53

公司的 RapidIO Switch; DSP之間通過 RapidIOX4互聯,Hyperlink X4 互聯,SGMII互聯,每片DSP外掛 1GB DDR3 ,32MB Nor Flash

2015-09-22 16:09:34

公司的Spartan XC3S200AN 配置芯片;一片 IDT 公司的 RapidIO Switch; DSP之間通過 RapidIOX4互聯,Hyperlink X4 互聯,SGMII互聯,每片

2015-05-15 17:34:08

RapidIO X4 EDMA 中斷 數據傳輸。 5) FPGA 完整的 DDR2控制、網絡數據收發傳輸。 6) FPGA Rocket 光纖數據傳輸測試程序。 7) DSP與FPGA的RapidIO

2015-05-19 17:34:31

TMS320C6678芯片,支持DDR3, Nor Flash, 以太網接口,DSP之間通過HyperLink互聯。DSP 的TSIF1外接連接器。 3) FPGA部分支持8路光纖 2.5Gbps

2015-09-17 14:38:59

TMS320C6678芯片,支持DDR3, Nor Flash, 以太網接口,DSP之間通過HyperLink互聯。DSP 的TSIF1外接連接器。 3) FPGA部分支持8路光纖 2.5Gbps 輸入輸出

2015-09-11 16:55:46

一、板卡概述 板卡由我公司自主研發,基于VPX架構,主體芯片為兩片 TI DSP TMS320C6678,兩片Virtex-6 XC6VSX315T-ff1156 FPGA,1個RapidIO

2014-05-30 11:36:40

RapidIO X4 EDMA 中斷 數據傳輸。 5) FPGA 完整的 DDR2控制、網絡數據收發傳輸。 6) FPGA Rocket 光纖數據傳輸測試程序。 7) DSP與FPGA

2015-05-11 17:14:29

RapidIO X4 EDMA 中斷 數據傳輸。 5) FPGA 完整的 DDR2控制、網絡數據收發傳輸。 6) FPGA Rocket 光纖數據傳輸測試程序。 7) DSP與FPGA的RapidIO

2015-09-14 11:56:15

RapidIO X4 EDMA 中斷 數據傳輸。 5) FPGA 完整的 DDR2控制、網絡數據收發傳輸。 6) FPGA Rocket 光纖數據傳輸測試程序。 7) DSP與FPGA的RapidIO

2015-09-18 15:24:37

各出一個千兆網口,另外2個網絡連于背板。前面板FPGA出兩個千兆網口,6個SFF模塊光纖,支持5Gbps前面板出4個指示燈,1個復位按鈕。DSP與FPGA之間 RapidIOX4互聯,DSP的Uart

2015-05-14 17:56:53

各出一個千兆網口,另外2個網絡連于背板。前面板FPGA出兩個千兆網口,6個SFF模塊光纖,支持5Gbps前面板出4個指示燈,1個復位按鈕。DSP與FPGA之間 RapidIOX4互聯,DSP的Uart

2015-09-11 16:11:46

各出一個千兆網口,另外2個網絡連于背板。前面板FPGA出兩個千兆網口,6個SFF模塊光纖,支持5Gbps前面板出4個指示燈,1個復位按鈕。DSP與FPGA之間 RapidIOX4互聯,DSP的Uart

2015-09-15 15:34:38

大家好,我現在在畫一塊28335的板子,想實現與FPGA之間的通信,但是不知道該怎樣設計,包括FPGA與DSP連接的引腳、通過內部什么模塊實現數據通信,現在一頭霧水,請大家幫忙。謝謝。

2018-12-03 15:55:34

DSP代碼大部分使用C語言編寫,實現了所需的功能,現在想移植到FPGA板子上,不知道該怎么辦?需要全部轉換Verilog代碼嗎?有沒有簡便一點的方法。。。

2015-01-23 13:35:51

用的貴公司的TL138F-EVM A2開發板。想利用SPI協議實現FPGA和DSP通信。看了核心板引腳說明 沒有看到FPGA這邊SPI協議要用的接口,是不是這塊板子不能實現DSP和FPGA的SPI通信。麻煩床龍工程師指導下。還有其他方法嗎?

2020-04-24 06:46:47

本人剛入門FPGA,不知道如何實現FPGA+DSP,FPGA+ARM接口設計,網上查詢有的說FPGA+DSP可以通過EMIF,IP核實現,FPGA+ARM可以通過SPI,有沒有具體硬件參考的?

2016-08-27 11:30:26

各位高手,小弟想實現FPGA下的網絡數據包抓取,應該怎么實現?功能與Sniffer相似!

2013-01-22 06:54:09

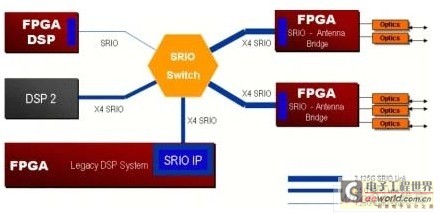

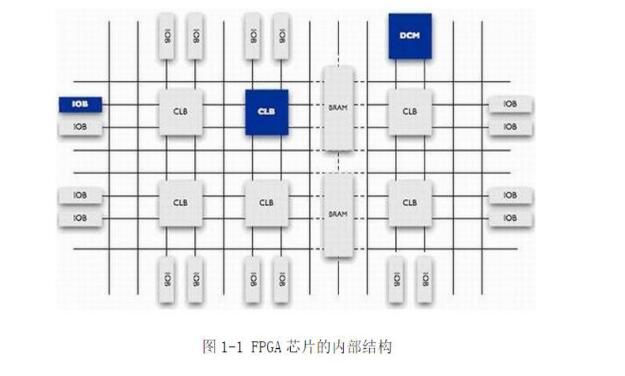

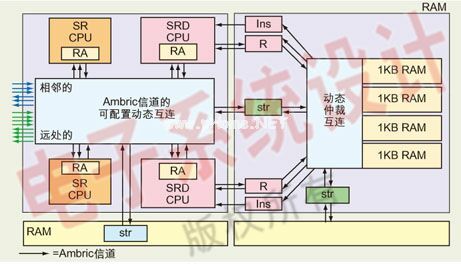

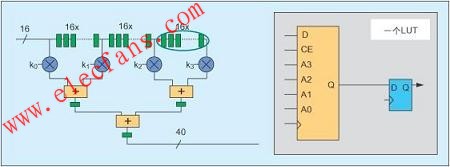

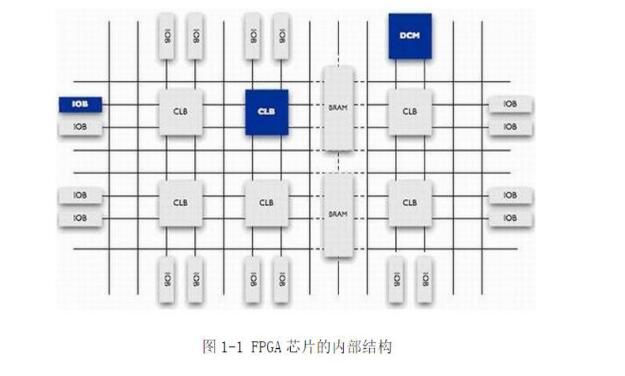

、功能多個角度解析兩者的不同。1、FPGA與DSP的特點FPAG的結構特點片內有大量的邏輯門和觸發器,多為查找表結構,實現工藝多為SRAM。規模大,集成度高,處理速度快,執行效率高。能完成復雜的時序

2019-05-07 01:28:40

和比較,并給出了FPGA與這兩種DSP芯片進行鏈路口通倍的具體方法。在FPGA內部實現了DSP鏈路口的設計,同時給出了DSP進行鏈路口通信的具體設置方法。由于實時處理中數據的重發會嚴重影響處理的實時性

2019-06-19 05:00:08

和比較,并給出了FPGA與這兩種DSP芯片進行鏈路口通倍的具體方法。在FPGA內部實現了DSP鏈路口的設計,同時給出了DSP進行鏈路口通信的具體設置方法。由于實時處理中數據的重發會嚴重影響處理的實時性,故

2018-12-04 10:39:29

一般涉及到數字處理和邏輯控制都用DSP加FPGA實現,最近想用FPGA實現數字處理和邏輯控制,聽搞通信的說多加幾個門就可以了,數字處理時鐘要求25MHZ,請高手指點一下。

2013-04-05 10:01:31

的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-21 09:22:42

FPGA實現和編程的一個方法是采用知識產權(IP)的模塊或核心。例如,大多數標準DSP功能都在Xilinx庫中以可參數配置的DSP核心的形式實現了,它們通過Xilinx公司的CORE生成器提供。包括

2011-02-17 11:21:37

FPGA設計之浮點DSP算法實現,DSP算法是很多工程師在設計過程中都會遇到的問題,本文將從FPGA設計的角度來講解浮點DSP算法的實現。FPGA設計之浮點DSP算法實現是賽靈思工程師最新力作,資料不可多得,大家珍惜啊1FPGA設計之浮點DSP算法實現[hide][/hide]

2012-03-01 15:23:56

fpga+dsp 4路ad采集系統,you嘗,rapidio pcieddr3 各種高速外圍接口 代碼有償。qq2715957785

2018-02-24 08:34:21

本人使用virtex 5 與dsp c6678 srio通信,fpga是從模式,一直使用的1x。現在調試4x的時候遇到問題,4x會自動變成1x通信,或者:dsp成4x,fpga也訓練成4x,但是此時

2018-06-21 00:10:20

DSP各出一個千兆網口,另外2個網絡連于背板。前面板FPGA出兩個千兆網口,6個SFF模塊光纖,支持5Gbps前面板出4個指示燈,1個復位按鈕。DSP與FPGA之間 RapidIOX4互聯,DSP

2021-11-01 11:23:03

) 通過本地總線、RapidIO與DSP連接; 7) 提供主FPGA所有接口代碼的封裝庫;DSP子系統規格 1) 選用TI公司8核DSP,型號TMS320C6678,工作主頻1GHz; 2) 外掛1

2019-09-06 10:15:41

反復編程使用。DSP、FPGA芯片雖成本略微高于ASIC芯片,但具有貨源暢通、可多次編程使用等優點。在中小批量通信產品的設計生產中,用FPGA和DSP實現HDLC功能是一種值得采用的方法。HDLC的幀

2011-03-17 10:23:56

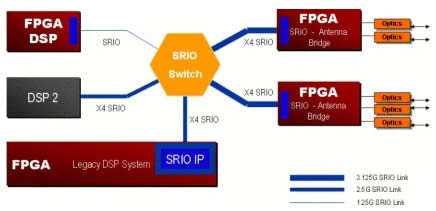

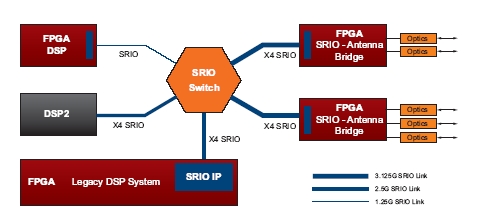

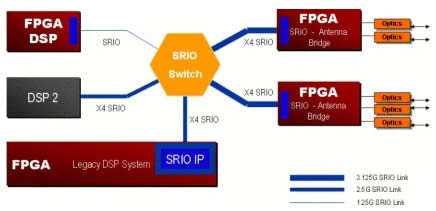

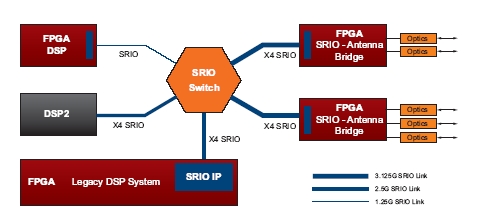

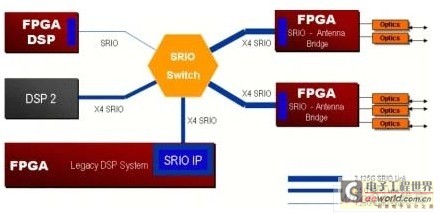

RapidIO正是滿足這些要求的最佳選擇。以無線基站為例,在SRIO出現之前,無線基站的基帶處理的典型框圖如圖7所示。圖7 傳統無線基站基帶處理框圖在傳統的基站中,DSP與ASIC或FPGA之間的互連一般用外部

2016-12-09 11:24:30

本人在北京工作7年以上,從事FPGA外圍接口設計,非常熟悉Serial RapidIO協議,設計調試了多個基于Serial RapidIO接口的DSP和PowerPC信號處理卡.本人非常

2014-08-23 13:27:47

處理器的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-21 09:20:11

處理器的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-24 13:07:08

PowerPC,dsp和fpga實現,fpga負責接收E1口,K口等數據,通過dsp的mcbsp接口傳輸到dsp,進行話音編解碼處理,然后通過HPI接口與PowerPC交互,或者通過dsp的網口直接收發數據。整個設備相當于一個路由器,它可以接入各種電臺!

2015-09-10 11:15:14

容量

?FPGA 外掛2組FMC HPC 連接器;

?FPGA 引出1路QSPF+,數據速率25GbpsX4/s;

?FPGA與DSP之間通過RapidIO互聯 。

?VPX 連接器上外接FPGA

2023-10-16 11:12:06

以上,從事FPGA外圍接口設計,非常熟悉Serial RapidIO協議,設計調試了多個基于Serial RapidIO接口的DSP和PowerPC信號處理卡.本人非常熟悉Spartan-6

2015-11-11 15:06:39

隨著通訊系統的數據處理量日益增大,過去總線形式的體系結構逐漸成為約束處理能力進一步提升的瓶頸。本文首先簡單介紹了嵌入式設計中總線結構的演化過程,從而引出新一代點對點串行交換結構RapidIO。

2019-11-01 06:05:21

要跟上日益提高的性能需求,還得注意保持成本低廉有效利用基于串行RapidIO的FPGA作為DSP協處理器就能達到這些目的。那么,我們該怎么做呢?

2019-08-07 06:47:06

運算平臺之間是如何連接的?SRIO系統的應用實例有哪些?如何利用串行RapidIO去實現FPGA協處理?

2021-04-29 06:17:59

本文討論了一種基于RapidIO的具有雙主機節點的嵌入式系統互聯設計,給出系統設計方案及驅動軟件設計,并在具體應用環境中對設計方案進行了系統驗證。

2021-05-24 06:24:37

隨著通訊系統的數據處理量日益增大,過去總線形式的體系結構逐漸成為約束處理能力進一步提升的瓶頸。本文首先簡單介紹了嵌入式設計中總線結構的演化過程,從而引出新一代點對點串行交換結構RapidIO。

2019-09-02 07:10:22

視頻圖像方面,VGA格式和LVDS格式的視頻圖像疊加、旋轉和縮放;3. 高低速接口方面,rapidIO、PCIE-DMA、10G以太網GTX、DDR3、SPI、UART、I2C、CAN接口,與DSP

2016-07-02 15:31:38

在雷達信號處理機的設計中,RapidIO接口可以可靠地實現芯片與芯片之間、板卡與板卡之間和系統與系統之間的高速低延遲通信,具有很大的應用前景。

2013-03-17 13:34:01

我在做fpga與dsp的SRIO通信,我用的是論壇上提供的SRIO test程序,目前dsp端能夠實現端口0的外部回環測試。fpga端的協議還沒做通,我想用dsp直接給fpga發包,fpga根據收到

2018-06-21 10:45:13

我們設計的系統里面需要實現DSP28377和ARM之間的高速互聯,目前擬定的方案有雙口RAM并行總線互聯和SPI總線互聯,請問還有其它高速總線互聯方式嗎?

2018-09-20 14:14:15

TI 相關技術支持專家 你們好 : 我在一個項目中使用了DM385 作為視頻的解壓縮方案,現在要將壓縮后的視頻流傳輸到fpga 基帶,通過無線發送。想問一下,dm385 能不能通過u*** 實現互聯

2020-08-18 07:03:22

Hi,Ti guys,我在使用自己板上的c6678,利用論壇上keystone_srio程序調試dsp和fpga端的通信。同事從fpga(v6,srio核)看來收發地址都是34衛的,但我調DSP互聯

2018-12-28 11:08:14

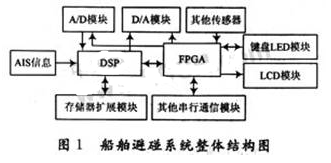

,數字控制信號經過 DA轉換后輸出模擬控制電壓到后端控制電路,實現對七路溫度的閉環控制。 4.FPGA與外圍電路之間的通信接口 FPGA與外圍電路之間的通信接口主要包括與溫度傳感器,DSP,232接口

2020-08-19 09:29:48

DSP芯片是專門為實現各種數字信號處理算法而設計的、具有特殊結構的微處理器,其卓越的性能、不斷上升的性價比、日漸完善的開發方式使它的應用越來越廣泛。將計算機網絡技術引入以DSP為核心的嵌入式系統

2019-06-20 05:00:04

DSP芯片是專門為實現各種數字信號處理算法而設計的、具有特殊結構的微處理器,其卓越的性能、不斷上升的性價比、日漸完善的開發方式使它的應用越來越廣泛。將計算機網絡技術引入以DSP為核心的嵌入式系統

2019-06-20 05:00:05

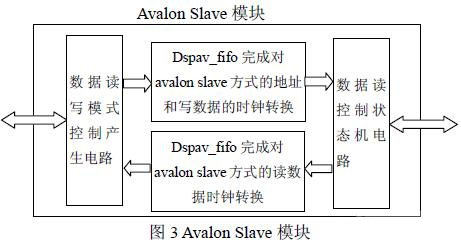

針對傳統總線PCI存在的問題,提出異步FIFO存儲轉發模式的串行RapidIO-PCI轉接橋方案,介紹RapidIO高速總線的體系結構及其性能優勢,根據PCI和RapidIO協議,給出轉接橋關鍵部分結構的設

2009-04-01 09:34:02 33

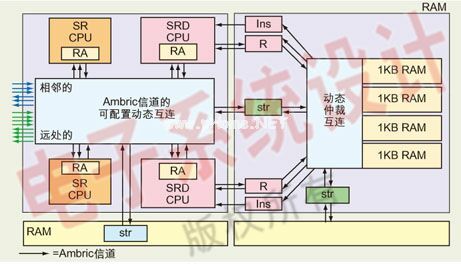

33 具有系統級性能的FPGA在半導體工藝的線寬達到深亞微米后更進一步按信號處理的要求改進器件結構和性能,不僅可實現VLSI DSP,且具有系統內可再編程的特性,可用流水和并行處

2009-05-09 12:57:35 16

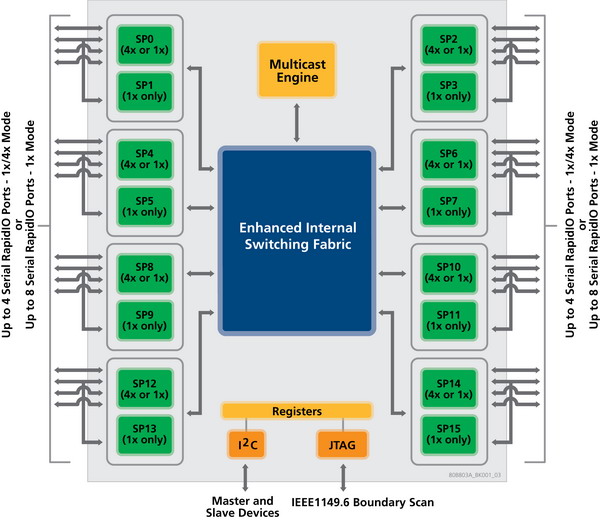

16 RapidIO 互連構架是一個開放的標準,可應用于連接多處理器、存儲器和通用計算平臺。本文簡要介紹了基于Tundra 公司TSI568 芯片的RapidIO 交換模塊的設計原理和實現方法,并對一些

2010-01-06 16:47:48 40

40 本文首先簡單的介紹了總線的發展,從而引出一種新型的串行點對點交換結構RapidIO。DSP 在高性能處理系統中的重要性毋庸置疑,但是目前的很多DSP 并沒有RapidIO接口。本文提出了

2010-01-25 14:25:19 32

32 FPGA實現DSP應用

摘要:具有系統級性能的FPGA在半導體工藝的線寬達到深亞微米后更進一步按信號處理的要求改進器件結構和性能,不僅可實現VLSI DSP,且具有系統

2010-04-01 15:39:54 14

14 FPGA的DSP應用

近年來由于多媒體技術和無線通信的發展,對DSP應用的要求不斷地增長,但是這些應用對信號處理要求高,需要采用處理速度高的硬件來實現DSP,所以,隨著CMOS工藝的

2010-04-07 14:25:58 16

16 用可再配置FPGA實現DSP功能

2010-07-16 17:56:43 10

10 比較了多種DSP芯片的互連性能,給出了一種簡單高性能DSP網絡結構。針對構成DSP網絡通訊接口的鏈路口,分析其基本特點,并且提出了在FPGA中實現的設計原理。最后給出了設計仿真圖和

2010-07-27 16:46:46 22

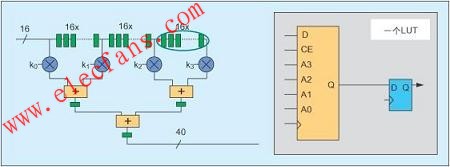

22 乘累加器在DSP算法中有著舉足輕重的地位。現在,很多前端DSP算法都通過FPGA實現。結合FPGA具體的硬件結構,提出了乘累加器在FPGA中實現的改進方法:流水線技術、CSD編碼、DA算法,

2010-08-06 14:41:38 29

29 分析當前高速互連網絡中同時存在的TCP/IP, GAMMA, InfiniBand, SCI 等技術的實現機制,介紹RapidIO 高性能總線技術。研究RapidIO 協議和MPC8548 處理器的相關技術,提出在RapidIO 高速互連網

2010-09-22 08:35:11 20

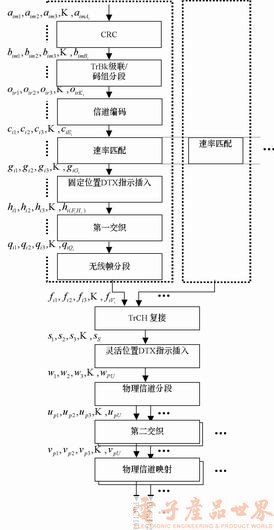

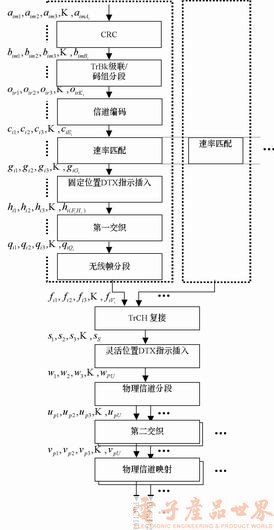

20 摘? 要: 本文在分析WCDMA系統基帶處理方案的基礎上,結合DSP和FPGA性能的比較,提出了一種在性能、靈活性和性價比上都比較理想的DSP+FPGA基帶發送的實現方案。 引言 隨

2006-03-11 13:29:42 670

670

基于DSP和FPGA的通用圖像處理平臺設計

摘要:設計一種基于DSP和FPGA架構的通用圖像處理平臺,運用FPGA實現微處理器接口設計,并對圖像數據進行簡單預處理,利用DSP

2010-02-01 11:10:21 1379

1379

利用串行RapidIO實現FPGA協處理

為了支持“三重播放”應用,人們對高速通信和超快速計算的需求日益增大,這向系統開發師、算法開發師和硬件工程師等人員提出了新

2010-02-25 17:06:55 1216

1216

用RapidIO提高DSP陣列的性能

“采用SERDES(串行/解串器)技術后只需少量引腳就能獲得很高的帶寬。由于硬件全部承擔了協議棧的處理,RapidIO減少了原來僅用于在系統中傳

2010-03-01 10:36:39 1318

1318

串行RapidIO交換器的應用優勢

EMIF6? 是由 Texas Instruments 開發的一款專利接口,在業內應用多年,反響良好。但是,EMIF6? 現正用于從未嘗試的 DSP 至 DSP 連接等應用。本文

2010-03-03 15:54:10 795

795

采用串行RapidIO連接功能增強DSP協處理能力

目前,對高速通信與超快計算的需求正與日俱增。有線和無線通信標準的應用隨處可見,數據處理架構每天都在擴展。較為普

2010-03-03 16:01:25 1134

1134

利用串行RapidIO實現FPGA協處理

為了支持“三重播放”應用,人們對高速通信和超快速計算的需求日益增大,這向系統開發師

2010-03-25 14:48:25 1389

1389

Spartan-3FPGA能以突破性的價位點實現嵌入式DSP功能。本文闡述了Spartan-3 FPGA針

2010-12-17 11:31:23 675

675

捅要:為了實現是彈武器瞄準自動化,本文設計了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統,采用QUartuBn在AJtera的FPGA器件CYCLONEII上設計了CCD驅動時序電路,采用PsPICE設計了可以

2011-02-25 13:48:05 187

187 摘要:為了實現高速HDLC通訊協議,設計了DSP+FPGA結構的485通訊接口,接口包括DSP、FPGA、485轉換等硬件電路,以及DSP與FPGA之間的數據交換程序和FPGA內部狀態機;其中DSP用于實現數據控制,FPGA用于實現HDLC通訊協議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 摘要:針對數控系統的工作特點和要求,通過對TI公司新推出的DSP芯片TMS320F2812和ALTERA公司的FPGA芯片EP1K30功能和特點的深入分析,給出了一種基于DSP和FPGA的運動控制卡的設計與實現。在充分考慮上述芯片特點和資源的基礎上,該卡采用DSP和FPGA取代單片機

2011-02-27 13:29:19 104

104 【摘要】本文論述了FPGA在DSP應用上的優缺點,比較了FPGA芯片和DSP芯片之間的差別,介紹了解決隔閡的方案--Xtreme DSP軟件包和平臺級的Virtex Ⅱ芯片。最后,對Xtreme和VirtexⅡ芯片的特點進行了詳細說明。 關鍵詞:數字信號處理;可編程門陣列;芯片

2011-02-28 13:09:41 59

59 System Generator 工具由 MathWorks 與 Xilinx 合作開發而成,DSP 設計人員可使用 MATLAB 和Simulink 工具在 FPGA 內進行開發和仿真來完善 DSP 設計。 該工具為系統級 DSP 設計與 FPGA 硬件實現的融合起

2011-05-11 18:36:23 224

224 為滿足導航系統設計的小型化、實時性要求,本文提出了一種基于FPGA + DSP 的實現方案。該方案的設計思路是:將FPGA 映射到DSP EMIF 的一段地址空間,并用FPGA 來完成多通道信號的采集; DSP 根

2011-09-13 14:32:08 77

77 該方案采用Altera公司的IP核和Cyclone系列FPGA,建立了串行RapidIO(SRIO)接口通信系統,并對其功能進行驗證。詳細分析了RapidIO應用系統及其驗證模型的功能結構和運行原理,為提高嵌入式

2011-12-23 14:47:22 38

38 介紹了RapidIo總線的特點,以及RapidIo總線初始化過程中面臨的系統網絡結構探測和最短路徑路由選擇問題。針對該問題,本文研究了深度優先(DFS)網絡拓撲探測方法在RapidIo總線枚舉過

2013-03-13 16:15:14 74

74 基于FPGA和DSP的圖像多功能卡的設計與實現

2016-09-22 12:32:08 28

28 DSP與FPGA高速的數據傳輸有三種常用接口方式: EMIF, HPI 和 McBSP 方式。而采用 EMIF 接口方式, 利用 FPGA ( 現場可編程邏輯門陣列) 設計 FIFO的接口電路,即可實現高速互聯。

2017-02-11 14:16:10 2487

2487

基于FPGA和DSP網絡單向時延測量系統設計與實現_唐旭

2017-03-19 11:38:26 0

0 基于FPGA的高速DSP與液晶模塊接口的實現

2017-10-19 13:46:23 3

3 基于DSP的FPGA配置方法研究與實現

2017-10-19 16:15:19 36

36 摘要 利用異步FIFO實現FPGA與DSP進行數據通信的方案。FPGA在寫時鐘的控制下將數據寫入FIFO,再與DSP進行握手后,DSP通過EMIFA接口將數據讀入。文中給出了異步FIFO的實現

2017-10-30 11:48:44 1

1 出于以下幾個原因,你可能會考慮使用FPGA來實現DSP解決方案。首先是為了提高性能,盡管今天的DSP處理器很快,并對許多DSP應用來說很有用,但仍有一些應用要求性能再進一步提升,而FPGA提供了更高

2017-11-06 11:47:52 0

0 結構,同時為滿足大數據存儲要求設計了可方便網絡控制的數據存儲模塊。模塊之間可以通過自定義LVDS接口實現互聯,組成一個系統。

2017-11-17 06:11:40 2373

2373

本文首先分析了FPGA是否會取代DSP,其次介紹了FPAG結構特點與優勢及DSP的基本結構和特征,最后闡述了FPGA與DSP兩者之間的區別。

2018-05-31 09:51:25 35711

35711

高性能 DSP 上的串行 RapidIO 接口

2018-06-12 03:44:00 3784

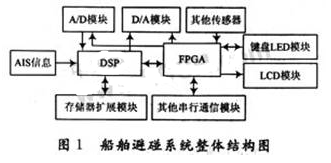

3784 的I/O功能,實現外圍輸入輸出接口如其他串行口、ADC數據采集緩存等硬件電路,使部分數據采集和數據通信的I/O任務由DSP和FPGA協同承擔,從而使DSP減輕負擔,可以更專注于避碰的復雜算法。FPGA還可以實現

2020-05-13 07:57:00 1705

1705

某魚雷聲自導的硬件系統使用了百兆網絡交換機實現DSP之間的互聯。交換機在MAC和PHY之間的接I=I是RMII,但DSP沒有相應的外圍設備與它匹配。因此必須在FPGA中設計RMII的通訊模塊,完成DSP數據格式向RMII數據格式的轉化。在設計中將該通訊模塊分為發送狀態機和接收狀態機兩部分

2018-10-18 16:46:51 64

64 通過分析網卡基本通信過程控制和數字信號處理器( DSP)對網卡直接編程方法, 成功設計基于DSP的網絡通程序,從而最終實現DSP系統數字化和網絡化的融合。

2020-08-14 15:55:00 7

7 RapidIO交換芯片是一種基于RapidIO協議的專用交換芯片,它能夠實現高速、低延遲的數據傳輸和交換,廣泛應用于嵌入式系統、數據中心、網絡通信等領域。RapidIO協議本身是一種基于包交換的互連技術,具有高速、高效、可靠等特點,因此RapidIO交換芯片在數據傳輸和交換方面具有很高的性能優勢。

2024-03-16 16:40:09 1532

1532

電子發燒友App

電子發燒友App

評論