隨著數字通信技術的飛速發展,軟件無線電的應用愈加的廣泛, 而影響軟件無線電性能的關鍵器件數控振蕩器NCO(Numerical CONtrolled Oscillator) 的設計至關重要直接數字頻率合成(DDS)技術是一種從相位概念出發直接合成所需要的波形的新的全數字頻率合成技術。同傳統的頻率合成技術相比,DDS 技術具有頻率精度高、轉換時間短、頻譜純度高以及頻率相位易編程、輸出的頻率穩定度與系統的時鐘穩定度相同等一系列優點, 廣泛應用于現代各種通信系統中,包括數字上下變頻、中頻變換、頻率合成以及擴頻系統和各種頻率相位數字調制解調系統中。

在軟件無線電及通信領域, 經常使用正交的數字信號;針對此類應用, 本文給出了一種基于FPGA 的正交NCO 設計方法,可以實現正交的、連續相位、高性能、高精度、可重利用的數控振蕩器,適合于多種應用場景的片上系統的設計。

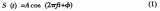

1 NCO 實現原理

直接數字頻率合成(DDS)技術是一種全數字技術,同傳統的頻率合成技術相比,DDS 技術具有多項優點: 頻率切換時間短、頻率分辨率高、相位變化連續、容易實現對輸出信號的多種調制等。

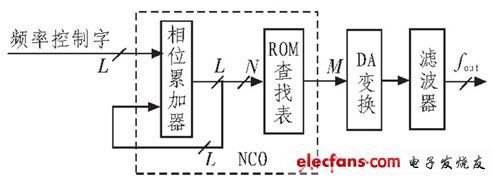

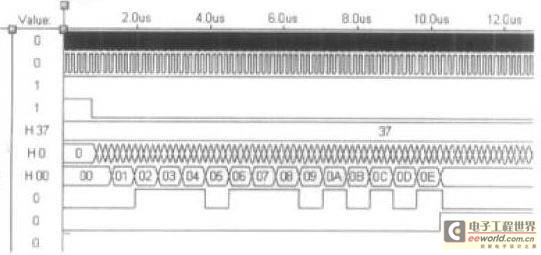

DDS 的原理框圖如圖1 所示, 其實質是以基準頻率源(系統時鐘)對相位進行等間隔的采樣。由圖1 可見,DDS 由相位累加器和波形存儲器(ROM 查詢表)構成的數控振蕩器(NCO)、數模轉換器(DAC)以及低通濾波器(LPF)3 部分組成。而DDS 的核心是NCO 的設計與實現,NCO 一般是由相位累加器和正余弦查找表兩部分組成,其中相位累加器的設計較簡單,故設計NCO 的關鍵是設計正、余弦函數發生器。

實現函數發生器的方法為查表法(LUT),對于一個相位位數為L,輸出信號幅度位數為M 的NCO,所需查找表的大小為M×2L。

?

圖1 DDS 基本原理框圖

在每一個時鐘周期,L 位相位累加器與其反饋值進行累加,其結果的高N 位作為ROM 查詢表的地址,然后從ROM中讀出相應的幅度值送到DAC。低通濾波器LPF 用于濾除DAC 輸出中的高次諧波。因此通過改變頻率控制字K 就可以改變輸出頻率fout。容易得到輸出頻率fout與頻率控制字K 的關系為:fout=Kfc /2L,其中fc為相位累加器的時鐘頻率,L 為相位累加器的位數。定義當K=1 為系統頻率分辨率,即f=fc /2L。

2 NCO 幾種常見設計方法

常見的NCO 實現的方法目前主要有計算法、CORDIC(Coordinated RotATIon Digital Computer)算法和查表法等。

計算法是一種以軟件編程的方式通過實時計算產生正弦波樣本, 該方法耗時多且只能產生頻率相對較低的正弦波,而需要產生高速的正交信號時,用此方法不能很好的滿足要求。

CORDIC 算法即坐標旋轉數字計算方法, 其基本思想是用一系列固定角度的不斷偏擺逼近所需旋轉的角度,實現包括乘除、平方根、三角函數、向量旋轉(即復數乘法) 以及指數運算,該算法往往需要通過乘法器和查找表才能實現多種超越函數的計算,這會導致硬件電路實現復雜、運算速度降低,此外它能夠計算的角度范圍也有限,故CORDIC 算法在實際使用時有較大的限制條件。

在實際應用中一般采用最有效、最簡單的查表法,即事先根據各個NCO 正弦波相位計算好相位的正弦值, 并以相位角度作為地址把該相位的正弦值數據存儲在表中,然后通過相位累加產生地址信息讀取當前時刻的相位值在表中對應的正弦值,從而產生所需頻率的正弦波;同時由于正余弦波形的對稱性,只需要存儲部分數據即可完成全相位的數值輸出。這種實現方法,設計簡單、運算速度較高,可以很好的滿足在數字變頻、擴頻、調制解調等多種場合的要求。

3 正交NCO 的查找表實現方法

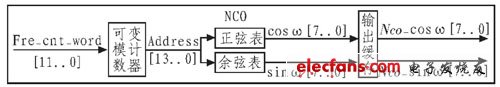

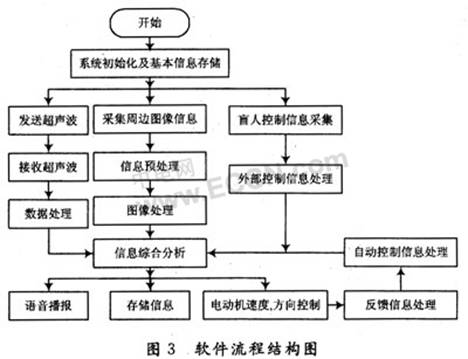

基于FPGA 的正交NCO 設計原理框圖如圖2 所示,主要由3 部分組成: 可變模計數器、正余弦查找表和輸出單元3個模塊組成。

?

圖2 NCO 的設計原理框圖

下面以輸入的頻率控制字為1 200 Hz 為例進行設計。

Fre_sample, 表示系統采用時鐘;Fre_cnt_word 表示頻率控制字。

1)可變模計數器的設計

可變模計數器是根據頻率控制字,計算出正余弦表的查表所需的地址;同時要保證產生的正余弦波的相位保持連續(有些應用場合常常要求輸出的相位連續),即置于相應的余數值。在第1 個工作時鐘周期讀入頻率控制字,第2 個工作時鐘周期內計算出mod(Fre_sample,Fre_cnt_word)作為相位控制字,第3 個工作時鐘周期內部計數器復位置入相位控制字,第4 個時鐘周期開始以頻率控制字為步長,相位控制字為初始值進行計數輸出。

2)正余弦查找表的設計

正余弦查找表是根據可變模計數器的輸出查表得到相應載頻波形的輸出。

基于FPGA 的NCO 設計的一個關鍵就是波形存儲器ROM 相位累加器的輸出地址作為ROM 的地址輸入,經查表和運算后,ROM 輸出正余弦波形的量化數據; 設計中主要是要節省存儲器資源的開銷,即減小ROM 存儲表的空間;由于存儲表的尺寸隨著地址位數或數據位數的增加呈現指數級遞增關系,所以在滿足頻率分辨率、信號性能的前提下,主要考慮較小ROM 存儲表的開銷;在實際的應用中,可以充分利用正余弦信號在一個周期內的對稱性來減少ROM 存儲表的開銷, 例如正弦信號, 在一個周期內對于X 軸是對稱的,基于此可以將ROM 存儲表減少至原來的1 /2, 再利用半周期內的左右對稱性,又可以將ROM 存儲表減少至原來的1 /2,因此通過一個正弦查找表的前1 /4 周期就可以變換得到整個正弦波周期查找表,這樣就節省了3 /4 的存儲器資源。

正余弦表的具體設計思想如下: 取頻率分辨率為df=1 Hz ; 假設頻率控制字為1 200 Hz 的頻率左右, 現考慮對1 200 Hz 的正余弦波形每一個周期采8 個樣點,則可得采樣率為fs =1 200×8=9 600 Hz.設對于每一個樣點值取8 bit 量化,則每個表格共需存儲9.6 kB;(如果考慮到正、余弦信號的對稱性,設計時可優化為上每個表格存儲1/4 個波形即可,即每個表格只需存儲2.4 kB;)使用時是用步長STep 來調節輸出頻率, 同時保證輸出的正余弦波的相位連續。如果每隔0樣點取1,即step=1,輸出頻率為1 Hz;每隔1 點取1,即step=2,輸出頻率為2 Hz;……;每隔1 199 點取1,step=1 200, 輸出頻率為1 200 Hz.

電子發燒友App

電子發燒友App

評論