基于FPGA的OFDM系統(tǒng)設計與實現(xiàn)

2012年05月25日 09:38 來源:互聯(lián)網(wǎng) 作者:秩名 我要評論(0)

近年來, 隨著數(shù)字信號處理(DSP) 和超大規(guī)模集成電路(VLSI) 技術的發(fā)展, 正交頻分復用OFDM(Orthogonal Frequency Division Multiplexing)技術的應用有了長足的進步和廣闊的發(fā)展前景。IEEE802.11a中就將正交頻分復用作為物理層的傳輸技術;歐盟在數(shù)字音頻廣播(DAB)、地面數(shù)字視頻廣播(DVB2T)、高清晰度電視(HDTV)以及2003年4月公布的無線城域網(wǎng)(WMAN)802.16a等研究中都使用了正交頻分復用技術作為信道的傳輸手段。在正交頻分復用技術逐漸成熟的今天, 如何降低通信系統(tǒng)的成本, 使之更廣泛地應用于數(shù)傳系統(tǒng)中, 已成為正交頻分復用研究的熱點。本文基于802.16a協(xié)議的原理架構,本著小成本、高效率的設計思想,建立了一個基于FPGA的可實現(xiàn)流水化運行的OFDM系統(tǒng)的硬件平臺,包括模擬前端及OFDM調(diào)制器及OFDM 解調(diào)器,用來實現(xiàn)OFDM的遠距離無線傳輸系統(tǒng)。

1 模擬前端

模擬前端主要包括發(fā)送端DA模塊、接收端AD模塊和射頻模塊。

發(fā)送端DA模塊主要由XILINX公司的FPGA-XC2V1000芯片和數(shù)模轉(zhuǎn)換芯片AD9765、濾波器和放大器構成,基帶處理調(diào)制后數(shù)據(jù)在控制時鐘同步下送入FPGA進行降峰均比等算法的處理,然后經(jīng)過交織將其送入AD9765進行數(shù)模轉(zhuǎn)換并上變頻到70MHz,輸出的模擬信號再經(jīng)聲表濾波器后放大進入下一級射頻模塊。發(fā)送端DA模塊硬件結構框圖如圖1所示。

接收端AD模塊主要由增益放大器、帶通濾波、采樣芯片AD9238和數(shù)字下變頻器GC1012構成。AD模塊的主要功能是完成中頻信號的采樣和數(shù)字下變頻,在FPGA XC2V1000中完成符號同步算法,其輸出送OFDM解調(diào)器。接收端AD模塊硬件結構框圖如圖2所示。

射頻模塊工作在70MHz中頻上,射頻模塊的功能是將完成調(diào)制的中頻信號搬移到射頻波段上,或者將空中的接收信號下變頻到模擬前端所需的中頻波段上。

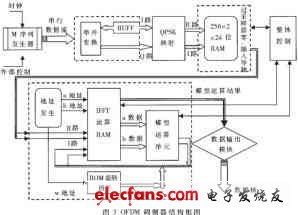

2 OFDM 調(diào)制器實現(xiàn)架構

在OFDM系統(tǒng)中,OFDM調(diào)制器主要完成OFDM數(shù)據(jù)的調(diào)制。圖3為OFDM調(diào)制器的結構框圖。OFDM的調(diào)制器采用N=120個數(shù)據(jù)子信道,8個導頻信道。120個數(shù)據(jù)子信道都采用 QPSK的信道調(diào)制,8個導頻信道采用BPSK的信道調(diào)制。為了使用基帶傳輸,進行添零處理(添加128個0),使頻帶擴展1倍。經(jīng)過逆序處理后,采用256點的IFFT進行 OFDM調(diào)制。系統(tǒng)時鐘為80MHz,用 FPGA 完成數(shù)據(jù)的編碼和調(diào)制,最后以讀時鐘為500kHz的速率送往 D/A。

在FPGA中,按照具體的參數(shù)要求實現(xiàn)了OFDM系統(tǒng)中的調(diào)制功能,其工作流程為:數(shù)據(jù)發(fā)生器(M序列產(chǎn)生器)發(fā)送數(shù)據(jù),串并轉(zhuǎn)換后存儲在 256×2位的RAM_in中,當接收夠一幀數(shù)據(jù)所需要的信息量后,從RAM_in中讀取數(shù)據(jù)進行QPSK映射、過采樣添零,隨后插入導頻模塊。與此同時,IFFT模塊接收QPSK映射、過采樣添零和插入導頻模塊發(fā)送出的數(shù)據(jù);當 QPSK、添零、共軛模塊處理完1個數(shù)據(jù)包的數(shù)據(jù)后,IFFT 模塊開始計算,進行OFDM的IFFT調(diào)制,經(jīng)IFFT 模塊計算后的數(shù)據(jù)輪換存入RAM_ou1或者RAM_ou2;控制模塊發(fā)出使能信號,先從數(shù)據(jù)輸出模塊中讀取同步頭發(fā)送,同步頭發(fā)送完成后,再從RAM_ou1或者RAM_ou2中讀取循環(huán)前綴和數(shù)據(jù)塊;當 IFFT 模塊計算完的數(shù)據(jù)全部送出后,控制模塊判斷開始處理下一包數(shù)據(jù),處理到第10包數(shù)據(jù),則通知外部控制器一幀數(shù)據(jù)處理完成。[next]

3 OFDM 解調(diào)器實現(xiàn)架構

在OFDM系統(tǒng)中,解調(diào)器主要是對接收 A/D 采樣來的數(shù)據(jù)進行解調(diào)。圖4為OFDM解調(diào)器的結構框圖。

在FPGA中,按照參數(shù)要求實現(xiàn):將從A/D以500kHz的速率采樣來的數(shù)據(jù)存入 RAM 當中,當接收到第64個幀頭數(shù)據(jù)時,開始計算局部自相關函數(shù);每接收到一個幀頭數(shù)據(jù),取出8位(最高位無效,剩余7位為巴克碼),計算一次x(i)*x(i+j),并存儲、判斷,是否有相關最大值,如果有,則判斷計數(shù)器加1,在一個幀頭短前導字部分中,共有10個短前導字片,每一片為64個采樣點;當接收到第640個數(shù)據(jù)后,判斷累加器是否超過了門限值640×3,如果累加門限值達到1920,則認為有幀到達,整體控制模塊產(chǎn)生使能信號,表示粗同步結束,準備接受長前導字,進行細同步和頻偏估計計算,否則,將累加計數(shù)器清零,重新開始接受幀頭;幀到達檢測和幀同步過程完成后,再將接收到的數(shù)據(jù)存入到解幀模塊的數(shù)據(jù)RAM中;當數(shù)據(jù)RAM中存滿256點的數(shù)據(jù)后,整體控制模塊發(fā)出讀使能信號、解幀使能信號和FFT的START信號,從RAM中讀取數(shù)據(jù),送往FFT 進行OFDM的解調(diào);然后去除循環(huán)前綴,去除添加的零和導頻信息;最后經(jīng)過QPSK的反映射和并串轉(zhuǎn)換后,還原成原始數(shù)據(jù)讀出,并等下一幀數(shù)據(jù)的接收。

本文導航

- 第 1 頁:基于FPGA的OFDM系統(tǒng)設計與實現(xiàn)(1)

- 第 2 頁:系統(tǒng)調(diào)試與性能分析

上周熱點文章排行榜

上周資料下載排行榜

論壇熱帖

熱門博文

創(chuàng)新實用技術專題

熱評

- LM3S9B96開發(fā)板手冊及原理圖

- STM32F103ZET6紅牛電路圖

- 高通發(fā)布全新設計DragonBoard板

- NI推出Single-Board RIO嵌入式介面

- protel99se正式漢化版免費下載

- hi3515海思原版原理圖

- matlab 7.0軟件下載(免費破解版)

- TX-1C型單片機開發(fā)板原理圖

- 三菱A500變頻器原理圖

- 三相IGBT全橋隔離驅(qū)動電源設計

博文

- 問什么郵箱激活不了

- 八成大學生認同先就業(yè)后擇業(yè)

- 我的心路

- 為什么郵箱激活不了

- 你是否曾這樣傷害過一個人?

- 2012.5.12 第一個DS18B20程序

- 到底有多少人在校園里浪費青春

- 到底有多少人在校園里浪費青春

- 藍牙技術越來越雞肋

- 【博客分享季】 我的單片機入門

用戶評論

查看全部 條評論

查看全部 條評論>>