電子發(fā)燒友網(wǎng)核心提示:對初級FPGA工程師而言,必須掌握FPGA相關(guān)基礎(chǔ)知識、精通硬件描述語言、熟練數(shù)字電路設(shè)計、加強(qiáng)工程項目的實(shí)踐。應(yīng)廣大初級FPGA工程師/FPGA愛好者之需,電子發(fā)燒友網(wǎng)策劃整合并隆重推出《FPGA核心基礎(chǔ)知識詳解》系列技術(shù)文章,以后會陸續(xù)推出其他章節(jié),敬請廣大工程師朋友繼續(xù)關(guān)注和留意。

一、FPGA基礎(chǔ)知識

1. 什么是 FPGA?

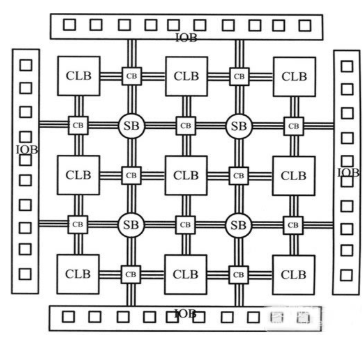

現(xiàn)場可編程門陣列 (FPGA) 是由通過可編程互連連接的可配置邏輯塊 (CLB) 矩陣構(gòu)成的可編程半導(dǎo)體器件。相對于專為特定設(shè)計定制構(gòu)建的專用集成電路 (ASIC) 而言,F(xiàn)PGA 能通過編程來滿足應(yīng)用和功能要求。

雖然市面上也有一次性可編程 (OTP) FPGA,但絕大多數(shù)是基于 SRAM 的類型,可隨著設(shè)計的演化進(jìn)行重編程。

請參考下面的內(nèi)容來具體了解方框圖中的各個突出顯示區(qū)域。

圖1.1 FPGA單元結(jié)構(gòu)

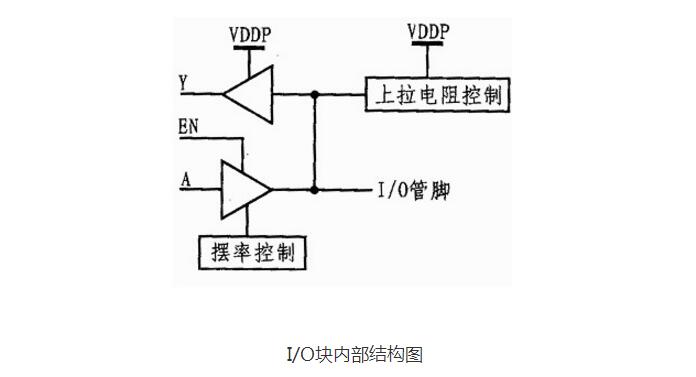

(1)IOB 細(xì)節(jié)

目前的 FPGA 可支持許多種 I/O 標(biāo)準(zhǔn),因而為您的系統(tǒng)提供了理想的接口橋接。FPGA 內(nèi)的 I/O 按 bank 分組 (見下圖) ,每個 bank 能獨(dú)立支持不同的 I/O 標(biāo)準(zhǔn)。 目前最先進(jìn)的 FPGA 提供了十多個 I/O bank,能夠提供靈活的 I/O 支持。

圖1.2 FPGA內(nèi)的 I/O 按bank分組圖示

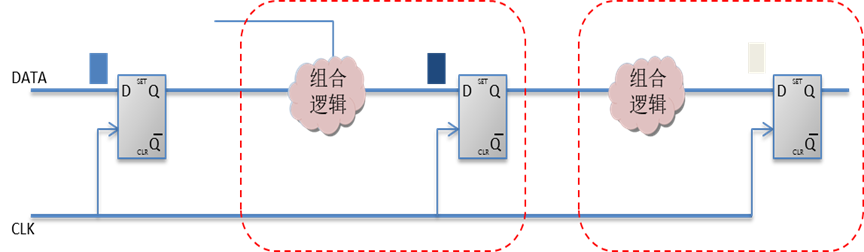

(2)CLB 細(xì)節(jié)

可配置邏輯塊是 FPGA 的基本邏輯單元。實(shí)際數(shù)量和特性會依器件的不同而改變,但是每個 CLB 都包含一個由 4 或 6 個輸入、一些選擇電路(多路復(fù)用器等)和觸發(fā)器組成的可配置開關(guān)矩陣。開關(guān)矩陣具有高度的靈活性,經(jīng)配置可以處理組合型邏輯、移位寄存器或 RAM。

圖1.3高層次的 CLB 簡介

(3)DCM 細(xì)節(jié)

業(yè)界大多數(shù) FPGA 均提供數(shù)字時鐘管理(Xilinx 所有 FPGA 均具有此特性),幾乎消除了過去設(shè)計者在將全局信號設(shè)計到 FPGA 中時不得不面對的歪斜及其它問題。

(4)FPGA 的常見特性

當(dāng)今的 FPGA 已經(jīng)遠(yuǎn)遠(yuǎn)超出了先前版本的基本性能,并且整合了如 RAM、時鐘管理和 DSP 這些常用功能的硬(ASIC 型)塊。 FPGA 的基本組件如下。

a.可配置邏輯塊 (CLB)

CLB 是 FPGA 的基本邏輯單元。實(shí)際數(shù)量和特性會依器件的不同而改變,但是每個 CLB 都包含一個由 4 或 6 個輸入、一些選擇電路(多路復(fù)用器等)和觸發(fā)器組成的可配置開關(guān)矩陣。開關(guān)矩陣具有高度的靈活性,經(jīng)配置可以處理組合型邏輯、移位寄存器或 RAM。

b.互連

CLB 提供了邏輯性能,靈活的互連布線則負(fù)責(zé)在 CLB 和 I/O 之間傳遞信號。布線有幾種類型,從設(shè)計用于專門實(shí)現(xiàn) CLB 互連、到器件內(nèi)的高速水平和垂直長線、再到時鐘與其它全局信號的全局低歪斜布線。除非另行說明,否則設(shè)計軟件會將互連布線任務(wù)隱藏起來,用戶根本看不到,從而大幅降低了設(shè)計復(fù)雜性。

c.SelectIO (IOB)

目前的 FPGA 可支持許多種 I/O 標(biāo)準(zhǔn),因而為您的系統(tǒng)提供了理想的接口橋接。FPGA 內(nèi)的 I/O 按 bank 分組 (見下圖) ,每個 bank 能獨(dú)立支持不同的 I/O 標(biāo)準(zhǔn)。目前最先進(jìn)的 FPGA 提供了十多個 I/O bank,能夠提供靈活的 I/O 支持。

d.存儲器

大多數(shù) FPGA 中都提供嵌入式塊 RAM 存儲器,這樣可以在您的設(shè)計中實(shí)現(xiàn)片上存儲。這些能為您的設(shè)計實(shí)現(xiàn)片上存儲。Xilinx FPGA 提供高達(dá) 10 Mbits 的片上存儲 (每個區(qū)塊大小為 36 Kbits),能夠支持真正的雙端口運(yùn)行。

e.完整的時鐘管理

業(yè)界大多數(shù) FPGA 都提供數(shù)字時鐘管理(所有 Xilinx FPGA 都具有此特性)Xilinx 推出的最高級 FPGA 提供了數(shù)字時鐘管理和鎖相環(huán)鎖定功能,不僅提供了精確時鐘綜合功能,而且能夠降低抖動和實(shí)現(xiàn)過濾。

(5)FPGA解決方案、應(yīng)用以及終端市場

由于其自身的可編程特性, FPGA 成為了眾多不同的市場的理想選擇。Xilinx 作為業(yè)界領(lǐng)先公司提供了包含 FPGA 器件、高級軟件和可配置即用型 IP 核等在內(nèi)的全套解決方案,可滿足以下市場和應(yīng)用的需求:

a.應(yīng)用方案

航空航天和軍用產(chǎn)品:用于實(shí)現(xiàn)圖形處理、波形生成和 SDR 部分重配置的抗輻射 FPGA 與 IP 核。

汽車:用于實(shí)現(xiàn)網(wǎng)關(guān)與駕駛員輔助系統(tǒng)、舒適性、便捷性、車載信息娛樂的汽車芯片和 IP 解決方案。

廣播:在視頻和音頻被廣泛采用(從演播室到生產(chǎn)與傳輸,再到消費(fèi)類)的同時,該解決方案也實(shí)現(xiàn)了一系列廣播鏈任務(wù)。

消費(fèi)類:高性價比解決方案支持新一代功能齊全的消費(fèi)類應(yīng)用,如整合式手持設(shè)備、數(shù)字平板顯示器、信息家電、家庭網(wǎng)絡(luò)和住宅機(jī)頂盒等。

工業(yè)/科學(xué)/醫(yī)療:工業(yè)解決方案可以解決工業(yè)自動化、電機(jī)控制和高端醫(yī)療成像領(lǐng)域中的特殊市場需求和挑戰(zhàn)。

存儲與服務(wù)器:針對網(wǎng)絡(luò)附加存儲(NAS)、存儲局域網(wǎng)(SAN)、服務(wù)器、存儲設(shè)備等的數(shù)據(jù)處理解決方案。

無線通信:針對無線設(shè)備的RF、基帶、連接、傳輸和網(wǎng)絡(luò)解決方案,可支持 WCDMA、HSDPA、WiMAX等標(biāo)準(zhǔn)。

有線通信:針對可編程網(wǎng)絡(luò)線卡包處理、成幀器/MAC、串行背板以及更多其它應(yīng)用的端對端解決方案

b.技術(shù)解決方案

DSP:Xilinx XtremeDSP? 計劃可幫助您開發(fā)出高性能定制 DSP 解決方案,以滿足航空航天和軍用產(chǎn)品、數(shù)字通信、多媒體、視頻以及成像等行業(yè)需求

嵌入式處理:Xilinx 針對您獨(dú)特的餓嵌入式應(yīng)用提供了一系列高度靈活的創(chuàng)新型處理解決方案。

二、FPGA與ASIC

1.ASIC 和 FPGA 的優(yōu)劣勢分析

ASIC 和 FPGA 具有不同的價值主張,在作出選擇前必須仔細(xì)評估。兩種種技術(shù)對比。這里介紹了 ASIC 和 FPGA 的優(yōu)勢與劣勢:

a.FPGA 的設(shè)計優(yōu)勢

更快的上市時間——無需布局、掩模和其它制造步驟;

無前期 NRE(非重發(fā)性設(shè)計成本)—— 與 ASIC 設(shè)計有關(guān)的成本;

縮短了設(shè)計周期——由于軟件可以處理很多布線、布局和時序問題;

更加可預(yù)測的項目周期——由于消除了可能的重置、晶圓容量等階段;

現(xiàn)場可重編程能力——可以遠(yuǎn)程上傳的新比特流。

b.ASIC 的設(shè)計優(yōu)勢

全定制性能——實(shí)現(xiàn)設(shè)計,因為器件根據(jù)設(shè)計規(guī)范進(jìn)行生產(chǎn);

降低單位成本——用于實(shí)現(xiàn)大批量設(shè)計;

小型化——因為器件根據(jù)設(shè)計規(guī)范進(jìn)行生產(chǎn);

較高的原始內(nèi)部時鐘速度。

過去 FPGA 用于速度/復(fù)雜度/容量較低的設(shè)計,而當(dāng)今的 FPGA 則可以輕松突破 500 MHz 的性能障礙。FPGA 能夠以更低的價格實(shí)現(xiàn)無可比擬的邏輯密度增加和眾多其它特性(如嵌入式處理器、DSP 模塊、時鐘技術(shù)和高速串行),現(xiàn)已幾乎成為任何設(shè)計的首選。

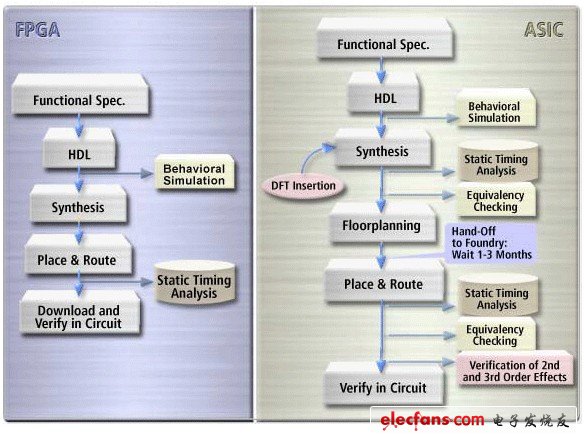

2.FPGA 和ASIC 的設(shè)計流程對比

圖2.1 FPGA與ASIC的設(shè)計流程對比

由于設(shè)計邏輯已綜合到通過驗證的定義好的 FPGA 器件上,這樣 FPGA 設(shè)計流程就避免了項目中既復(fù)雜又耗時的平面規(guī)劃、布局布線、時間分析以及掩碼/項目階段。

然而,必要時,Xilinx 還能夠提供先進(jìn)的布局規(guī)劃、層次化設(shè)計和時序工具,使用戶能夠?qū)⒁笞羁量痰脑O(shè)計的性能最大化

三、CPLD基礎(chǔ)知識

1.CPLD 是什么?

CPLD 由完全可編程與/或陣列以及宏單元庫構(gòu)成。 與/或陣列可重編程,能夠執(zhí)行眾多邏輯功能。宏單元是執(zhí)行組合邏輯或時序邏輯的功能塊,同時還提供了真值或補(bǔ)碼輸出和以不同的路徑反饋等更高靈活性。

傳統(tǒng)上, CPLD 采用模擬傳感放大器來提高架構(gòu)性能。This performance boost came at the cost of very high current requirements. Xilinx推出的CoolRunner?-II CPLD 采用創(chuàng)新型全數(shù)字內(nèi)核,能夠以極低的功耗達(dá)到同樣的性能水平。 這樣,設(shè)計人員能夠采用同一CPLD 架構(gòu)實(shí)現(xiàn)高性能和低功耗兩種不同設(shè)計。避免采用模擬傳感放大器還使架構(gòu)具有可擴(kuò)展能力,這樣隨著工藝技術(shù)一代一代的進(jìn)步,不僅大幅降低了成本,而且還實(shí)現(xiàn)了特性增強(qiáng)。

2.為何選用CPLD?

由于其具有獨(dú)特的功能,CPLD 在系統(tǒng)設(shè)計中可完成多種有用的功能

(1)可重編程

可根據(jù)需要,立即、隨意修改設(shè)計,且不會帶來任何成本,能構(gòu)建可重配置系統(tǒng),修正ASIC錯誤,隨時隨地升級系統(tǒng)功能,從而節(jié)約時間,降低成本,簡化設(shè)計。

(2)簡單易用

利用 CPLD 進(jìn)行設(shè)計即簡單又容易,可輕松適應(yīng)已有的設(shè)計流程;節(jié)約時間,降低成本并簡化設(shè)計。

(3)低成本

不僅可通過重編程來修正系統(tǒng)錯誤,降低單位成本,而且還可取代 TTL 和 ASSP 解決方案,減少電路板組件數(shù)量并提高可靠性;從而降低了設(shè)計成本、系統(tǒng)成本和維護(hù)成本。

(4)非易失性

斷電模式下也能編程,當(dāng)系統(tǒng)上電時 CPLD 功能立即可用,存儲的設(shè)計內(nèi)容幾乎不可能被竊取;提高安全性,簡化了設(shè)計。

3.為何選用Xilinx CPLD?

做為可編程邏輯解決方案的市場領(lǐng)頭羊,Xilinx提供完整的解決方案來滿足設(shè)計人員的 CPLD 需求:

(1)高級芯片

成本優(yōu)化的芯片設(shè)計、高性能、低功耗運(yùn)行、最大范圍的封裝選擇、高級系統(tǒng)特性,每個宏單元 I/O 數(shù)量最多。

(2)功能強(qiáng)大的免費(fèi)設(shè)計工具

ISE WebPACK 設(shè)計工具提供了用于開發(fā)所有 Xilinx CPLD 產(chǎn)品的最完善、簡便易用的桌面軟件解決方案。

(3)各種其他支持

免費(fèi)的參考設(shè)計和應(yīng)用手冊,可立即著手設(shè)計的完整設(shè)計套件, 龐大的分銷商網(wǎng)絡(luò)、銷售代表、現(xiàn)場應(yīng)用工程師和內(nèi)部技術(shù)支持網(wǎng)絡(luò),以及大量的在線技術(shù)文檔。

四、利用CPLD進(jìn)行設(shè)計

1.Xilinx CPLD 帶來了極大的設(shè)計優(yōu)勢

了解 CPLD 使用的特性與優(yōu)勢, 有助于簡化設(shè)計、降低開發(fā)成本并加速產(chǎn)品上市進(jìn)程。CPLD 優(yōu)勢概覽:簡化設(shè)計;降低開發(fā)成本;實(shí)現(xiàn)產(chǎn)品創(chuàng)收增長;縮小板級空間;提高系統(tǒng)可靠性;加速產(chǎn)品上市進(jìn)程 。

2.利用CPLD 進(jìn)行設(shè)計的4 個簡單步驟

第 1 步:選擇 CPLD 器件

在為設(shè)計選擇合適的 CPLD 的過程中,需要考慮以下幾個方面(其優(yōu)先次序依設(shè)計的不同而不同):

(1)密度與 I/O

通過將您的設(shè)計提交到免費(fèi)下載的 ISE? WebPACK? 軟件,您可確定您的設(shè)計所需要的 Xilinx CPLD 的規(guī)模(邏輯密度和 I/O)。

(2)性能

Xilinx CPLD 有多種速度級別,因此您只需購買您所需性能的 CPLD 器件。利用 ISE WebPACK 確定器件的速度級別以滿足您系統(tǒng)的時序要求。

(3)電壓和功耗

不同的 Xilinx CPLD 系列具有不同的電壓(電源和 I/O)和功耗(靜態(tài)和動態(tài))要求。

(4)封裝

Xilinx CPLD 采用廉價的 QFP 封裝、超小型芯片級封裝, 以及 I/O 數(shù)量較多的 BGA 封裝等多種封裝形式。

(5)Xilinx CPLD 系列

a.CoolRunner? Series

Xilinx CoolRunner 系列 CPLD 是業(yè)界功耗最低、性能最高 的器件。 這些 CPLD 提供了諸如 I/O banking 、高級時鐘控制,以及出色的設(shè)計安全性等高級功能來支持系統(tǒng)級設(shè)計。

b.XC9500 系列

提供 5.0V (XC9500 系列) 和 3.3V (XC9500XL 系列) 版本,這些低成本 CPLD 系列產(chǎn)品提供了當(dāng)今尖端系統(tǒng)設(shè)計所需的高性能、豐富特性集和 靈活性 。

第 2 步:選擇軟件包

(1)CPLD 和簡單的 FGPA 設(shè)計

要實(shí)現(xiàn)基本的 CPLD 或 FPGA 設(shè)計,您需要下載免費(fèi)的ISE WebPACK 軟件工具。

(2)任何 CPLD/ FPGA 設(shè)計

除了 ISE WebPACK 軟件工具外,Xilinx 還提供了多種軟件包,以滿足不同的設(shè)計要求點(diǎn)擊這里來確定最適合您的設(shè)計需求的軟件包。

第 3 步:實(shí)現(xiàn)設(shè)計

選好 CPLD 器件并下載了必要的軟件后,下一步就是設(shè)計的實(shí)現(xiàn)。設(shè)計實(shí)現(xiàn)包括:設(shè)計實(shí)現(xiàn)包括:

(1)設(shè)計輸入

(2)對原型進(jìn)行編程和測試

(3)技術(shù)文檔

每個 CPLD 產(chǎn)品頁面都提供了應(yīng)用指南、參考設(shè)計、開發(fā)板、配置工具及其它有用信息的鏈接,可幫助設(shè)計人員快速、輕松地完成設(shè)計。

第 4 步:購買 CPLD

有幾種購買 Xilinx 解決方案的方法:Xilinx網(wǎng)上商城Xilinx分銷商

這兩種渠道都提供芯片、軟件、編程硬件及其它產(chǎn)品和資源。Xilinx 銷售辦事處和客戶 支持中心可以保證使用 Xilinx CPLD 是一次簡單而令人滿意的體驗。

電子發(fā)燒友App

電子發(fā)燒友App

評論