本文首先會(huì)對(duì)這個(gè)問題進(jìn)行一般性地分析,在此基礎(chǔ)上我們將以德州儀器公司 10G SERDES 器件 TLK10002 為例,提出一個(gè)新的解決方案,即采用雙時(shí)鐘模式提供 SERDES系統(tǒng)時(shí)鐘,并且探討

2013-09-26 14:34:31 3258

3258

不夠的情況下有可能會(huì)造成 FIFO 的溢出。本文首先會(huì)對(duì)這個(gè)問題進(jìn)行一般性地分析,在此基礎(chǔ)上我們將以德州儀器公司 10G SERDES 器件 TLK10002 為例,提出一個(gè)新的解決方案,即采用雙時(shí)鐘模式提供 SERDES系統(tǒng)時(shí)鐘。

2013-09-29 10:05:45 2100

2100

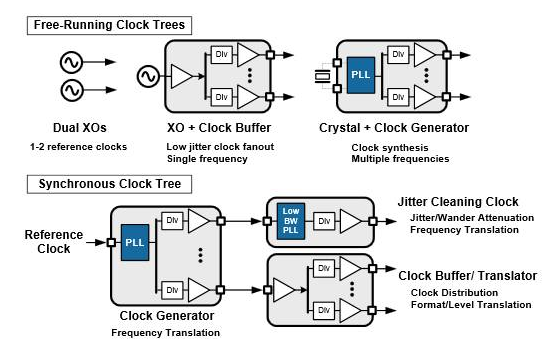

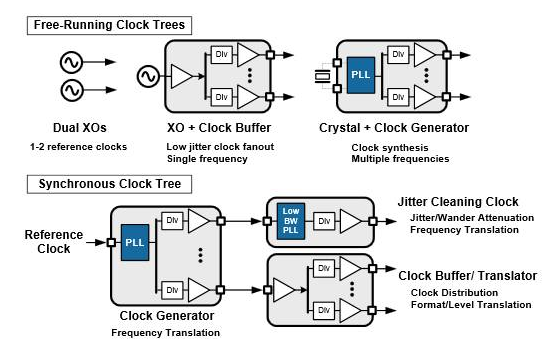

在高性能應(yīng)用中,例如通信、無線基礎(chǔ)設(shè)施、服務(wù)器、廣播視頻以及測(cè)試和測(cè)量裝置,當(dāng)系統(tǒng)集成更多功能并需要提高性能水平時(shí),硬件設(shè)計(jì)就變得日益復(fù)雜,為系統(tǒng)提供參考時(shí)序的板級(jí)時(shí)鐘樹也走向這種趨勢(shì)。在進(jìn)行時(shí)鐘

2017-10-31 09:45:13 5550

5550

GMII、SGMII和SerDes的區(qū)別和聯(lián)系? GMII和SGMII區(qū)別,上一篇已經(jīng)介紹了,這一篇重點(diǎn)介紹SGMII和SerDes區(qū)別。 GMII和SGMII SGMII接口 SGMII

2020-10-09 11:31:29 29959

29959

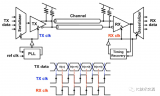

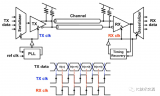

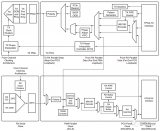

SerDes是串化(Serializer)和解串(Deserializer)的簡(jiǎn)稱,下圖給出了PHY的簡(jiǎn)圖。發(fā)送端發(fā)送并行數(shù)據(jù),時(shí)鐘由ref_clk經(jīng)過PLL鎖相環(huán)振出的時(shí)鐘提供,經(jīng)過差分對(duì)信號(hào)傳輸至接收端,通過CDR恢復(fù)時(shí)鐘并解串?dāng)?shù)據(jù)。

2023-08-16 17:19:23 2740

2740

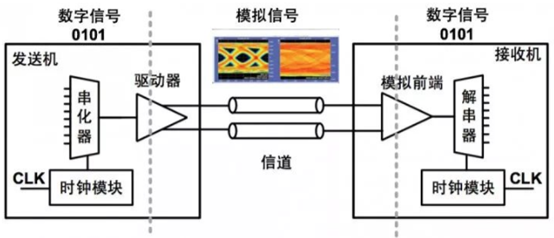

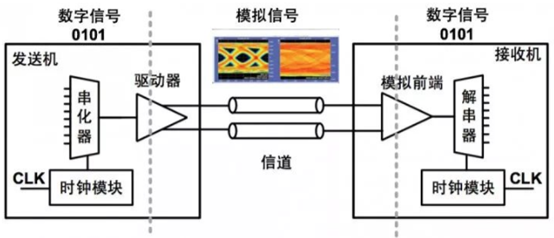

SerDes是SERializer(串行器)/DESerializer(解串器)的簡(jiǎn)稱,是一種主流的時(shí)分多路復(fù)用(TDM)、點(diǎn)對(duì)點(diǎn)(P2P)的串行通信技術(shù)。

2023-11-14 09:32:39 2479

2479

SERDES是英文SERializer(串行器)/DESerializer(解串器)的簡(jiǎn)稱。

2024-01-04 09:04:02 495

495

親愛的Xilinx論壇,我正在實(shí)現(xiàn)基于SERDES協(xié)議的序列化傳輸。我需要在Kintex7上接收8個(gè)差分對(duì),這些差分對(duì)承載由另一個(gè)Kintex7串行化的64位字,主時(shí)鐘為100MHz。將托管FPGA

2020-03-17 09:53:11

/10b的SerDes接口,包括SERDES收發(fā)單元,通過完全數(shù)字化的方法實(shí)現(xiàn)SERDES的CDR(Clock Data Recovery,時(shí)鐘數(shù)據(jù)恢復(fù)),完成100~200Mhz的板間SERDES單通道

2019-05-29 17:52:03

用戶在產(chǎn)品選型和方案設(shè)計(jì)之初,對(duì)于硬件接口資源分配不熟悉,不遵守芯片規(guī)范使用導(dǎo)致項(xiàng)目出現(xiàn)問題,造成了嚴(yán)重?fù)p失。本期我們就此系列平臺(tái)的SerDes資源分配做一篇文章。LS系列產(chǎn)品的資源不可為不豐富,其中最讓人頭暈的當(dāng)屬于SerDes協(xié)議。百度百科這樣解釋,SERDES是英文SERializer(串行器)/DE

2021-12-20 06:01:37

到Serial RIO,…等等,都是在借助SerDes來提高性能。SerDes是非常復(fù)雜的數(shù)模混合設(shè)計(jì),用戶手冊(cè)的內(nèi)容只是描述了森林里面的一棵小樹,并不能夠解釋SerDes是怎么工作的。SerDes怎么...

2021-07-28 07:02:12

SerDes的發(fā)送端TX的均衡原理是什么?怎樣利用高速接口SerDes去實(shí)現(xiàn)芯片間信號(hào)的有線傳輸?

2021-06-17 07:15:16

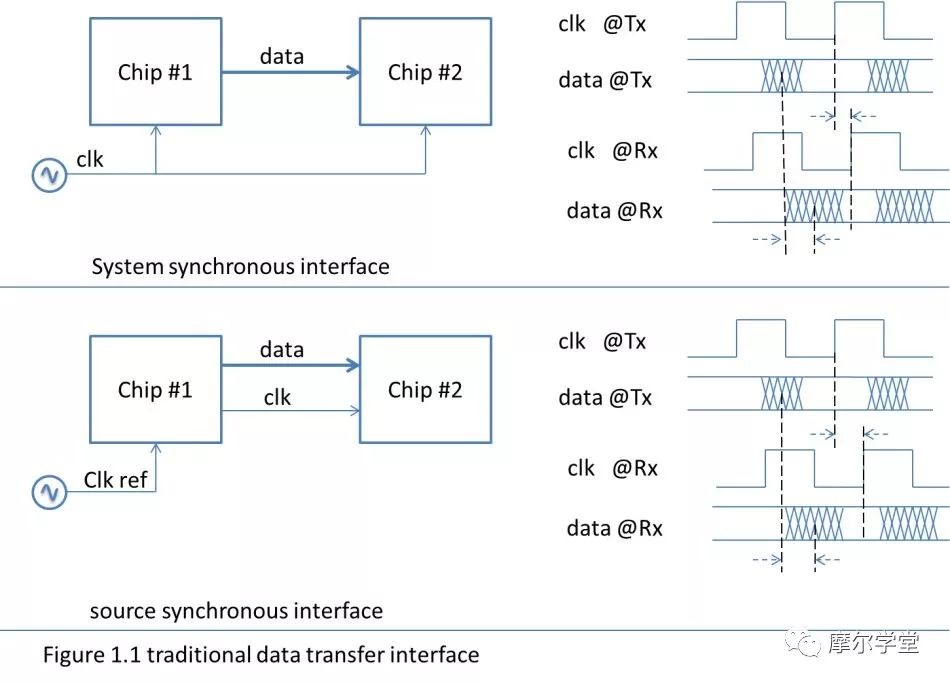

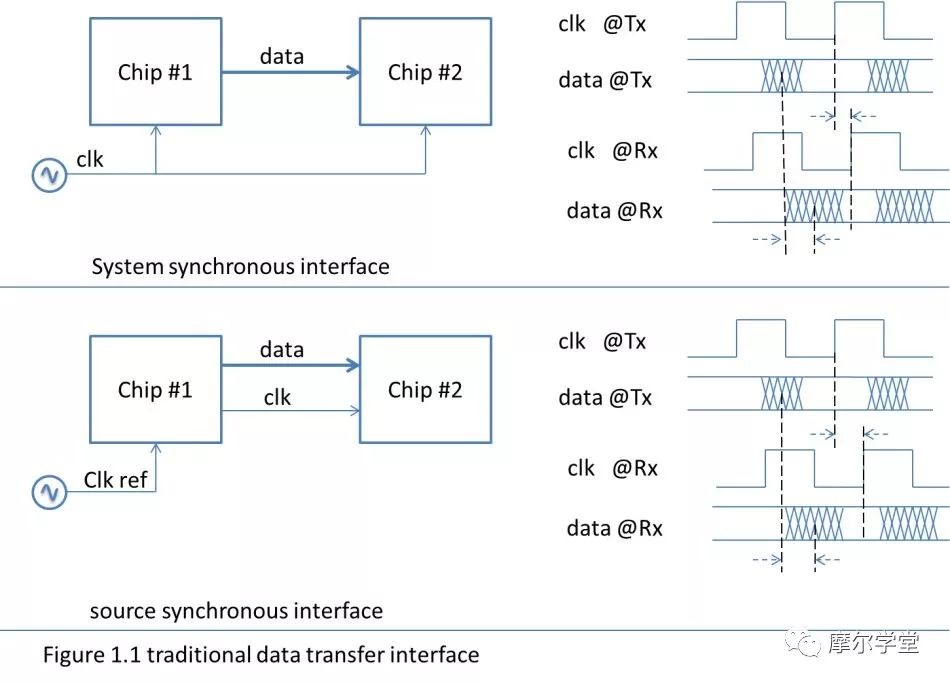

一、SERDES的作用1.1并行總線接口在SerDes流行之前,芯片之間的互聯(lián)通過系統(tǒng)同步或者源同步的并行接口傳輸數(shù)據(jù),圖1.1演示了系統(tǒng)和源同步并行接口。隨著接口頻率的提高,在系統(tǒng)同步接口方式中

2021-07-26 07:33:44

一、SERDES的作用1.1并行總線接口在SerDes流行之前,芯片之間的互聯(lián)通過系統(tǒng)同步或者源同步的并行接口傳輸數(shù)據(jù),圖1.1演示了系統(tǒng)和源同步并行接口。隨著接口頻率的提高,在系統(tǒng)同步接口方式中,有幾個(gè)因素限制了有效數(shù)據(jù)窗口寬度的繼續(xù)增加。a)、時(shí)鐘...

2021-07-28 08:35:42

我想用serdes ip模擬圖書館的位置在哪里?

2020-05-20 15:05:17

對(duì)高速信號(hào)進(jìn)行高分辨率的數(shù)字化處理需審慎選擇時(shí)鐘,才不至于使其影響模數(shù)轉(zhuǎn)換器(ADC)的性能。那么時(shí)鐘抖動(dòng)會(huì)對(duì)高速ADC的性能有什么影響呢?

2021-04-08 06:00:04

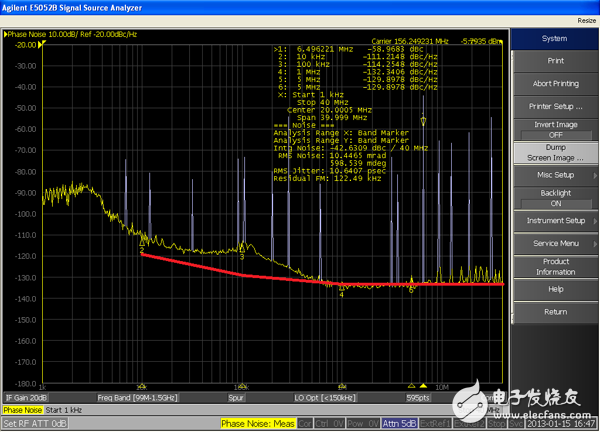

在本文中,我們將討論抖動(dòng)傳遞及其性能,以及相位噪聲測(cè)量技術(shù)的局限性。 時(shí)鐘抖動(dòng)和邊沿速率 圖1顯示了由一個(gè)通用公式表述的三種波形。該公式包括相位噪聲項(xiàng)“φ(t)”和幅度噪聲項(xiàng)“λ(t)。對(duì)評(píng)估的三個(gè)

2022-11-23 07:59:49

時(shí)鐘相噪對(duì)ADC性能的影響是什么?鎖相環(huán)的基本原理和相噪優(yōu)化方式

2021-04-07 06:25:40

如題,9176DAC的PLL鎖上了,證明時(shí)鐘應(yīng)該沒問題,但是為什么DLL和serdes PLL鎖不上呢?配置順序,我是按照手冊(cè)的START-UP SEQUENCE進(jìn)行配置的。

2023-12-01 06:54:09

串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨(dú)立

2019-10-23 07:16:35

SerDes在93000平臺(tái)上量產(chǎn)測(cè)試。本文將介紹Nautilus UDI方案是如何實(shí)現(xiàn)高速SerDes測(cè)試的,包括UDI結(jié)構(gòu),輸入時(shí)鐘設(shè)計(jì),Load board設(shè)計(jì),socket選型等多個(gè)測(cè)試環(huán)節(jié)。

2021-05-10 06:58:55

STM32系統(tǒng)架構(gòu)基礎(chǔ)名詞有哪些呢?STM32時(shí)鐘系統(tǒng)有哪些性能呢?

2021-12-14 07:49:07

),. clk_out1(link_clock))從serdes TX時(shí)鐘制作繪圖時(shí)鐘;我希望鏈接時(shí)鐘是txusrclk的兩倍,因?yàn)镚TX一次使用兩個(gè)字節(jié)。但是link_clock是靜態(tài)的,DRP_CLK_O是200Mhz,gt0_pll0lock_out是16Khz的方波。系統(tǒng)似乎一直在重置!戴夫

2020-07-31 09:10:30

我想把c6455 srio配置為1P4X的模式,是不是這種模式下只使用一個(gè)port,那么我在設(shè)置寄存器SERDES_CFGRXn_CNTL和SERDES_CFGTXn_CNTL的時(shí)候,只使能

2019-01-21 15:42:20

大家好。BUFG資源和DCM / PLL模塊在許多FPGA線路上使用專用時(shí)鐘布線資源。對(duì)于SerDes應(yīng)用,我們使用BUFIO2來獲得DDR SerDes IOCLK,SerDes Strobe

2019-07-30 10:35:37

大家好, 在一個(gè)I / O塊中有一個(gè)主serdes和一個(gè)slave serdes。如果我使用主設(shè)備,奴隸不能使用,是不是?謝謝。最好的祝福。

2020-06-08 15:03:22

什么是SerDes?

2021-06-24 07:52:02

嗨, 我計(jì)劃在我的設(shè)計(jì)中使用SERDES(LVDS)作為背板。我已經(jīng)瀏覽了virtex5用戶指南中的advnced IO部分,并看過ISERDES_NODELAY和OSERDES宏。我已經(jīng)看到了一些

2020-07-13 15:54:49

沖突、降低開關(guān)噪聲、更低的功耗和封裝成本等許多好處。而SERDES技術(shù)的主要缺點(diǎn)是需要非常精確、超低抖動(dòng)的元件來提供用于控制高數(shù)據(jù)速率串行信號(hào)所需的參考時(shí)鐘。即使嚴(yán)格控制元件布局,使用長度短的信號(hào)并

2019-05-21 05:00:13

本文將討論通過優(yōu)化封裝內(nèi)的阻抗不連續(xù)性和改善其回波損耗性能,以滿足10Gbps SerDes鍵合線封裝規(guī)范。

2021-04-25 07:42:13

約束將無法在時(shí)序分析期間返回任何路徑”,因此,當(dāng)我們使用輸入SerDes時(shí)鐘資源來生成DDR時(shí)鐘時(shí),我們不會(huì)期望任何分析甚至是建立/保持違規(guī)的通知。2)在同一白皮書中,“OFFSET約束不優(yōu)化由內(nèi)部

2019-08-09 09:54:33

我在官網(wǎng)上下載了CH569的數(shù)據(jù)手冊(cè)和參考應(yīng)用例程(EVT), 發(fā)現(xiàn)對(duì)SerDes這塊的介紹很少, 而且EVT里也沒有SerDes相關(guān)的例程.我想使用SerDes連接SFP模塊來測(cè)試光纖通信.請(qǐng)問可以提供下關(guān)于SerDes的詳細(xì)資料嗎, 謝謝.

2022-05-18 08:37:16

需要生成一個(gè)低速單端時(shí)鐘來測(cè)試非常慢的serdes通道(長篇故事為什么它如此低和單端)。我試圖在低頻模式下使用V5 DCM接受2.5MHz的輸入時(shí)鐘并產(chǎn)生15MHz-17.5MHz。當(dāng)我使用GUI

2020-06-15 16:11:09

如何更有效地使用可編程時(shí)鐘器件?設(shè)計(jì)SERDES參考時(shí)鐘源面臨的挑戰(zhàn)有哪些?如何去實(shí)現(xiàn)XAUI參考時(shí)鐘源?

2021-04-20 06:03:53

Recovery,時(shí)鐘數(shù)據(jù)恢復(fù)),完成100~200Mhz的板間SERDES單通道通信,該SERDES接口方案具有成本低、靈活性高、研發(fā)周期短等特點(diǎn)。

2019-10-21 07:09:44

SerDes的基本結(jié)構(gòu)是由哪些部分組成的?怎樣去更好地使用SerDes?

2021-09-22 06:25:17

SerDes是怎么工作的?SerDes有傳輸時(shí)鐘信號(hào)嗎?

2021-10-18 08:53:42

SERDES的作用有哪些?SerDes的主要構(gòu)成可以分為哪幾部分?

2021-10-18 09:25:08

漂移及漂移形成的原因是什么?光纖漂移引起的SERDES FIFO溢出問題分析BBU SERDES 雙系時(shí)鐘方案及具體實(shí)現(xiàn)

2021-04-19 08:35:11

的serdes?2、如果serdes是各自的,是否共享輸入時(shí)鐘?(外部時(shí)鐘,對(duì)于我們來說是156.25MHz)3、在研究SRIO速率配置時(shí)發(fā)現(xiàn)文檔中描述:serdes的輸出時(shí)鐘不能超過3.125GHz,該描述是否準(zhǔn)確?是否適用于所有的serdes模塊?謝謝!

2018-08-06 06:17:36

6678中的srio的serdes和以太網(wǎng)的serdes是共用還是各自有自己的serdes?

2018-08-02 06:11:31

7系列系列中的SERDES是否有最小延遲規(guī)范?我想了解如果SERDES直接(最短路徑)連接到另一個(gè)SERDES以實(shí)現(xiàn)GTH收發(fā)器之間的最小延遲串行到串行連接,那將是什么樣的。

2020-07-22 13:45:34

bufg用于非時(shí)鐘輸入邏輯?你可以使用組合邏輯和serdes選通來獲得時(shí)序嗎?以上來自于谷歌翻譯以下為原文I'm a bit confused on the Spartan 6 clocking when

2019-06-19 06:38:52

選擇SerDes參考時(shí)鐘。各功能需要的時(shí)鐘如下圖:這就是我們需要配置的PLL1和PLL2,硬件和軟件需要同時(shí)做好。參考的時(shí)鐘源我們?cè)诤诵陌迳弦呀?jīng)做好,用戶不需要額外做這部分的硬件。 具體是這樣實(shí)現(xiàn)

2020-10-28 17:15:14

之后,還需要選擇SerDes參考時(shí)鐘。各功能需要的時(shí)鐘如下圖:?這就是我們需要配置的PLL1和PLL2,硬件和軟件需要同時(shí)做好。參考的時(shí)鐘源我們?cè)诤诵陌迳弦呀?jīng)做好,用戶不需要額外做這部分的硬件。 具體

2020-11-01 20:21:02

SERDES結(jié)構(gòu)是怎樣構(gòu)成的?高速SERDES接口在網(wǎng)絡(luò)方面有哪些應(yīng)用?

2021-04-28 07:19:38

SerDes/Differential Pair-- The Feature of High Speed Designreference list– reference1:link 應(yīng)對(duì)未來高速

2021-11-12 06:46:26

引言在有線通信中,需要從數(shù)據(jù)中恢復(fù)時(shí)鐘。將時(shí)鐘編碼到數(shù)據(jù)中的優(yōu)點(diǎn)是可以省卻發(fā)送時(shí)鐘的線路,也有助于處理偏移問題。SERDES(串行器-解串器)器件諸如SCAN25100可

2008-08-15 22:51:17 21

21 M31 SerDes PHY IP M31 SerDes PHY IP為高帶寬應(yīng)用提供高性能、多通道功能和低功耗架構(gòu)。SerDes IP支持從1.25G到10.3125Gbps的數(shù)據(jù)速率

2023-04-03 20:29:47

串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)的帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初

2010-02-25 23:03:44 38

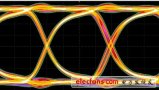

38 利用眼圖模板評(píng)估串行器和解串器(SerDes)的性能

Abstract: Maxim has developed a family of serializer and deserializer

2008-11-26 14:08:24 2054

2054

摘要:Maxim開發(fā)了一系列串行器和解串器,廣泛用于視頻顯示和數(shù)字圖像系統(tǒng)中的高速、串行數(shù)據(jù)互聯(lián)。目前,設(shè)計(jì)人員急需找到一種測(cè)試由串行器和解串器(SerDes)芯片組搭建的串行

2009-05-02 10:32:33 2031

2031

該應(yīng)用筆記介紹如何根據(jù)STO超時(shí)、時(shí)鐘頻率和UART位時(shí)鐘計(jì)算MAX9257/MAX9258可編程串行器/解串器(SerDes)的CCEN持續(xù)時(shí)間。

2011-07-30 22:55:13 1353

1353

討論了物理設(shè)計(jì)中時(shí)鐘網(wǎng)絡(luò)的設(shè)計(jì)技術(shù),并以現(xiàn)有的CPU時(shí)鐘網(wǎng)絡(luò)的為例,介紹了高性能CPU的時(shí)鐘網(wǎng)絡(luò)設(shè)計(jì)技術(shù)。

2011-12-27 15:28:56 46

46 SERDES在數(shù)字系統(tǒng)中高效時(shí)鐘設(shè)計(jì)方案,無論是在一個(gè)FPGA、SoC還是ASSP中,為任何基于SERDES的協(xié)議選擇一個(gè)參考時(shí)鐘源都是非常具有挑戰(zhàn)性的。

2012-02-16 11:23:43 5384

5384

本文以TLK3132為例,詳細(xì)介紹了SERDES工作原理和器件特點(diǎn),并以WI系統(tǒng)中的CPRI應(yīng)用需求為例,提供TLK3132的設(shè)計(jì)方法等。

2012-05-07 16:01:58 6293

6293

電子發(fā)燒友網(wǎng): 本文主要講述的是 LatticeECP4 高速可配置SERDES。 LatticeECP4 FPGA系列結(jié)合了高性能 FPGA 結(jié)構(gòu)、高性能I/O和多達(dá)16個(gè)通道的嵌入式SERDES,帶有相關(guān)的物理編碼子層(PCS)邏輯。每

2012-06-12 10:41:35 1439

1439

FPGA SERDES的應(yīng)用需要考慮到板級(jí)硬件,SERDES參數(shù)和使用,應(yīng)用協(xié)議等方面。由于這種復(fù)雜性,SERDES的調(diào)試工作對(duì)很多工程師來說是一個(gè)挑戰(zhàn)。

2013-03-15 14:55:13 10360

10360

如何使用 HyperLynx DRC 來查找 SERDES 設(shè)計(jì)問題

2016-01-06 14:49:36 0

0 如何使用 HyperLynx DRC 來查找 SERDES 設(shè)計(jì)問題

2016-05-24 17:12:50 0

0 沖突、降低開關(guān)噪聲、更低的功耗和封裝成本等許多好處。而SERDES技術(shù)的主要缺點(diǎn)是需要非常精確、超低抖動(dòng)的元件來提供用于控制高數(shù)據(jù)速率串行信號(hào)所需的參考時(shí)鐘。即使嚴(yán)格控制元件布局,使用長度短的信號(hào)并遵循信號(hào)走線限制,這些接口的抖動(dòng)

2017-10-26 15:37:45 4

4 高性能CPU的時(shí)鐘網(wǎng)絡(luò)設(shè)計(jì)

2017-10-30 15:28:58 23

23 在很多無線或者有線的系統(tǒng)應(yīng)用中,都需要器件的接收端能夠和鏈路的發(fā)送端的頻率做跟隨。通常的實(shí)現(xiàn)方案都是通過將SERDES的恢復(fù)時(shí)鐘引到芯片外部,然后通過一個(gè)cleanup PLL過濾抖動(dòng),然后同時(shí)再生出低相位抖動(dòng)的跟隨時(shí)鐘,然后將此時(shí)鐘作為SERDES的參考時(shí)鐘。

2017-11-18 12:08:49 5864

5864

的量產(chǎn)測(cè)試。那么,Nautilus UDI方案是如何實(shí)現(xiàn)包括UDI結(jié)構(gòu)、輸入時(shí)鐘設(shè)計(jì)、Load board設(shè)計(jì)、socket選型等多個(gè)測(cè)試環(huán)節(jié)高速SerDes測(cè)試的呢?

2018-06-10 10:51:17 4434

4434

對(duì)于10Gbps及以上數(shù)據(jù)速率的SerDes,每個(gè)數(shù)據(jù)位的單位間隔是隨著近 20~30ps的信號(hào)上升/下降時(shí)間而縮短的。

2018-07-18 17:18:48 7390

7390

Recovery,時(shí)鐘數(shù)據(jù)恢復(fù)),完成100~200Mhz的板間SERDES單通道通信,該SERDES接口方案具有成本低、靈活性高、研發(fā)周期短等特點(diǎn)。

2019-05-24 15:33:25 4073

4073

只要SERDES接口的高級(jí)架構(gòu)是合理的,SERDES總線的成功實(shí)現(xiàn)就歸結(jié)為“實(shí)現(xiàn)細(xì)節(jié)”。

2019-08-14 17:57:00 2615

2615 隨著SerDes 速度的增加,參考時(shí)鐘所需的 RMS 相位抖動(dòng)性能隨之減少。在本次網(wǎng)絡(luò)研討會(huì)上,我們概述最新一代FPGA、光學(xué)DSP、相干DSP 和網(wǎng)絡(luò)處理器的參考時(shí)鐘要求,并重點(diǎn)介紹Si54x Ultra Series XO 和 VCXO 產(chǎn)品家族的關(guān)鍵功能

2020-11-03 17:13:10 2613

2613 為滿足目前的56GPAM-4 SerDes技術(shù),以支持更高帶寬的100G+以太網(wǎng)和光網(wǎng)絡(luò)設(shè)計(jì)。硬件開發(fā)人員通常需要100fs(典型值)以下RMS相位抖動(dòng)規(guī)范的時(shí)鐘。這些設(shè)計(jì)通常需要與CPU和系統(tǒng)時(shí)鐘等其他頻率時(shí)鐘混用。

2020-11-12 15:25:55 4154

4154 為了學(xué)習(xí)xilinx serdes 原語的使用,以及交流學(xué)習(xí)經(jīng)驗(yàn),在工程項(xiàng)目中方便的應(yīng)用SERDES進(jìn)行設(shè)計(jì),故編寫此文檔。

2021-02-26 10:04:00 37

37 ADN2865:連續(xù)速率12.3Mb/s至2.7 Gb/s時(shí)鐘和數(shù)據(jù)恢復(fù)IC,帶環(huán)路定時(shí)SERDES初步數(shù)據(jù)表

2021-05-09 14:33:49 7

7 ,另一個(gè)優(yōu)勢(shì)是能夠通過一對(duì)差分對(duì)信號(hào)引腳(而不是8、16、32或N個(gè)數(shù)據(jù)引腳和一個(gè)時(shí)鐘引腳)發(fā)送數(shù)據(jù)。在串行傳輸這個(gè)方面得益于更小的數(shù)據(jù)包和更密集的pcb而節(jié)省了成本。具體取決于晶片成本、封裝成本、PCB成本和PCB擁塞等因素。 距離優(yōu)勢(shì) 在過去的十年里,SERDES在PCB和基

2021-07-23 11:59:46 3795

3795 SerDes/Differential Pair-- The Feature of High Speed Designreference list– reference1:link 應(yīng)對(duì)未來高速

2021-11-07 10:21:00 47

47 SERDES最明顯的優(yōu)勢(shì)是具備更少的引腳數(shù)量和線纜/通道數(shù)量。對(duì)于早期的SERDES,這意味著數(shù)據(jù)可以通過同軸電纜或光纖發(fā)送。

2022-07-22 10:39:21 2436

2436 112Gbps SerDes設(shè)計(jì)將根據(jù)應(yīng)用情況在各種配置中被采用。下圖展示了長距離(LR)、中距離(MR)、極短距離(VSR)和超短距離(XSR)拓?fù)洌渲?12G信令路徑在每個(gè)拓?fù)渲卸纪怀鲲@示。

2022-07-27 15:05:16 1091

1091 FPGA發(fā)展到今天,SerDes(Serializer-Deserializer)基本上是標(biāo)配了。

2022-10-31 11:28:41 1350

1350 SerDes 是空間到時(shí)間到空間的轉(zhuǎn)換。并行數(shù)據(jù)同時(shí)傳輸?shù)加貌煌奈锢砘ミB,串行數(shù)據(jù)共享相同的物理空間但占用不同的時(shí)間時(shí)刻

2023-01-31 14:13:37 3369

3369 到Serial RIO……等等,都是在借助SerDes來提高數(shù)據(jù)傳輸?shù)?b class="flag-6" style="color: red">性能。SerDes是非常復(fù)雜的數(shù)模混合設(shè)計(jì),用戶手冊(cè)的內(nèi)容只是描述了相對(duì)粗略的概念以及使用方法,并不能完全解釋SerDes是怎么工作

2023-03-16 10:28:11 1915

1915

同時(shí)介紹一種采用光電集成技術(shù)的,即采用光SerDes而非電SerDes的高速收發(fā)器。

2023-04-01 09:28:58 1078

1078 首先我們要了解什么是SerDes,SerDes的應(yīng)用場(chǎng)景又是什么呢?SerDes又有哪些常見的種類?

2023-06-06 17:03:55 4707

4707

8/10b的SerDes接口,包括SERDES收發(fā)單元,通過完全數(shù)字化的方法實(shí)現(xiàn)SERDES的CDR(Clock Data Recovery,時(shí)鐘數(shù)

2023-07-27 16:10:01 1566

1566

Xilinx公司的許多FPGA已經(jīng)內(nèi)置了一個(gè)或多個(gè)MGT(Multi-Gigabit Transceiver)收發(fā)器,也叫做SERDES(Multi-Gigabit Serializer/Deserializer)。MGT收發(fā)器內(nèi)部包括高速串并轉(zhuǎn)換電路、時(shí)鐘數(shù)據(jù)恢復(fù)電路、數(shù)據(jù)編解碼電路、時(shí)鐘糾正和通道綁定電路

2023-07-29 16:47:04 468

468

業(yè)界高端FPGA的卓越性能和高口碑聲譽(yù)都有哪些因素了?其中很重要的一個(gè)因素就是FPGA內(nèi)部豐富的時(shí)鐘資源使得FPGA在處理復(fù)雜時(shí)鐘結(jié)構(gòu)和時(shí)序要求的設(shè)計(jì)中具有很大優(yōu)勢(shì)。設(shè)計(jì)師可以更好地控制和管理時(shí)鐘信號(hào),提高時(shí)序性能、減少時(shí)鐘相關(guān)問題,并滿足設(shè)計(jì)的高性能和穩(wěn)定性要求。

2023-08-31 10:44:01 530

530 到Serial RIO……等等,都是在借助SerDes來提高數(shù)據(jù)傳輸?shù)?b class="flag-6" style="color: red">性能。SerDes是非常復(fù)雜的數(shù)模混合設(shè)計(jì),用戶手冊(cè)的內(nèi)容只是描述了相對(duì)粗略的概念以及使用方法,并不能完全解釋SerDes是怎么工作

2023-10-16 14:50:37 558

558

盡管設(shè)計(jì)和驗(yàn)證很復(fù)雜,SERDES 已成為 SoC 模塊不可或缺的一部分。隨著 SERDES IP 模塊現(xiàn)已推出,它有助于緩解任何成本、風(fēng)險(xiǎn)和上市時(shí)間問題。

2023-10-23 14:44:59 449

449

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論