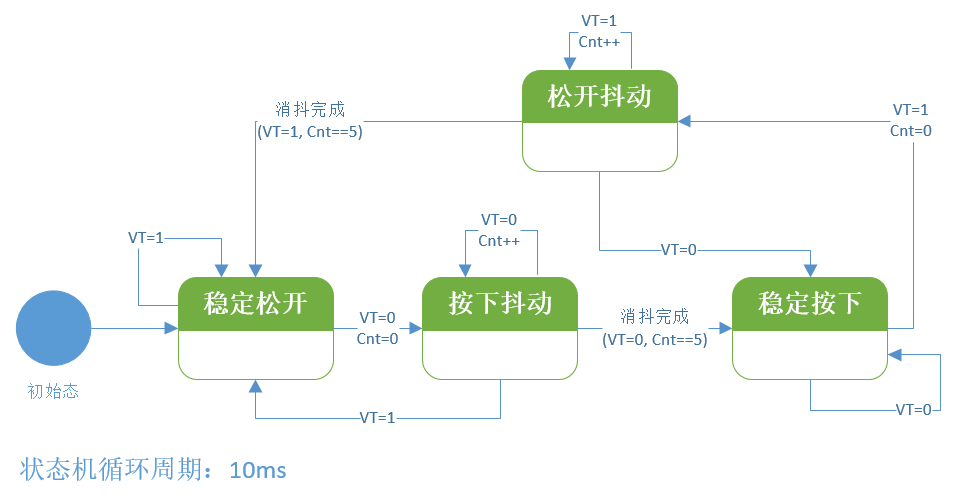

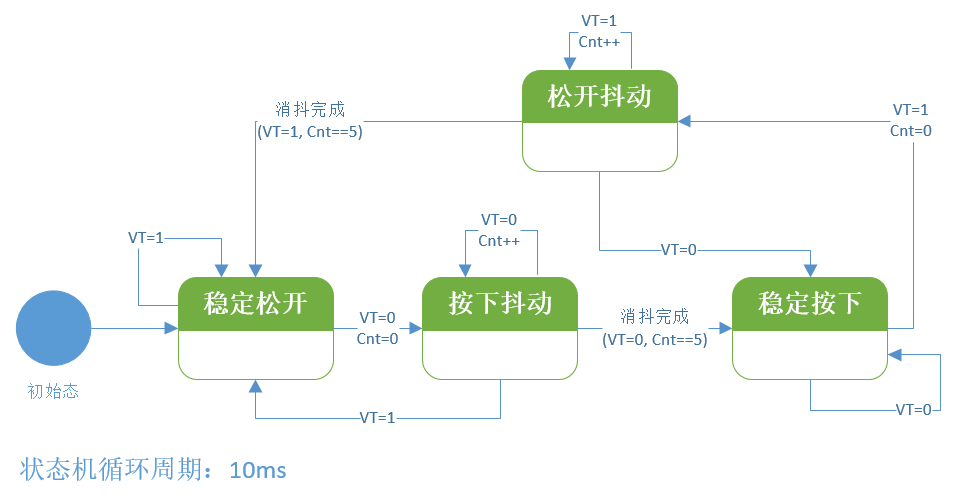

本篇繼續(xù)介紹狀態(tài)機(jī)的使用,在上篇的基礎(chǔ)上,通過簡化按鍵去抖邏輯,并增加按鍵長按功能,進(jìn)一步介紹狀態(tài)圖的修改與狀態(tài)機(jī)代碼的實(shí)現(xiàn),并通過實(shí)際測試,演示狀態(tài)機(jī)的運(yùn)行效果。

2022-09-03 21:26:52 3277

3277

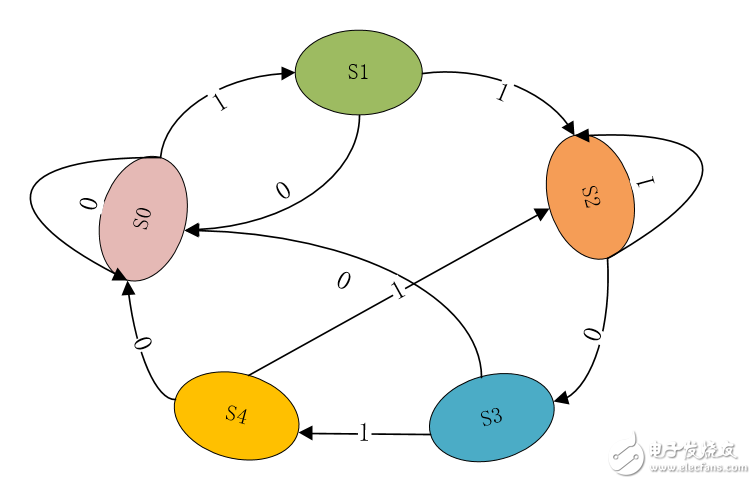

在verilog中狀態(tài)機(jī)的一種很常用的邏輯結(jié)構(gòu),學(xué)習(xí)和理解狀態(tài)機(jī)的運(yùn)行規(guī)律能夠幫助我們更好地書寫代碼,同時作為一種思想方法,在別的代碼設(shè)計(jì)中也會有所幫助。 一、簡介 在使用過程中我們常說

2024-02-12 19:07:39 1818

1818

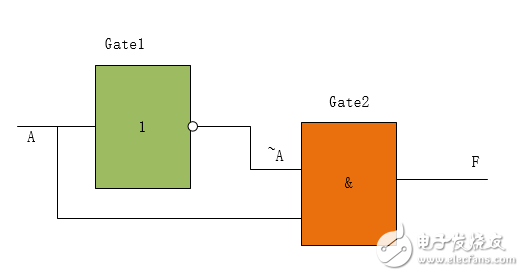

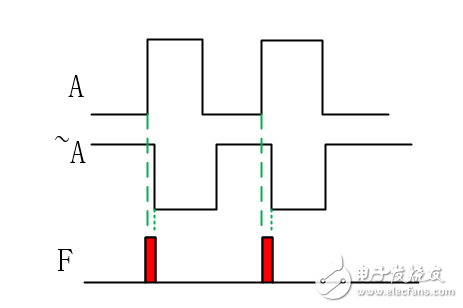

幫助。 產(chǎn)生原因 競爭 :在組合邏輯電路中不同路徑的輸入信號到達(dá)同一個門級電路時,在時間上有先有后,這種先后時間上的差異稱之為競爭(Competition) 冒險(xiǎn) :由于競爭的存在,信號在過渡時間瞬間可能產(chǎn)生錯誤的輸出,例如尖峰脈沖。成

2024-02-18 14:34:11 456

456

狀態(tài)機(jī)

2017-09-12 13:56:23

控制狀態(tài)機(jī)控制狀態(tài)機(jī)的初始化和狀態(tài)轉(zhuǎn)換的最佳方法是使用枚麗型輸入控件。一般使用自定義類型的枚麗變量。使用子定義類型的枚麗變量可以是控件和實(shí)例乊間存在關(guān)聯(lián),使得添加或刪除狀態(tài)時所有的枚麗型輸入控件副本自動更新。

2014-02-13 12:39:31

最實(shí)用的狀態(tài)機(jī)模板

2017-06-08 15:45:18

狀態(tài)機(jī) 狀態(tài)圖

2012-08-22 19:45:36

程序一運(yùn)行 就開始自動運(yùn)行程序 狀態(tài)機(jī)各種各種狀態(tài)開始執(zhí)行 我這里是布爾變量 每一秒點(diǎn)亮一個布爾按鈕。我現(xiàn)在想在界面增加一個暫停按鈕 當(dāng)點(diǎn)暫停時候 此時暫停按鈕文字成為繼續(xù) 如果 狀態(tài)機(jī)執(zhí)行第二步

2018-04-09 09:23:30

剛開始學(xué)fpga,讀資料,有些名詞不太理解,比如狀態(tài)機(jī),我只知道fpga就是由查找表和觸發(fā)器構(gòu)成的,狀態(tài)機(jī)這個概念是怎么提出來的,干什么使得,求大神講解,什么情況下用到

2013-04-25 18:35:55

狀態(tài)機(jī)可歸納為哪幾個要素?狀態(tài)機(jī)可分為哪幾種?什么是消息觸發(fā)類型的狀態(tài)機(jī)?

2021-04-19 06:02:21

以前寫狀態(tài)機(jī),比較常用的方式是用 if-else 或 switch-case,高級的一點(diǎn)是函數(shù)指針列表。最近,看了一文章《c語言設(shè)計(jì)模式–狀態(tài)模式(狀態(tài)機(jī))》(來源:embed linux

2022-02-15 06:01:46

自己編寫的狀態(tài)機(jī)結(jié)構(gòu)程序

2017-08-14 21:46:43

進(jìn)行程序設(shè)計(jì)的基本方法與技巧。一、有限狀態(tài)機(jī)分析設(shè)計(jì)的基本原理對于電子技術(shù)和電子工程類的讀者,最先接觸和使用到狀態(tài)機(jī)應(yīng)該是在數(shù)字邏輯電路課程里,狀態(tài)機(jī)的思想和分析方法被應(yīng)用于時序邏輯電路設(shè)計(jì)。其實(shí)

2008-07-10 18:00:24

.smp_rdy_i和rdy_i是來自其他模塊的信號,它與狀態(tài)機(jī)處于同一時鐘域,但是從寄存器輸出后,兩個信號傳遞了一些組合邏輯。通常,關(guān)于A,B,C,D的跳躍碼如下:來自A-B-C-D的狀態(tài),我認(rèn)為在狀態(tài)D中

2020-07-08 10:51:29

本帖最后由 inception1900 于 2015-11-16 14:51 編輯

tmp,tmp_num 是std_logic_vector(15 downto 0),tmp輸入,tmp_num 輸出,如何消除下面VHDL描述組合邏輯出現(xiàn)的競爭(不采用時鐘方式)tmp_num(15)

2015-11-16 14:50:26

`對于一個組合邏輯電路,如果有兩個輸入端,那么只有兩個輸入端一個從0變1,另一個從1變0是才有可能產(chǎn)生競爭冒險(xiǎn)嗎,如果開始時兩個輸入端都是1,那么同時從1變0時會不會產(chǎn)生競爭。例如異或門,開始始輸入

2015-12-22 18:49:44

來看看三種方式是如何實(shí)現(xiàn)的。 (各種圖片,各種坑爹啊 - -!)一段式狀態(tài)機(jī) 當(dāng)把整個狀態(tài)機(jī)卸載一個always模塊中,并且這個模塊既包含狀態(tài)轉(zhuǎn)移,又含有組合邏輯輸入/輸出時,稱為一段式狀態(tài)機(jī)。不

2012-03-09 10:04:18

影響電路工作的可靠性、穩(wěn)定性,嚴(yán)重時會導(dǎo)致整個數(shù)字系統(tǒng)的誤動作和邏輯紊亂。下面就來討論交流一下FPGA 的競爭冒險(xiǎn)與毛刺問題。

在數(shù)字電路中,常規(guī)介紹和解釋:

什么是競爭與冒險(xiǎn)現(xiàn)象:

在組合電路中

2023-11-02 17:22:20

今天給大俠帶來如何寫好狀態(tài)機(jī),狀態(tài)機(jī)是邏輯設(shè)計(jì)的重要內(nèi)容,狀態(tài)機(jī)的設(shè)計(jì)水平直接反應(yīng)工程師的邏輯功底,所以很多公司在硬件工程師及邏輯工程師面試中,狀態(tài)機(jī)設(shè)計(jì)幾乎是必選題目。本篇在引入狀態(tài)機(jī)設(shè)計(jì)思想

2020-09-28 10:29:23

FPGA狀態(tài)機(jī)的文書資料

2014-09-14 19:01:20

FPGA中競爭冒險(xiǎn)問題的研究

2012-08-04 16:16:06

競爭冒險(xiǎn):在組合電路中,當(dāng)邏輯門有兩個互補(bǔ)輸入信號同時向相反狀態(tài)變化時,輸出端可能產(chǎn)生過渡干擾脈沖的現(xiàn)象,稱為競爭冒險(xiǎn)。那么 FPGA 產(chǎn)生競爭冒險(xiǎn)的原因是什么呢? 信號在 FPGA 器件內(nèi)部通過

2024-02-21 16:26:56

冒險(xiǎn)往往會影響到邏輯電路的穩(wěn)定性。時鐘端口、清零和置位端口對毛刺信號十分敏感,任何一點(diǎn)毛刺都可能會使系統(tǒng)出錯,因此判斷邏輯電路中是否存在冒險(xiǎn)以及如何避免冒險(xiǎn)是設(shè)計(jì)人員必須要考慮的問題。如何處理毛刺

2018-08-01 09:53:36

和二進(jìn)制表示有沒有什么影響?3,好的狀態(tài)機(jī)寫法是,在狀態(tài)判斷的組合邏輯always塊中,最好先定義一個初始化狀態(tài),case中最好定義一個默認(rèn)狀態(tài),初始化狀態(tài)是不是必要,定義為全零好還是不定態(tài)“x“好呢。困擾好久了,求解答,謝謝

2014-03-06 19:49:09

摘 要:以現(xiàn)場可編程門陣列(以下簡稱FPGA)在設(shè)計(jì)中由于其內(nèi)部構(gòu)成,容易引起競爭問題。以我們在實(shí)驗(yàn)教學(xué)中的應(yīng)用與實(shí)踐為主線,詳細(xì)介紹了消除競爭冒險(xiǎn)的各種方法。關(guān)鍵詞:現(xiàn)場可編程

2009-04-21 16:44:44

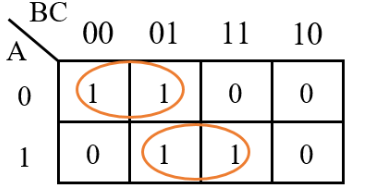

時序電路)。 在組合邏輯電路中,任何時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態(tài)無關(guān)。這就是組合邏輯電路在邏輯功能上的共同特點(diǎn)。在上一節(jié)中,設(shè)計(jì)的三人表決器就是組合邏輯電路,輸出與輸入一一對應(yīng),和其他

2023-02-21 15:35:38

求LABVIEW狀態(tài)機(jī)與隊(duì)列的詳細(xì)資料。

2015-12-12 15:35:01

本帖最后由 afnuaa 于 2017-5-24 11:22 編輯

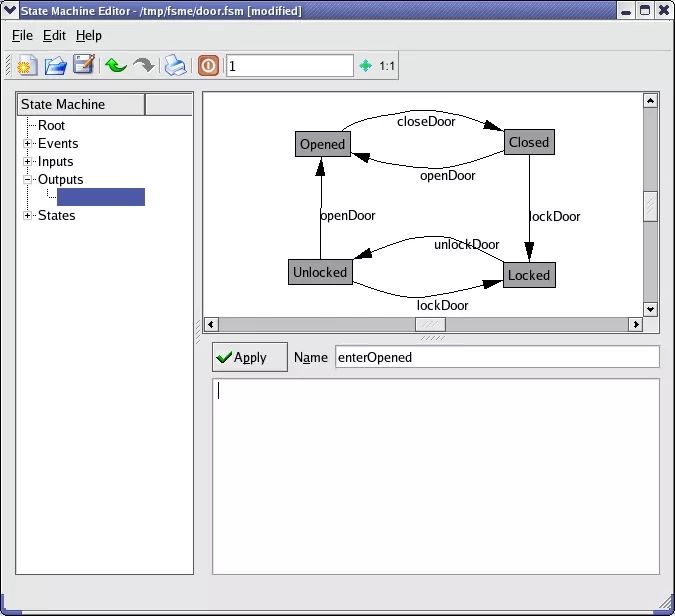

狀態(tài)機(jī)是一種普遍而有效的架構(gòu),我們可以利用狀態(tài)機(jī)設(shè)計(jì)模式來實(shí)現(xiàn)狀態(tài)圖或流程圖的算法。State Machines

2017-05-23 17:11:34

執(zhí)行超時里的東西。一旦VI檢測到有更新就會觸發(fā)用戶事件。狀態(tài)機(jī)執(zhí)行用戶事件里的東西。(如圖3)用戶事件里的東西,我們就是把開始這個全局變量的值改變。當(dāng)開始的值改變后就能進(jìn)入邏輯判斷的VI了,該VI在處理

2018-12-25 16:53:35

的邏輯時,往往能化繁為簡,出奇制勝。由于狀態(tài)機(jī)的特殊編程機(jī)制,狀態(tài)機(jī)往往配合事件驅(qū)動機(jī)制來配合一起使用。raw os巧妙地把狀態(tài)機(jī)編程引進(jìn)到了空閑任務(wù)里,這樣的話系統(tǒng)空閑的時候可以進(jìn)行面向狀態(tài)機(jī)的編程

2013-02-27 14:35:10

波形仿真時verilog 寫的狀態(tài)機(jī)被綜合掉,編譯沒有錯誤,狀態(tài)轉(zhuǎn)移也沒錯,什么原因可能導(dǎo)致這種問題呢。

2017-10-05 11:31:26

的RTL視圖中可以看出二進(jìn)制比獨(dú)熱碼使用更少的寄存器。 二進(jìn)制用7個寄存器就可以實(shí)現(xiàn)100個狀態(tài)的狀態(tài)機(jī),但是獨(dú)熱碼就需要100個寄存器。但是另一方面,雖然獨(dú)熱碼使用更多的寄存器但是其組合邏輯相對簡單

2016-12-26 00:17:38

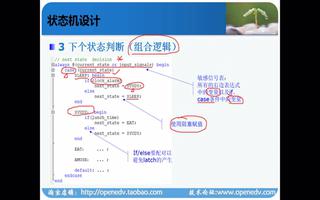

;(2)二段式:用兩個always模塊來描述狀態(tài)機(jī),其中一個always模塊采用同步時序描述狀態(tài)轉(zhuǎn)移;另一個模塊采用組合邏輯判斷狀態(tài)轉(zhuǎn)移條件,描述狀態(tài)轉(zhuǎn)移規(guī)律以及輸出;(3)三段式:在兩個always

2015-05-25 20:33:02

穩(wěn)定狀態(tài)所需的時間不同,稱為競爭。 邏輯門因輸入端的競爭而導(dǎo)致輸出產(chǎn)生不應(yīng)有的尖峰干擾脈沖(又稱過渡干擾脈沖)的現(xiàn)象,稱為冒險(xiǎn)。 在實(shí)際電路中,輸入信號通過每一個門電路然后輸出,它總是要有傳輸時間

2020-04-24 15:07:49

事件狀態(tài)機(jī)

2018-11-07 16:24:00

一. 什么是狀態(tài)機(jī)我們以生活中的小區(qū)的停車系統(tǒng)為例:停車桿一般沒車的是不動的(初態(tài)),有車來的時候需要抬桿(狀態(tài)1),車通過需要放桿(狀態(tài)2),如果在放桿的過程中突然有車,又需要抬桿(狀態(tài)3

2022-01-06 08:01:00

目錄1 前言2 狀態(tài)機(jī)2.1 什么是狀態(tài)機(jī)2.2 狀態(tài)機(jī)的概念2.3 使用狀態(tài)機(jī)寫鍵盤的思路3 代碼實(shí)例3.1 使用軟件3.2 protues電路圖3.2 狀態(tài)機(jī)部分程序3.3 Keil工程文件

2022-01-24 06:23:02

什么是狀態(tài)機(jī)?狀態(tài)機(jī)是如何編程的?

2021-10-20 07:43:43

文章目錄1、什么是狀態(tài)機(jī)?2、狀態(tài)機(jī)編程的優(yōu)點(diǎn)(1)提高CPU使用效率(2) 邏輯完備性(3)程序結(jié)構(gòu)清晰3、狀態(tài)機(jī)的三種實(shí)現(xiàn)方法switch—case 法表格驅(qū)動法函數(shù)指針法小節(jié)摘要:不知道大家

2021-12-22 06:51:58

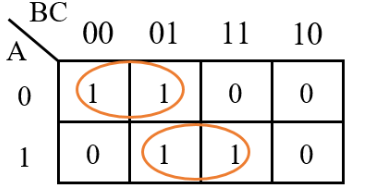

在組合邏輯中,由于門的輸入信號通路中經(jīng)過了不同的延時,導(dǎo)致到達(dá)該門的時間不一致叫競爭。產(chǎn)生毛刺叫冒險(xiǎn)。 如果布爾式中有相反的信號則可能產(chǎn)生競爭和冒險(xiǎn)現(xiàn)象。 解決方法:一是添加布爾式的消去項(xiàng),二是在芯片外部加電容。

2019-08-02 11:57:35

在嵌入式,機(jī)器人領(lǐng)域,由于多的復(fù)雜邏輯狀態(tài),我們編寫程序的時候不得不考慮很多種情況,容易造成功能間的沖突。有限狀態(tài)機(jī)(finite-state machine),簡稱狀態(tài)機(jī),是一種表示有限個狀態(tài)以及狀態(tài)間轉(zhuǎn)移等行為的數(shù)學(xué)模型。狀態(tài)機(jī)簡單來說

2021-12-20 06:51:26

從事邏輯設(shè)計(jì)的小伙伴對狀態(tài)機(jī)這個詞并不陌生,什么兩段、三段狀態(tài)機(jī)耳熟能詳,摩爾、米利狀態(tài)機(jī)型倒背如流。然而不得不承認(rèn)的是讀別人的RTL代碼真的是一件痛苦的事情,那狀態(tài)機(jī)可否更優(yōu)雅的呈現(xiàn)呢?狀態(tài)機(jī)那些

2022-07-13 14:56:24

的輸出與輸入直接相關(guān),時序邏輯的輸出和原有狀態(tài)也有關(guān)。●組合邏輯立即反應(yīng)當(dāng)前輸入狀態(tài),時序邏輯還必須在時鐘上升沿觸發(fā)后輸出新值。●組合邏輯容易出現(xiàn)競爭、冒險(xiǎn)現(xiàn)象,時序邏輯一般不會出現(xiàn)。●組合邏輯的時序

2017-11-17 18:47:44

積少成多,集腋成裘,堅(jiān)持!!!目錄1. 進(jìn)制轉(zhuǎn)換2. 狀態(tài)機(jī)和編碼方式3. 存儲器的分類4. Verilog語法中的操作符5. 對組合邏輯的認(rèn)識6. 對時序邏輯的認(rèn)識7. 競爭冒險(xiǎn)的認(rèn)識8.

2021-07-26 07:14:31

根據(jù)CLD的課程寫的取款機(jī)的邏輯。一邊看一邊改,從最簡單的狀態(tài)機(jī),到事件驅(qū)動,生產(chǎn)者消費(fèi)者模型,隊(duì)列狀態(tài)機(jī),最后到AMC。實(shí)現(xiàn)的功能基本相同,但結(jié)構(gòu)各有不同。取款機(jī)的邏輯非常簡單,前面板也沒有美化,只是實(shí)現(xiàn)了邏輯。附件提供給大家,希望和大家一起討論學(xué)習(xí)。

2017-08-01 16:25:25

狀態(tài)機(jī)是邏輯設(shè)計(jì)的重要內(nèi)容,狀態(tài)機(jī)的設(shè)計(jì)水平直接反應(yīng)工程師的功底。

2012-03-12 16:30:24

一篇經(jīng)典文獻(xiàn),詳細(xì)講解了一段、兩段、三段式狀態(tài)機(jī)的實(shí)現(xiàn),效率、優(yōu)缺點(diǎn)。看完后相信會對狀態(tài)機(jī)有一個詳細(xì)的了解。 狀態(tài)機(jī)是邏輯設(shè)計(jì)的重要內(nèi)容,狀態(tài)機(jī)的設(shè)計(jì)水平直接反應(yīng)工程師的邏輯功底,所以許 多公司

2011-10-24 11:43:11

; elseout=0;endendmodule在進(jìn)行門級仿真的時候波形中出現(xiàn)了毛刺,也就是所謂的競爭冒險(xiǎn),如下圖書上也有競爭冒險(xiǎn)的解決辦法,但具體到代碼里還是不會,誰能教教我該怎么改這個代碼才能消除競爭冒險(xiǎn)?

2011-10-21 14:31:40

報(bào)警狀態(tài)機(jī)

2014-06-20 13:16:06

在實(shí)際的應(yīng)用中,根據(jù)有限狀態(tài)機(jī)是否使用輸入信號,設(shè)計(jì)人員經(jīng)常將其分為Moore型有限狀態(tài)機(jī)和Mealy型有限狀態(tài)機(jī)兩種類型。

2020-04-06 09:00:21

不僅便于閱讀、理解、維護(hù),而且利于綜合器優(yōu)化代碼,利于用戶添加合適的時序約束條件,利于布局布線器實(shí)現(xiàn)設(shè)計(jì)。在兩段式描述中,當(dāng)前狀態(tài)的輸出用組合邏輯實(shí)現(xiàn),可能存在競爭和冒險(xiǎn),產(chǎn)生毛刺。則要求對狀態(tài)機(jī)

2014-09-25 09:35:29

問題。

競爭冒險(xiǎn):在組合電路中,當(dāng)邏輯門有兩個互補(bǔ)輸入信號同時向相反狀態(tài)變化時,輸出端可能產(chǎn)生過渡干擾脈沖的現(xiàn)象,稱為競爭冒險(xiǎn)。

那么 FPGA 產(chǎn)生競爭冒險(xiǎn)的原因是什么呢?

信號在

2023-05-30 17:15:28

問個關(guān)于狀態(tài)機(jī)的問題,書上說的三段式狀態(tài)機(jī)的第三段,同步時序的狀態(tài)輸出部分的狀態(tài)到底是當(dāng)前態(tài)還是次態(tài)啊?有的書寫的是次態(tài),case(next_state),有的寫的是case(cur_state)。

2014-09-22 20:42:17

應(yīng)用LabView做的連接mdb數(shù)據(jù)庫,應(yīng)用隊(duì)列狀態(tài)機(jī)

2016-02-05 22:58:25

如何寫好狀態(tài)機(jī):狀態(tài)機(jī)是邏輯設(shè)計(jì)的重要內(nèi)容,狀態(tài)機(jī)的設(shè)計(jì)水平直接反應(yīng)工程師的邏輯功底,所以許多公司的硬件和邏輯工程師面試中,狀態(tài)機(jī)設(shè)計(jì)幾乎是必選題目。本章在引入

2009-06-14 19:24:49 96

96 狀態(tài)機(jī)舉例

你可以指定狀態(tài)寄存器和狀態(tài)機(jī)的狀態(tài)。以下是一個有四種狀態(tài)的普通狀態(tài)機(jī)。 // These are the symbolic names for states// 定義狀態(tài)的符號名稱parameter [1

2009-03-28 15:18:28 893

893 第二十一講 組合邏輯電路中的競爭冒險(xiǎn)

6.7.1 競爭冒險(xiǎn)現(xiàn)象及其產(chǎn)生的原因一、競爭、冒險(xiǎn)1.理想情況2.實(shí)際情況3.競

2009-03-30 16:25:35 2728

2728

組合邏輯中的競爭與冒險(xiǎn)及毛刺的處理方法 在組合邏輯中,由于門的輸入信號通路中經(jīng)過了不同的延時,導(dǎo)致到達(dá)該門的時間不一致叫競爭。產(chǎn)生毛刺叫冒險(xiǎn)。如果布爾式中有相反的信號則可能產(chǎn)生競爭和冒險(xiǎn)現(xiàn)象。解決方法:一是添加布爾式的(冗余)消去項(xiàng),但是不

2011-01-24 18:12:53 0

0 狀態(tài)機(jī)代碼生成工具狀態(tài)機(jī)代碼生成工具狀態(tài)機(jī)代碼生成工具狀態(tài)機(jī)代碼生成工具

2015-11-19 15:12:16 9

9 狀態(tài)機(jī)原理及用法狀態(tài)機(jī)原理及用法狀態(tài)機(jī)原理及用法

2016-03-15 15:25:49 0

0 。其只有外部硬件復(fù)位采用異步方式,其余信號均用全局時鐘進(jìn)行同步。把狀態(tài)機(jī)邏輯和算術(shù)邏輯及數(shù)據(jù)通道分開,把狀態(tài)機(jī)純粹當(dāng)作控制邏輯電路來使用,從而改善其性能。

2016-03-22 16:03:03 12

12 組合邏輯中的競爭與冒險(xiǎn)及毛刺的處理方法

2017-01-17 19:54:24 7

7 練習(xí)九.利用狀態(tài)機(jī)的嵌套實(shí)現(xiàn)層次結(jié)構(gòu)化設(shè)計(jì)目的:1.運(yùn)用主狀態(tài)機(jī)與子狀態(tài)機(jī)產(chǎn)生層次化的邏輯設(shè)計(jì);

2017-02-11 05:52:50 3126

3126

有限狀態(tài)機(jī)(FSM)是一種常見的電路,由時序電路和組合電路組成。設(shè)計(jì)有限狀態(tài)機(jī)的第一步是確定采用Moore狀態(tài)機(jī)還是采用Mealy狀態(tài)機(jī)。

2017-02-11 13:51:40 3881

3881

三段式結(jié)構(gòu)中,2個時序always塊分別用來描述現(xiàn)態(tài)邏輯轉(zhuǎn)移,及輸出賦值。組合always塊用于描述狀態(tài)轉(zhuǎn)移的條件。這種結(jié)構(gòu)是寄存器輸出,輸出無毛刺,而且代碼更清晰易讀,特別是對于復(fù)雜的狀態(tài)機(jī)來說,但是消耗的面積也更多點(diǎn)。這是一種比較流行的狀態(tài)機(jī)結(jié)構(gòu)。

2017-09-16 09:04:54 5

5 寄存器存儲狀態(tài)信息、組合邏輯產(chǎn)生下一個狀態(tài)和輸出值時,大量使用了FPGA的布線、查找表、寄存器等寶貴資源。

為了實(shí)現(xiàn)FPGA的可編程性,在其內(nèi)部使用了大量的可編程邏輯開關(guān)。由于可編程邏輯開關(guān)

2017-11-17 02:30:07 3184

3184

如何使用QII狀態(tài)機(jī)向?qū)?chuàng)建一個狀態(tài)機(jī)

2018-06-20 00:11:00 3940

3940

本篇文章包括狀態(tài)機(jī)的基本概述以及通過簡單的實(shí)例理解狀態(tài)機(jī)

2019-01-02 18:03:31 9928

9928

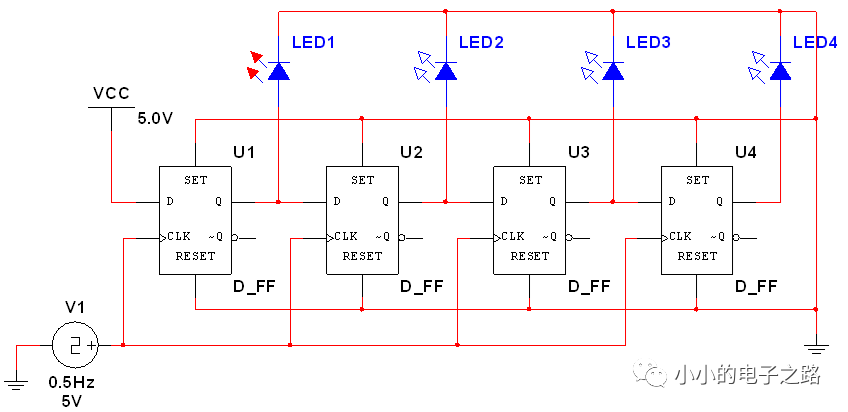

狀態(tài)機(jī)由狀態(tài)寄存器和組合邏輯電路構(gòu)成,能夠根據(jù)控制信號按照預(yù)先設(shè)定的狀態(tài)進(jìn)行狀態(tài)轉(zhuǎn)移,是協(xié)調(diào)相關(guān)信號動作,完成特定操作的控制中心。狀態(tài)機(jī)分為摩爾(Moore)型狀態(tài)機(jī)和米莉(Mealy)型狀態(tài)機(jī)。

2019-09-19 07:00:00 2178

2178

狀態(tài)機(jī)由狀態(tài)寄存器和組合邏輯電路構(gòu)成,能夠根據(jù)控制信號按照預(yù)先設(shè)定的狀態(tài)進(jìn)行狀態(tài)轉(zhuǎn)移,是協(xié)調(diào)相關(guān)信號動作,完成特定操作的控制中心。狀態(tài)機(jī)分為摩爾(Moore)型狀態(tài)機(jī)和米莉(Mealy)型狀態(tài)機(jī)。

2019-10-09 07:07:00 3198

3198 狀態(tài)機(jī)由狀態(tài)寄存器和組合邏輯電路構(gòu)成,能夠根據(jù)控制信號按照預(yù)先設(shè)定的狀態(tài)進(jìn)行狀態(tài)轉(zhuǎn)移,是協(xié)調(diào)相關(guān)信號動作、完成特定操作的控制中心。

2019-10-09 07:06:00 2234

2234 狀態(tài)機(jī)由狀態(tài)寄存器和組合邏輯電路構(gòu)成,能夠根據(jù)控制信號按照預(yù)先設(shè)定的狀態(tài)進(jìn)行狀態(tài)轉(zhuǎn)移,是協(xié)調(diào)相關(guān)信號動作、完成特定操作的控制中心。

2019-12-04 07:03:00 2880

2880

狀態(tài)機(jī)由狀態(tài)寄存器和組合邏輯電路構(gòu)成,能夠根據(jù)控制信號按照預(yù)先設(shè)定的狀態(tài)進(jìn)行狀態(tài)轉(zhuǎn)移,是協(xié)調(diào)相關(guān)信號動作、完成特定操作的控制中心。

2019-10-09 07:02:00 2137

2137 狀態(tài)機(jī)由狀態(tài)寄存器和組合邏輯電路構(gòu)成,能夠根據(jù)控制信號按照預(yù)先設(shè)定的狀態(tài)進(jìn)行狀態(tài)轉(zhuǎn)移,是協(xié)調(diào)相關(guān)信號動作,完成特定操作的控制中心。狀態(tài)機(jī)分為摩爾(Moore)型狀態(tài)機(jī)和米莉(Mealy)型狀態(tài)機(jī)。

2019-05-28 07:03:49 2648

2648 簡言之:在組合邏輯中,由于門的輸入信號通路中經(jīng)過了不同的延時,導(dǎo)致到達(dá)該門的時間不一致叫競爭,競爭產(chǎn)生冒險(xiǎn)。

2020-06-26 06:38:00 16665

16665 狀態(tài)機(jī) 1、狀態(tài)機(jī)是許多數(shù)字系統(tǒng)的核心部件,是一類重要的時序邏輯電路。通常包括三個部分:一是下一個狀態(tài)的邏輯電路,二是存儲狀態(tài)機(jī)當(dāng)前狀態(tài)的時序邏輯電路,三是輸出組合邏輯電路。 2、根據(jù)狀態(tài)機(jī)的輸出

2020-11-16 17:39:00 24811

24811 是FPGA設(shè)計(jì)中一種非常重要、非常根基的設(shè)計(jì)思想,堪稱FPGA的靈魂,貫穿FPGA設(shè)計(jì)的始終。 02. 狀態(tài)機(jī)簡介 什么是狀態(tài)機(jī):狀態(tài)機(jī)通過不同的狀態(tài)遷移來完成特定的邏輯操作(時序操作)狀態(tài)機(jī)是許多數(shù)字系統(tǒng)的核心部件, 是一類重要的時序邏輯電路。通常包括三個部分: 下一個

2020-11-05 17:58:47 6145

6145

狀態(tài)機(jī)是邏輯單元、存儲器單元和反饋的組合。狀態(tài)機(jī)的輸入與狀態(tài)機(jī)的當(dāng)前狀態(tài)組合在一起,確定下一個狀態(tài)。當(dāng)出現(xiàn)狀態(tài)時鐘時,下一個狀態(tài)成為當(dāng)前狀態(tài),狀態(tài)機(jī)的輸出由當(dāng)前狀態(tài)決定。

2021-03-30 15:58:14 7

7 Synplify的優(yōu)勢之一是有限狀態(tài)機(jī)編譯器。 這是一個強(qiáng)大的功能,不僅具有自動檢測狀態(tài)機(jī)中的狀態(tài)的能力源代碼,并使用順序編碼,灰色編碼或一鍵編碼實(shí)現(xiàn)它們。但也要進(jìn)行可達(dá)性分析,以確定所有可能的狀態(tài)達(dá)到并優(yōu)化掉所有無法達(dá)到的狀態(tài)和轉(zhuǎn)換邏輯。因此,產(chǎn)生狀態(tài)機(jī)的高度優(yōu)化的最終實(shí)現(xiàn)。

2021-04-07 09:20:51 12

12 競爭現(xiàn)象的組合電路中,當(dāng)某個變量發(fā)生變化的時候,比如說從 1 跳到 0,或者說從 0 跳到 1,如果真值表所描述的邏輯關(guān)系或者功能遭受到短暫的破壞,在輸出端出現(xiàn)一個不應(yīng)有的尖脈沖?毛刺,這種現(xiàn)象就叫?冒險(xiǎn)。 冒險(xiǎn)是由競爭造成的,

2021-06-13 16:56:00 15806

15806 “本文主要分享了在Verilog設(shè)計(jì)過程中狀態(tài)機(jī)的一些設(shè)計(jì)方法。 關(guān)于狀態(tài)機(jī) 狀態(tài)機(jī)本質(zhì)是對具有邏輯順序或時序順序事件的一種描述方法,也就是說具有邏輯順序和時序規(guī)律的事情都適用狀態(tài)機(jī)描述。狀態(tài)機(jī)

2021-06-25 11:04:43 2249

2249 玩單片機(jī)還可以,各個外設(shè)也都會驅(qū)動,但是如果讓你完整的寫一套代碼時,卻無邏輯與框架可言。這說明編程還處于比較低的水平,你需要學(xué)會一種好的編程框架或者一種編程思想!比如模塊化編程、狀態(tài)機(jī)編程、分層思想

2021-07-27 11:23:22 19223

19223

1. 前言 在數(shù)字電路課程中,老師在講組合邏輯的時候,一般都會講競爭與冒險(xiǎn)。sky當(dāng)時也聽的云里霧里,沒有想清楚如下問題: 1) 競爭與冒險(xiǎn)究竟是什么東西?有啥物理現(xiàn)象? 2) 在數(shù)

2021-08-09 14:43:08 2657

2657

以前寫狀態(tài)機(jī),比較常用的方式是用 if-else 或 switch-case,高級的一點(diǎn)是函數(shù)指針列表。最近,看了一文章《c語言設(shè)計(jì)模式–狀態(tài)模式(狀態(tài)機(jī))》(來源:embed linux

2021-12-16 16:53:04 7

7 今天還是更新狀態(tài)機(jī),狀態(tài)機(jī)基本是整個HDL中的核心,合理、高效地使用狀態(tài)機(jī),是數(shù)字電路中的重要技能。

2023-02-12 10:21:05 542

542 有限狀態(tài)機(jī)是由寄存器組和組合邏輯構(gòu)成的硬件時序電路,其狀態(tài)(即由寄存器組的1和0的組合狀態(tài)所構(gòu)成的有限個狀態(tài))只可能在同一時鐘跳變沿的情況下才能從一個狀態(tài)轉(zhuǎn)向另一個狀態(tài),究竟轉(zhuǎn)向哪一狀態(tài)還是留在原狀態(tài)不但取決于各個輸入值,還取決于當(dāng)前所在狀態(tài)。這里是指Mealy型有限狀態(tài)機(jī)。

2023-04-07 09:52:46 909

909 和序列要求的最佳方法則是使用狀態(tài)機(jī)。狀態(tài)機(jī)是在數(shù)量有限的狀態(tài)之間進(jìn)行轉(zhuǎn)換的邏輯結(jié)構(gòu)。一個狀態(tài)機(jī)在某個特定的時間點(diǎn)只處于一種狀態(tài)。但在一系列觸發(fā)器的觸發(fā)下,將在不同狀態(tài)間進(jìn)行轉(zhuǎn)換。理論上講,狀態(tài)機(jī)可以分為Moore 狀態(tài)機(jī)和Mealy 狀態(tài)機(jī)

2023-07-18 16:05:01 499

499

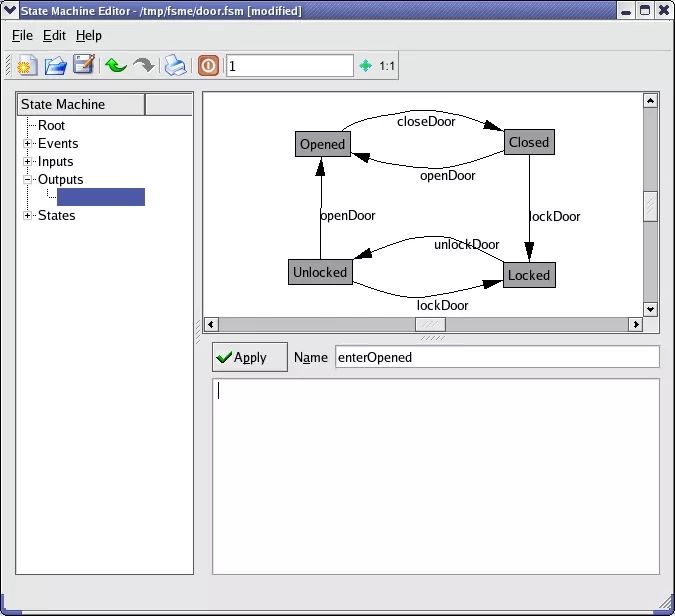

本身相關(guān)的那些處理邏輯。在FSME中,與具體應(yīng)用相關(guān)的操作稱為輸出(Output),它們實(shí)際上就是一些需要用戶給出具體實(shí)現(xiàn)的虛函數(shù),自動生成的狀態(tài)機(jī)引擎負(fù)責(zé)在進(jìn)入或者退出某個狀態(tài)時調(diào)用它們。 仍然以控制城門的那個狀態(tài)機(jī)為例

2023-09-13 16:57:37 821

821

門電路的兩個輸入信號同時向相反的邏輯電平跳變的現(xiàn)象叫做 競爭 ,這種競爭可能在電路的輸出端產(chǎn)生尖峰脈沖,這種現(xiàn)象稱為 競爭冒險(xiǎn) 。

2023-09-25 11:50:45 1080

1080

狀態(tài)機(jī),又稱有限狀態(tài)機(jī)(Finite State Machine,F(xiàn)SM)或米利狀態(tài)機(jī)(Mealy Machine),是一種描述系統(tǒng)狀態(tài)變化的模型。在芯片設(shè)計(jì)中,狀態(tài)機(jī)被廣泛應(yīng)用于各種場景,如CPU指令集、內(nèi)存控制器、總線控制器等。

2023-10-19 10:27:55 3405

3405

電子發(fā)燒友App

電子發(fā)燒友App

評論