1 主要芯片簡(jiǎn)介

1.1TMS320F2812 SPI模塊

SPI總線(xiàn)是一種同步串行外設(shè)接口,它可以使控制芯片以串行方式與各種外圍設(shè)備進(jìn)行通信。該接口一般使用4條線(xiàn):串行時(shí)鐘線(xiàn)(SCK)、主機(jī)輸入/從機(jī)輸出數(shù)據(jù)線(xiàn)MISO、主機(jī)輸出/從機(jī)輸入數(shù)據(jù)線(xiàn)MOSI和片選信號(hào)STE。

TMS320F2812的SPI模塊有主從兩種工作模式,可以通過(guò)寄存器來(lái)設(shè)置(其數(shù)據(jù)長(zhǎng)度可以配置為1~16位,具有125種可編程的波特率);通過(guò)時(shí)鐘極性和時(shí)鐘相位可以將SPI模塊配置成4種不同的時(shí)鐘模式;有16級(jí)發(fā)送/接收FIFO,并且具有延時(shí)發(fā)送的功能,可以通過(guò)中斷或者查詢(xún)的方式來(lái)完成數(shù)據(jù)的發(fā)送和接收。

SPI模塊有8個(gè)寄存器需要設(shè)置,用來(lái)控制SPI的操作:SPICCR、SPICTL用來(lái)配置SPI的工作狀態(tài);SPISTS用來(lái)獲取SPI的狀態(tài)信息,包括2個(gè)接收狀態(tài)位和1個(gè)發(fā)送緩沖狀態(tài)位,可以通過(guò)查詢(xún)這些狀態(tài)位來(lái)判斷是否完成數(shù)據(jù)的接收或者發(fā)送;SPIBRR用來(lái)設(shè)置SPI的波特率;SPIRXBUF和SPITXBUF分別用來(lái)接收和發(fā)送數(shù)據(jù);SPIDAT裝載SPI要發(fā)送的數(shù)據(jù),SPIPRI用來(lái)設(shè)置SPI中斷的優(yōu)先級(jí)。

1.2EEPROM芯片25LC040

25LC040是SPI接口的4 Kb EEPROM,至少可以擦寫(xiě)1 000萬(wàn)次,數(shù)據(jù)至少可以保存200年,可以滿(mǎn)足大部分?jǐn)?shù)據(jù)存儲(chǔ)的要求。DSP必須能通過(guò)相應(yīng)的指令實(shí)現(xiàn)對(duì)25LC040的訪(fǎng)問(wèn)。25LC040的操作指令如表1所列。

表1中,A8是讀/寫(xiě)開(kāi)始地址的第9位。25LC040是512×8位的EEPROM,分成上下兩頁(yè),每頁(yè)256個(gè)字節(jié),通過(guò)選擇A8可以實(shí)現(xiàn)對(duì)不同頁(yè)的操作。

1.2.1讀時(shí)序

當(dāng)片選信號(hào)為低時(shí),向25LC040傳送8位的讀指令(0000 A8011),緊接著傳送需要讀取數(shù)據(jù)的低8位地址。當(dāng)正確的讀寫(xiě)指令和地址被識(shí)別后,EEPROM中對(duì)應(yīng)地址的數(shù)據(jù)將會(huì)由輸出引腳順次傳出,若繼續(xù)提供時(shí)鐘信號(hào),下一位地址對(duì)應(yīng)的數(shù)據(jù)也會(huì)依次讀出。當(dāng)片選信號(hào)為高時(shí),讀數(shù)據(jù)的操作將會(huì)被終止。其具體操作如圖1所示。圖中,CS為片選信號(hào),SCK為時(shí)鐘信號(hào),SI為輸入引腳信號(hào),SO為輸出引腳信號(hào)。

1.2.2寫(xiě)時(shí)序

在對(duì)25LC040進(jìn)行任何寫(xiě)操作之前,必須先執(zhí)行WREN(寫(xiě)使能)指令。寫(xiě)使能指令的操作如圖2所示。先使片選信號(hào)為低,然后傳送寫(xiě)使能指令到25LC040中,指令傳送完畢后,必須將片選信號(hào)設(shè)置為高以完成寫(xiě)使能操作。如果寫(xiě)指令傳送結(jié)束后沒(méi)有拉高片選信號(hào),直接進(jìn)行寫(xiě)操作,那么數(shù)據(jù)將不會(huì)寫(xiě)入到存儲(chǔ)陣列中。

寫(xiě)使能操作完成后,片選信號(hào)應(yīng)該被拉低以進(jìn)行寫(xiě)操作,時(shí)序如圖3所示。寫(xiě)指令、寫(xiě)入地址以及寫(xiě)入的數(shù)據(jù)會(huì)被依次傳送到25LC040中。若要使數(shù)據(jù)正確地寫(xiě)入到存儲(chǔ)陣列中,片選信號(hào)應(yīng)該在最后一個(gè)有效字節(jié)的D0位傳送完畢后被拉高。

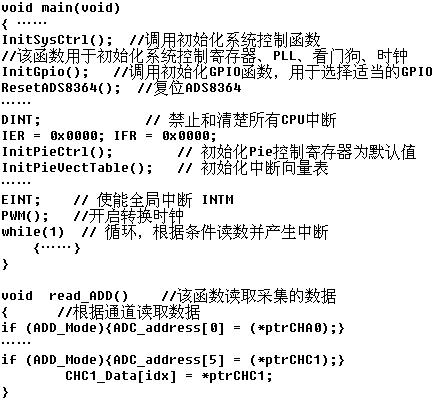

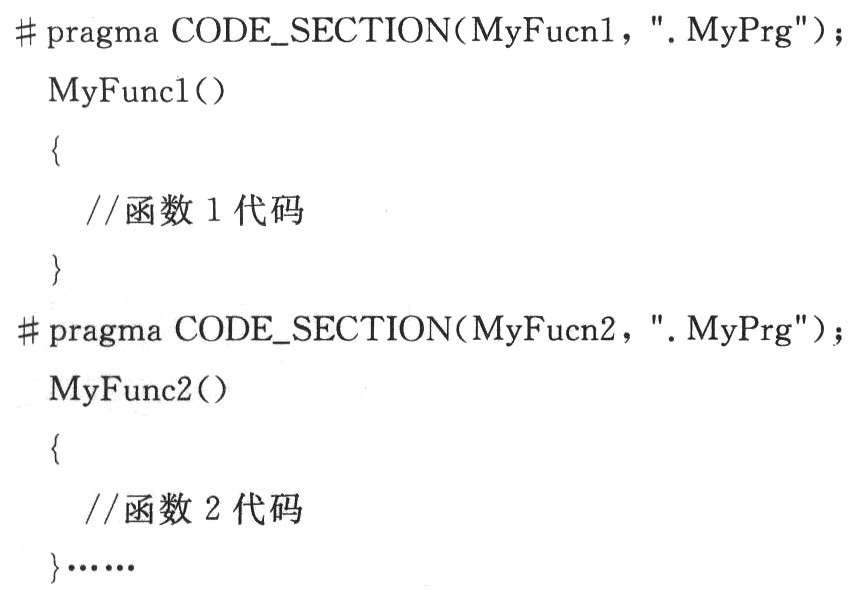

2 TMS320F2812的SPI接口設(shè)計(jì)

TMS320F2812與25LC040的硬件連接如圖4所示。TMS320F2812工作在主模式,SPISIMO為主模式下的數(shù)據(jù)輸出接口,連接到25LC040的數(shù)據(jù)接收端口;SPISOMI為主模式下的數(shù)據(jù)輸入接口,連接到25LC040的數(shù)據(jù)發(fā)送端口;時(shí)鐘信號(hào)SPICLK和片選信號(hào)SPISTE均由TMS320F2812產(chǎn)生。寫(xiě)保護(hù)引腳WP直接接高電平以確保25LC040總是可以被寫(xiě)入。

2.1 SPI模塊的設(shè)置

SPI模塊的波特率可由如下兩種情況計(jì)算得出:

①SPIBRR=3~127,波特率的計(jì)算公式為:

SPI波特率=LSPCLK/(SPIBRR+1)

②SPIBRR=0~2,波特率的計(jì)算公式為:

SPI波特率=LSPCLK/4

LSPCLK是TMS320F2812的低速外設(shè)時(shí)鐘頻率;SPIBRR是SPIBRR寄存器的值。將LSPCLK設(shè)置成37.5 MHz,25LC040的最大時(shí)鐘頻率為2 MHz,SPI的波特率應(yīng)該小于2 MHz,即37.5/(SPIBRR+1)≤2,SPIBRR的取值范圍為SPIBRR≥18。

通信中將SPISIMO、SPISOMI和SPICLK設(shè)置為基本功能SPI口,SPISTE設(shè)置為一般I/O口。作為25LC040的片選信號(hào),當(dāng)主/從控制器進(jìn)行數(shù)據(jù)交換時(shí),SPISTE配置成低電平,數(shù)據(jù)傳輸結(jié)束后再配置成高電平。

TMS320F2812的數(shù)據(jù)寄存器都是16位的,且接收和發(fā)送都是雙緩沖的,而25LC040的地址和數(shù)據(jù)寄存器都是8位的,因此將SPI模塊的數(shù)據(jù)長(zhǎng)度設(shè)置成8位。發(fā)送緩沖寄存器SPITXBUF中的數(shù)據(jù)以左對(duì)齊的方式發(fā)送,先發(fā)送數(shù)據(jù)的最高位,因此在發(fā)送數(shù)據(jù)前必須將等待發(fā)送的數(shù)據(jù)放在SPITXBUF的高8位。當(dāng)要對(duì)25LC040進(jìn)行寫(xiě)使能操作時(shí),寫(xiě)入SPITXBUF的數(shù)據(jù)應(yīng)為0x0600。TMS320F2812則是以右對(duì)齊的方式來(lái)接收數(shù)據(jù)的,8位的數(shù)據(jù)被放在SPITXBUF的低8位上。

SPI模塊有4種時(shí)鐘模式:上升沿?zé)o延時(shí)模式、上升沿有延時(shí)模式、下降沿?zé)o延時(shí)模式和下降沿有延時(shí)模式。25LC040是在時(shí)鐘的上升沿接收數(shù)據(jù),下降沿發(fā)送數(shù)據(jù),所以TMS320F2812的SPI應(yīng)該配置為上升沿發(fā)送數(shù)據(jù),下降沿接收數(shù)據(jù)。

2.2接收數(shù)據(jù)流程

通過(guò)SPI讀取數(shù)據(jù)比較簡(jiǎn)單,只需要依次傳送讀指令和待讀數(shù)據(jù)的低位地址,就可以在SPISOMI引腳上接收到25LC040中的數(shù)據(jù)。因?yàn)門(mén)MS320F2812為主控制器,所以必須先發(fā)送一個(gè)無(wú)意義的數(shù),才能夠啟動(dòng)時(shí)鐘。在SPI狀態(tài)寄存器(SPISTS)中有一個(gè)SPI中斷標(biāo)志位(SPIINT FLAG),該位是一個(gè)只讀標(biāo)志位,由硬件設(shè)置。當(dāng)SPI已經(jīng)完成數(shù)據(jù)發(fā)送或者接收,正在等待下一步的操作時(shí),SPI中斷標(biāo)志位被置1,若使能SPI中斷,將產(chǎn)生一個(gè)SPI中斷請(qǐng)求。可以通過(guò)查詢(xún)SPI中斷標(biāo)志位來(lái)判斷數(shù)據(jù)是否完成接收。若該標(biāo)志為1,已接收的數(shù)據(jù)將被放入接收緩沖寄存器SPIRXBUF中,通過(guò)讀SPIRXBUF寄存器即可得到需要的數(shù)據(jù)。下面給出接收數(shù)據(jù)的子程序,其中addr為待讀數(shù)據(jù)的低位地址。

2.3發(fā)送數(shù)據(jù)流程

SPI發(fā)送數(shù)據(jù)需要先完成寫(xiě)使能操作,然后依次傳送寫(xiě)指令和低位地址,才可以正確地進(jìn)行數(shù)據(jù)寫(xiě)入。向SPITXBUF寄存器中寫(xiě)入待發(fā)的數(shù)據(jù),SPI時(shí)鐘就會(huì)自動(dòng)啟動(dòng),數(shù)據(jù)會(huì)由輸出引腳順次傳出;數(shù)據(jù)傳送完后,SPI時(shí)鐘自動(dòng)停止。也可以通過(guò)查詢(xún)SPI中斷標(biāo)志位來(lái)判斷數(shù)據(jù)是否完成發(fā)送,若該標(biāo)志位為1,則可接著發(fā)送下一個(gè)數(shù)據(jù)。SPI設(shè)置成主模式時(shí),發(fā)送完一個(gè)數(shù)據(jù),必須要空讀一下SPIRXBUF寄存器,以清除SPI中斷標(biāo)志位。由于在讀取數(shù)據(jù)的過(guò)程中已經(jīng)包含讀SPIRXBUF寄存器,因此在讀取數(shù)據(jù)時(shí)不需要再空讀SPIRXBUF寄存器。下面給出發(fā)送數(shù)據(jù)程序,其中data為待發(fā)送的數(shù)據(jù),addr為待發(fā)送數(shù)據(jù)將要存放的地址。

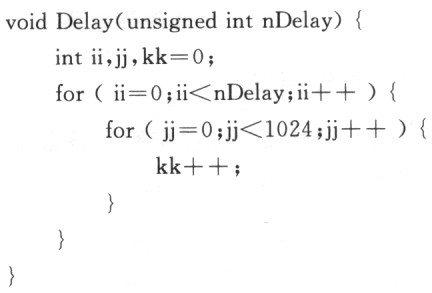

2.4運(yùn)行效率的提升

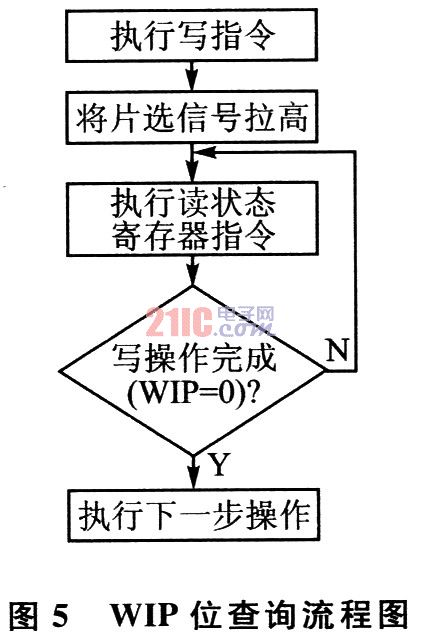

25LC040要求在寫(xiě)操作之后有一定的寫(xiě)周期時(shí)間來(lái)存儲(chǔ)數(shù)據(jù),其間TMS320F2812對(duì)25LC040的所有訪(fǎng)問(wèn)會(huì)被忽略。每個(gè)器件都有規(guī)定的最壞情況寫(xiě)周期時(shí)間,可以通過(guò)在再次訪(fǎng)問(wèn)25LC040之前插入不小于最壞情況寫(xiě)周期時(shí)間的延時(shí)等待來(lái)確保遵守寫(xiě)周期時(shí)間。但是25LC040常常會(huì)在最大規(guī)定時(shí)間內(nèi)完成寫(xiě)周期,而此時(shí)TMS320F2812還在等待,會(huì)造成不必要的時(shí)間浪費(fèi)。25LC040內(nèi)部有一個(gè)狀態(tài)寄存器,其第1位為WIP(Write-In-Process)位,該位是一個(gè)只讀位,可以顯示25LC040是否處在寫(xiě)周期內(nèi)。當(dāng)芯片處于寫(xiě)周期時(shí),WIP位置1;當(dāng)寫(xiě)操作完成時(shí),WIP位立即清零。狀態(tài)寄存器在寫(xiě)操作期間仍然可讀,可以通過(guò)讀狀態(tài)寄存器指令(WRSR)來(lái)獲取狀態(tài)寄存器的內(nèi)容,從而得到WIP位的值以判斷寫(xiě)周期何時(shí)完成,以進(jìn)入下一步操作。這樣就可以減少不必要的等待時(shí)間,使運(yùn)行更加高效。具體的流程如圖5所示。

結(jié)語(yǔ)

本文在分析TMS320F2812 SPI模塊的特點(diǎn)的基礎(chǔ)上,描述了SPI各個(gè)控制寄存器的作用。通過(guò)與EEPROM25LC040通信的實(shí)例,給出了SPI口的軟硬件設(shè)計(jì)方法,并對(duì)其中需要注意的關(guān)鍵問(wèn)題進(jìn)行了分析討論。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論