本文以解讀AXI協(xié)議中的多交易操作部分為目的而展開介紹,首先介紹了AXI協(xié)議基本概念中與多交易操作相關(guān)的概念,之后對多交易操作所涉及的“outstanding”、“out of order”和“interleaving”等重要概念做了基本解讀。

1、AXI基本概念

基本互聯(lián)結(jié)構(gòu)

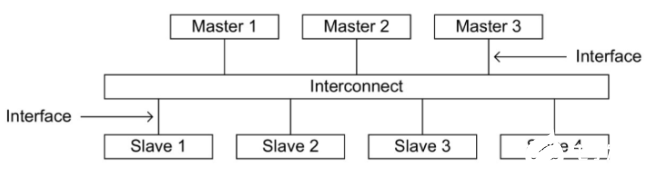

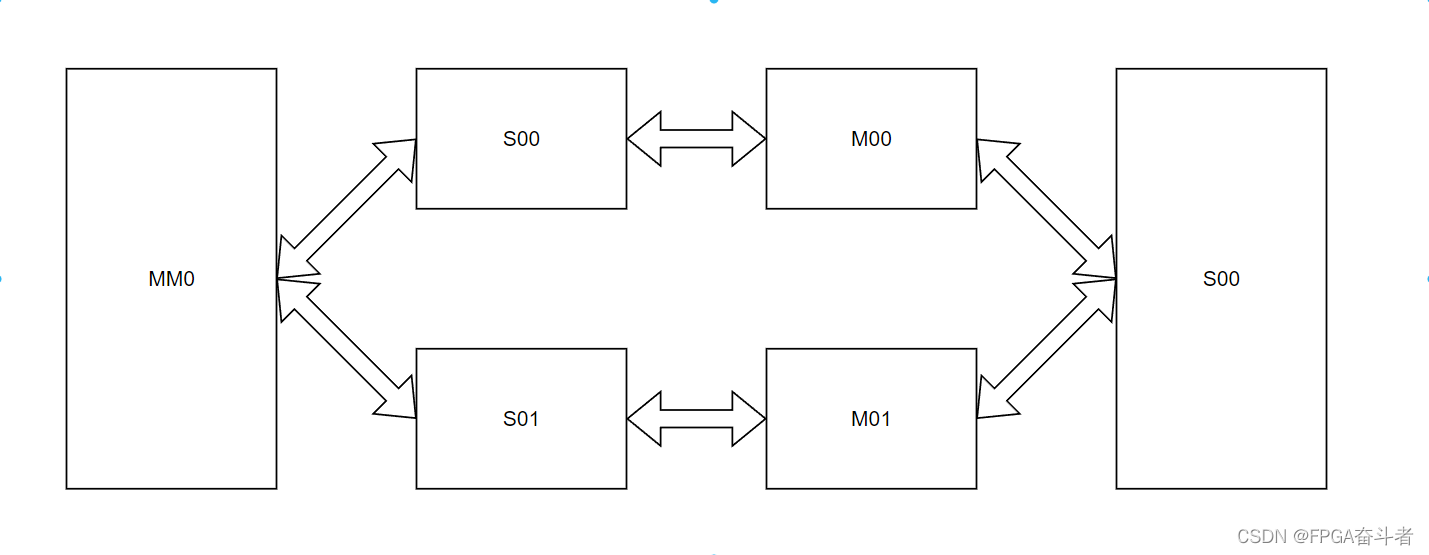

AXI總線系統(tǒng)由Master、Slave和Interconnect等基本器件搭建而成,器件間的互聯(lián)方式如下圖所示:

通道分離

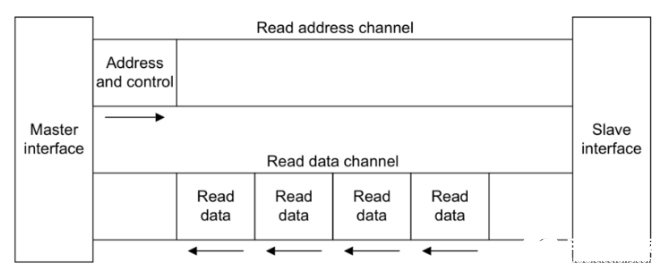

AXI協(xié)議定義了5個獨立的通道,每個通道通過VALID和READY信號完成握手機制。 五個通道分別為:讀地址通道、讀數(shù)據(jù)通道、寫地址通道、寫數(shù)據(jù)通道和寫響應(yīng)通道。 讀交易通道結(jié)構(gòu)如下圖所示:

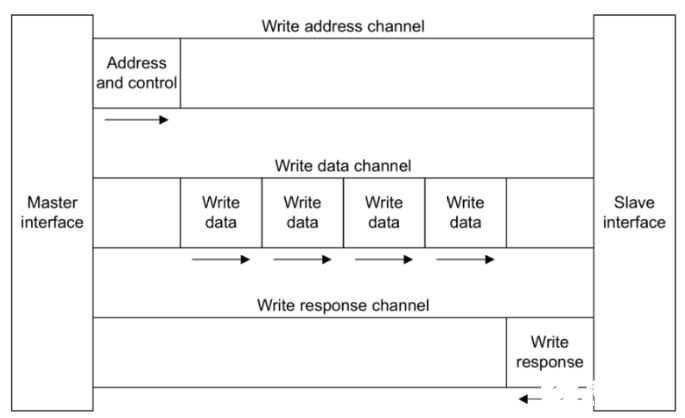

寫交易通道結(jié)構(gòu)如下圖所示:

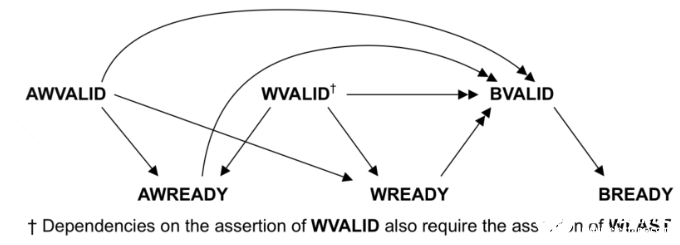

讀寫交易中握手信號的依賴關(guān)系

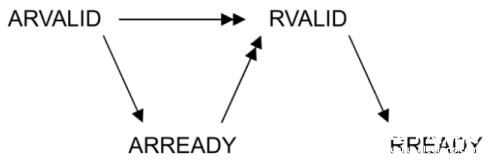

讀交易中握手信號的依賴關(guān)系如下圖所示:

寫交易中握手信號的依賴關(guān)系如下圖所示:

注:單箭頭指向的信號可以在指向它的信號未使能或使能后,它再使能;雙箭頭指向的信號必須在指向它的信號全都使能后,它再使能。

獨立的交易ID

通過接口的每次交易都有一個ID標(biāo)簽且五個通道均具備傳遞ID標(biāo)簽的能力。

2、多交易中的“out of order”概念

“out of order”即亂序傳輸。

協(xié)議基本規(guī)定

在猝發(fā)讀模式中,相同交易ID的Slave應(yīng)依據(jù)地址發(fā)送順序返回對應(yīng)讀數(shù)據(jù); 在猝發(fā)寫模式中,相同交易ID的Master應(yīng)依據(jù)地址發(fā)送順序發(fā)送對應(yīng)寫數(shù)據(jù); 不同ID的交易間,不同交易的讀寫命令與命令對應(yīng)的讀寫數(shù)據(jù)間無順序限制。

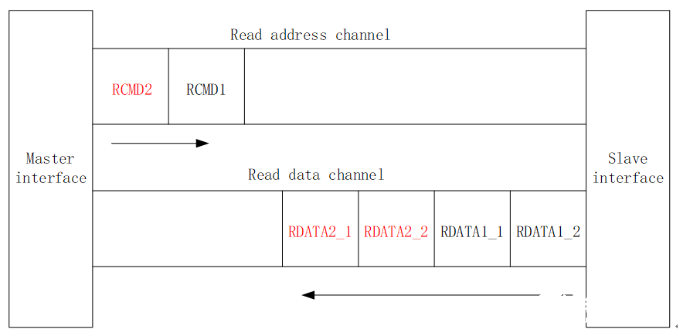

亂序傳輸?shù)氖疽獍咐?/p>

二猝發(fā)的讀交易亂序傳輸示意圖如下圖所示: (其中Master先發(fā)出讀命令RCMD1,后發(fā)出讀命令RCMD2,但Slave先返回了RCMD2對應(yīng)的讀數(shù)據(jù)RDATA2_1和RDATA2_2)

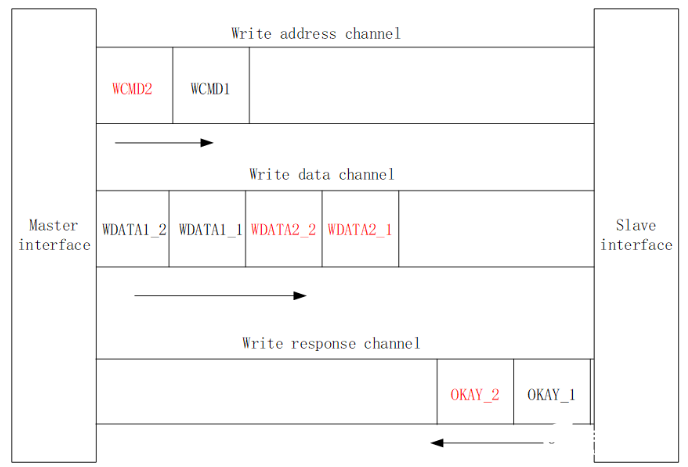

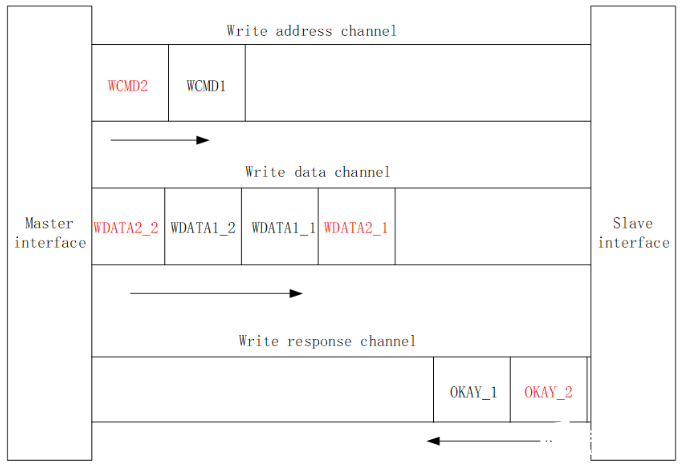

二猝發(fā)的寫交易亂序傳輸示意圖如下圖所示: (其中Master先發(fā)出寫命令WCMD1,后發(fā)出寫命令WCMD2,但Master先發(fā)出了寫命令WCMD2對應(yīng)的寫數(shù)據(jù)WDATA2_1和WDATA2_2)

亂序傳輸?shù)膬?yōu)勢

“out of order”技術(shù)保證響應(yīng)較快的存儲區(qū)域不必等待響應(yīng)較慢的存儲區(qū)域,降低了交易延時,從而提高了系統(tǒng)性能表現(xiàn)。

3、多交易中的“interleaving”概念

“interleaving”即交錯傳輸。

協(xié)議基本規(guī)定

在猝發(fā)讀模式中,不同交易ID的Slave返回數(shù)據(jù)間允許交錯傳遞; 在猝發(fā)寫模式中,不同交易ID的Master寫入數(shù)據(jù)間允許交錯傳遞。(此項只在AXI3協(xié)議中生效)

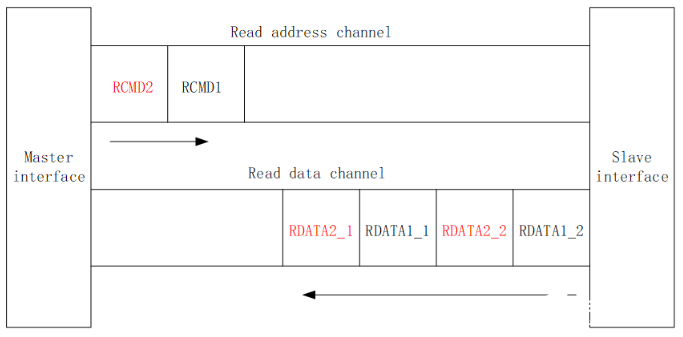

交錯傳輸?shù)氖疽獍咐?/p>

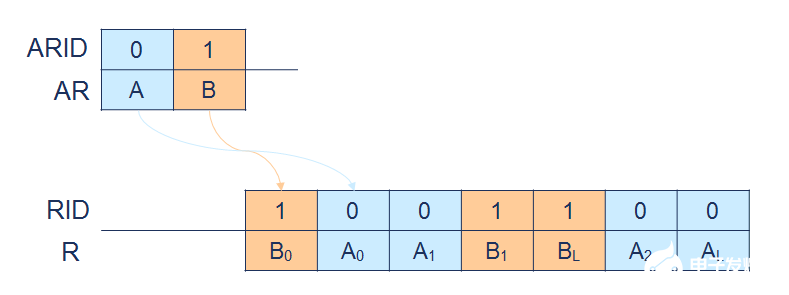

二猝發(fā)的讀交易交錯傳輸示意圖如下圖所示: (其中Master先后發(fā)出讀命令RCMD1和RCMD2,Slave依據(jù)時間先后,交錯返回了RDATA2_1、RDATA1_1、RDATA2_2、RDATA1_2等讀數(shù)據(jù))

二猝發(fā)的寫交易交錯傳輸示意圖如下圖所示: (其中Master先后發(fā)出寫命令WCMD1和WCMD2,Master依據(jù)時間先后,交錯寫入了WDATA2_1、WDATA1_1、WDATA1_2、WDATA2_2等寫數(shù)據(jù))

交錯傳輸?shù)膬?yōu)勢

在讀交易下,“interleaving”技術(shù)保證了不同響應(yīng)狀況的Slave在傳遞讀數(shù)據(jù)時能最大化利用互聯(lián)帶寬; 在寫交易下,當(dāng)Master單此猝發(fā)傳輸?shù)膶憯?shù)據(jù)來自速度不同的存儲單元時,“interleaving”技術(shù)能夠提升互聯(lián)帶寬的利用率。

4、多交易中的“outstanding”概念

“outstanding”即待處理的傳輸。

協(xié)議基本規(guī)定

AIX總線系統(tǒng)支持同時發(fā)布多個未完成的交易地址。

待處理傳輸?shù)膬?yōu)勢

“outstanding”技術(shù)意味著Masters可以不需等待上一交易完成便可發(fā)布交易地址,因而使能了總線系統(tǒng)平行處理多個交易的能力,進而提高了系統(tǒng)性能。

=============================================================================

AXI事務(wù)ID與outstanding/out of oreder/interleaving實現(xiàn)關(guān)系

前言

眾所周知,AXI3/AXI4支持outstanding/out of order/ interleaving的特性,但是這一特性是根據(jù)AXI哪一路實現(xiàn)的,以及需要注意和說明的地方是什么。

here is the analysis.

超前傳輸 outstanding的實現(xiàn)

outstanding是什么

outstanding表示AXI超前傳輸?shù)奶匦裕硎具@筆transaction還沒完成,可以先提起別的事務(wù),這么說如果抽象的話,那么就是AR/AWchannel可以提起多個事物,即便在W/R channel數(shù)據(jù)還沒發(fā)完或者還沒發(fā)的情況下。

超前傳輸是如何實現(xiàn)的?

在不考慮其他兩個特性(亂序和交織)的情況下,AXI事務(wù)都是順序完成的,這時多事務(wù)在途不需要其他信號來實現(xiàn),直接根據(jù)write channel或者read channel的LAST信號或者response channel的信號來判斷分割事務(wù)就可以了。可以認(rèn)為是一種隊列或FIFO結(jié)構(gòu),AR/AWchannel發(fā)起事務(wù)就是順序壓入隊列,當(dāng)這些事務(wù)對應(yīng)完成的時候,就最提起事務(wù)先彈出隊列,表示結(jié)束,然后接收完成后面的事務(wù)。

超前傳輸?shù)目芍С中?/p>

超前傳輸需要master和slave都支持超前傳輸,其中outstanding depth表示了主機超前傳輸?shù)男阅埽硎就粫r刻最多支持多少個AXI 事務(wù)在途。

如果slave不支持outstanding如何響應(yīng)?

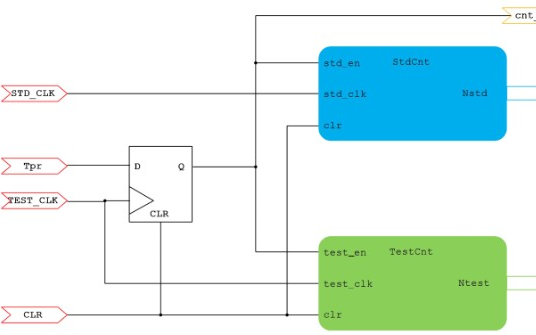

AXI 從機可選地支持超前傳輸,假設(shè)從機不支持超前傳輸,只需要在接收到 Trans0 后,置低 AxREADY 信號,阻止主機超前傳輸。在返回讀數(shù)據(jù)后,再置高 AxREADY 信號,接收下一事務(wù)。如下圖所示,主機將 Trans1 保持在總線上直至從機接收。

亂序 out of order的實現(xiàn)

out of order亂序是什么?

當(dāng)有多個事務(wù)在途的時候,有的事務(wù)可能先準(zhǔn)備好,因此可以先發(fā)送在總線上。那就需要面對一個問題,如何判斷返回的是哪個事務(wù)的數(shù)據(jù)?這就與AXI的事務(wù)ID有關(guān)

AXI的事務(wù)ID

AXI的事務(wù)ID包含了:

AWID

WID (只有AXI3有,AXI4沒有,因此不支持寫交織)

BID

ARID

RID

AXI out of order亂序的實現(xiàn)模型與思路

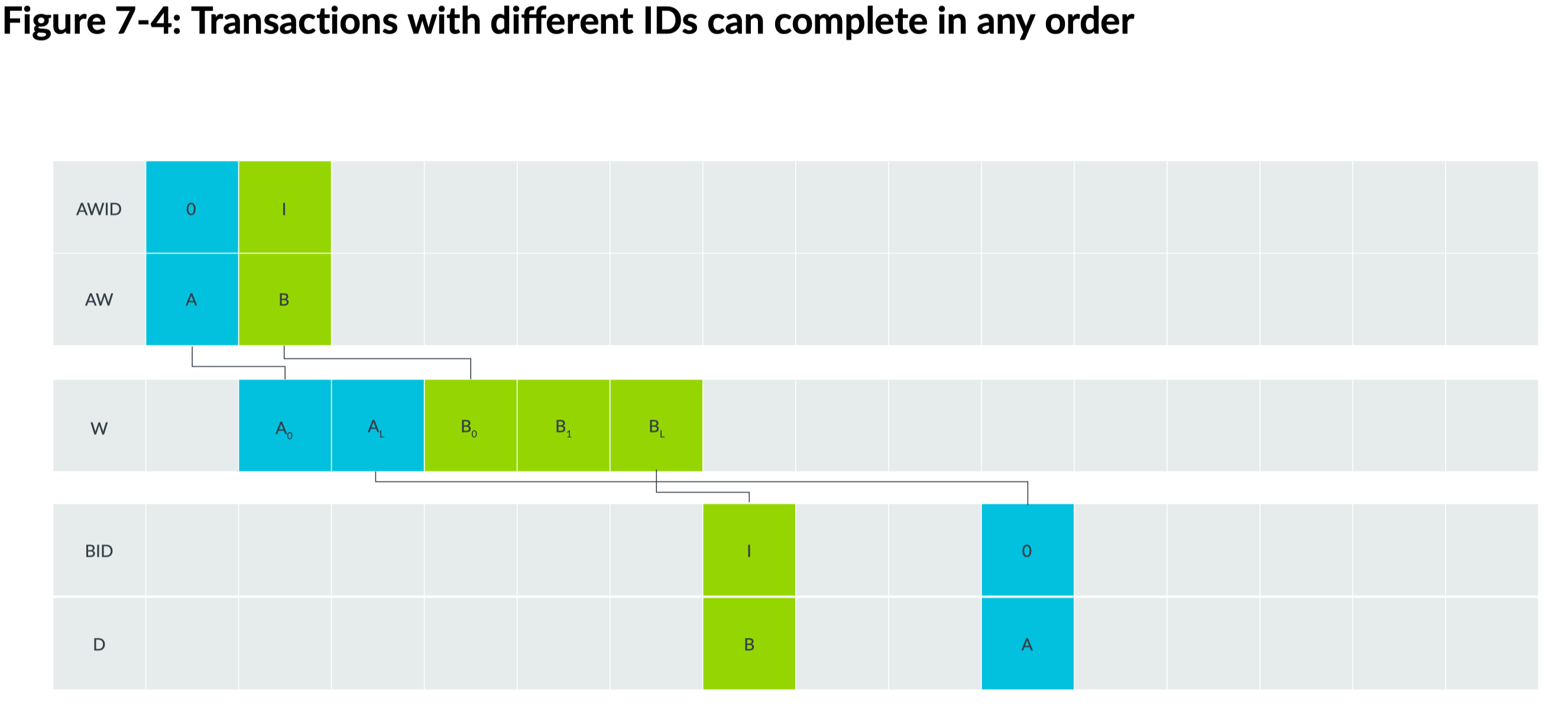

AXI亂序的特性是由地址channel和響應(yīng)channel上的ID信號AWID/ARID和WID/RID來實現(xiàn)的,根據(jù)ID不同來標(biāo)識事務(wù)不同,但是并不代表不同事務(wù)傳輸AWID/ARID就已經(jīng)要不同

不同事務(wù)的AxID如果一致,那么這些事務(wù)就不能實現(xiàn)out of order,只能進行順序完成。(因此需要重排序模型,重排序模型包括了事務(wù)緩沖區(qū)和數(shù)據(jù)緩沖區(qū),事務(wù)緩沖區(qū)存放在途需要完成的事務(wù),對于slave來說,其可能對于不同事務(wù)完成的時間不同,因此事務(wù)準(zhǔn)備好了與事務(wù)緩沖區(qū)的首個事務(wù)比較,如果匹配就輸出,如果不匹配就進入數(shù)據(jù)緩沖區(qū))

如果不同事務(wù)AxID不同,那么這些事務(wù)之間可以亂序。那么不同AxID事務(wù)的數(shù)據(jù),對于AXI讀來說,如何判斷返回的數(shù)據(jù)屬于哪個事務(wù)呢,是通過RID來進行匹配的,也就是說,在完成亂序傳輸?shù)臅r候,需要RID和ARID保持一致,以標(biāo)識不同事務(wù)的數(shù)據(jù)

那么對于實際情況來說,在實際傳輸中,可能有的事務(wù)AxID是不同的,有的是相同的,這是如何解決的?答:對于ID相同的就順序完成,對于ID不同的可以亂序。

在實際應(yīng)用中,在slave的實現(xiàn)中,為每個ARID準(zhǔn)備了一個事務(wù)緩沖區(qū)和數(shù)據(jù)緩沖區(qū),以支持相同ID和不同ID的數(shù)據(jù)順序傳輸和亂序傳輸。

有關(guān)于寫亂序

有一個重要的觀點,寫亂序不是針對于master來說的,說的不是不同事務(wù)發(fā)送的順序可以不一樣(即事務(wù)A先發(fā)起,事務(wù)B后發(fā)起,先發(fā)B事務(wù)的數(shù)據(jù)然后再發(fā)A事務(wù)的數(shù)據(jù),如此叫做亂序,這種觀點是錯誤的!)

寫亂序指的是:亂序是針對slave來說的,slave接收到了多個事務(wù)(可能是多個master傳輸來的事務(wù))那么slave返回BID的順序與發(fā)送過來的AWID順序是不同的,這叫做寫亂序,如圖所示,slave對于寫事務(wù)的完成(響應(yīng))可以是亂序的,稱之為寫亂序,寫亂序?qū)嶋H上指的是寫響應(yīng)亂序。

對應(yīng)寫事務(wù)亂序跟讀事務(wù)也是相同的

通過BID和AWID來表示數(shù)據(jù)所屬事務(wù)

AXI interleaving 交織的實現(xiàn)

什么是交織?

interleaving表示不同事務(wù)的數(shù)據(jù)可以被打散混合排列(但是注意,這里說的混合排列是不同事務(wù)間的,同一個是數(shù)據(jù)是不循序被打亂的)。例如事務(wù)1數(shù)據(jù)是0a 0b,事務(wù)2數(shù)據(jù)是1a 1b,如果不支持交織,那么總線上數(shù)據(jù)的傳輸需要是0a0b1a1b或者1a1b0a0b,如果支持交織的話那么就可以是0a1a0b1b(或者別的插入順序)

交織的實現(xiàn)

對于讀交織來說,讀事務(wù)的response方向和讀方向的相同的,不同事務(wù)交織是通過RID來進行識別的,也就是說RID在AXI傳輸中即起到了out of order亂序的不同事務(wù)識別也起到了interleaving交織中不同事務(wù)數(shù)據(jù)的識別

對于寫交織來說,由于寫方向和response方向不一樣,那么WID就是提供了寫交織的不同事務(wù)的識別,BID提供了亂序不同事務(wù)的識別。使用與 AWID 匹配的 BID 標(biāo)識寫回復(fù)所屬的事務(wù) ID。實際上從機給出寫回復(fù)可以類比讀事務(wù)中給出讀數(shù)據(jù)的過程。

總結(jié)

到此為止,介紹了AxID和RID/BID在AXI亂序交織中的作用。

審核編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評論