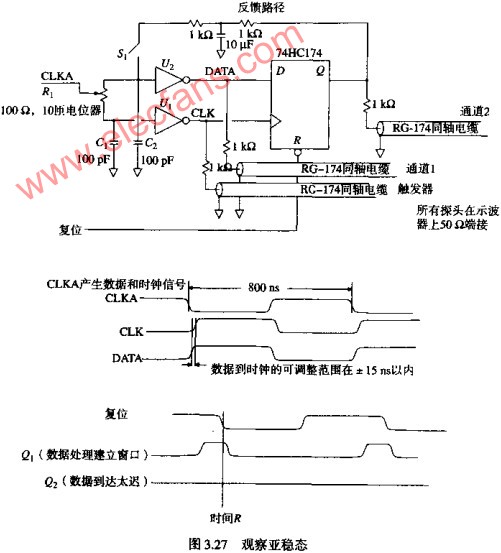

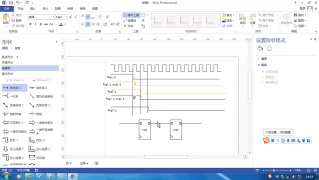

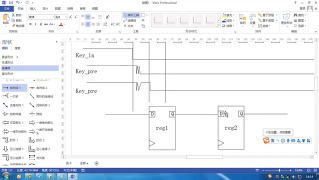

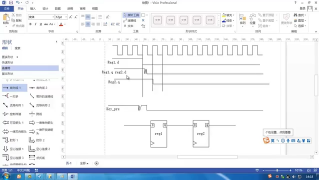

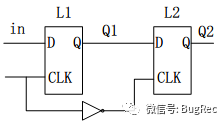

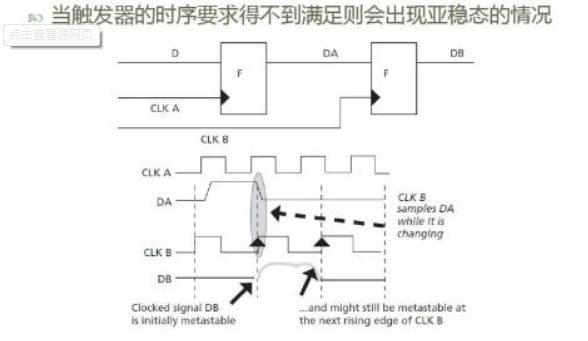

圖3.27所示的是一個(gè)觀察D觸發(fā)器亞穩(wěn)態(tài)的電路圖。使用這個(gè)電路至少需要一個(gè)雙通道示波器。

CLKA的波形是一個(gè)方波,通過R1與C1和C2的兩個(gè)支路被延遲。如果將R1的觸點(diǎn)向DATA輸出方向進(jìn)行調(diào)整,CLK的輸出延遲會達(dá)到最大值。如果將R1的觸點(diǎn)向CLK輸出的方向進(jìn)行調(diào)整,DATA的輸出延遲會達(dá)到最大值。DATA和CLK之間的相對位置的可調(diào)整范圍在正負(fù)15NS之間。

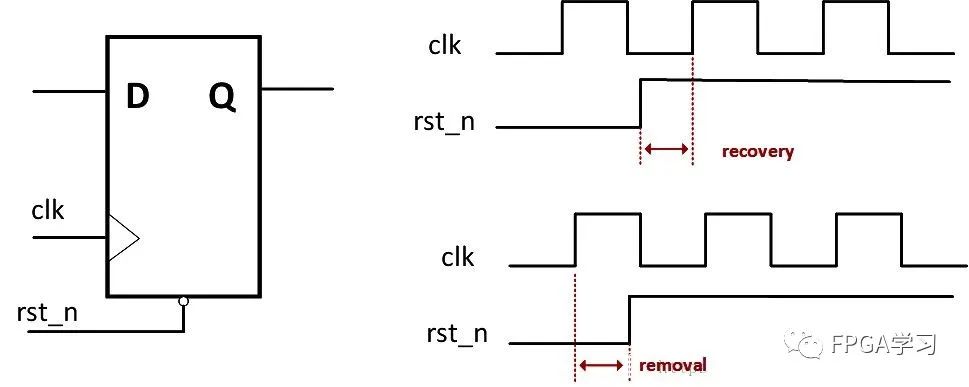

復(fù)位的波形在每個(gè)時(shí)鐘上升沿之后產(chǎn)生一個(gè)負(fù)電平有效的復(fù)位脈沖。這個(gè)復(fù)位信號使觸發(fā)器在每個(gè)周期到來之前是一個(gè)固定的狀態(tài)。可以用經(jīng)過延遲的時(shí)鐘信號作為復(fù)位信號。

圖3.27中的所有主要信號都用21:1的探頭通過1K的電阻連接。首先將示波器連接到DATA的CLK信號。

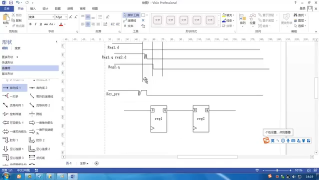

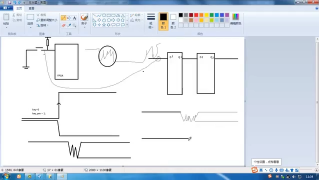

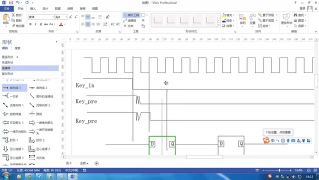

將反饋回路開關(guān)S1打開,并將電位器觸點(diǎn)逐漸由數(shù)據(jù)最小延遲變化到數(shù)據(jù)最大延遲。將DATA和CLK之間的時(shí)序關(guān)系相對于電位器的設(shè)置大致畫出一個(gè)草圖。將電位器進(jìn)行大范圍調(diào)整,并觀察得到的結(jié)果。在最小數(shù)據(jù)延遲時(shí),數(shù)據(jù)應(yīng)該在要求的最小上升時(shí)間之前到達(dá)。在最大數(shù)據(jù)延遲時(shí),數(shù)據(jù)應(yīng)該直到最小保持時(shí)間過去之后,才會變化。

計(jì)算一下電位器每一匝的變化得到的時(shí)延調(diào)整。

現(xiàn)在將示波器連接到CLK和Q。把DATA同軸電纜同一個(gè)50歐的電阻端接,這樣它的響應(yīng)就不會發(fā)生變化。使示波器通過CLK信號來觸發(fā),調(diào)整電位器,得到最小的數(shù)據(jù)延時(shí)。

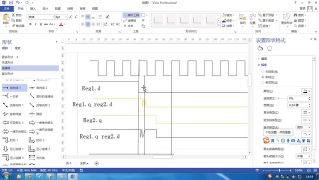

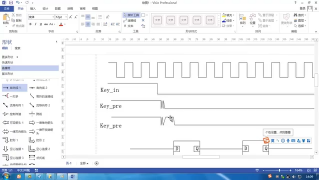

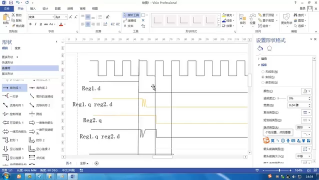

起初,D輸入端滿足建立時(shí)間的要求,而Q輸出的響應(yīng)波形如同Q1,如圖3.27所示,每個(gè)時(shí)鐘到來時(shí)Q輸出都變成高電平(HI),而每當(dāng)R時(shí)刻到來時(shí),Q輸出都被復(fù)位到低電平(。不要用時(shí)鐘的反相信號復(fù)位觸發(fā)器,否則由復(fù)位信號產(chǎn)生的電平變化會同來穩(wěn)態(tài)效果混在一起。

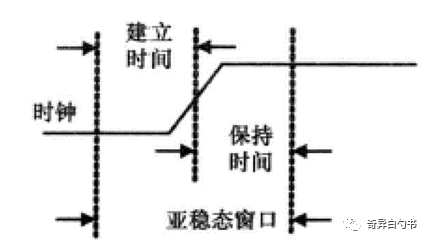

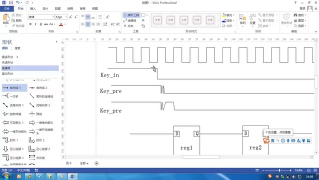

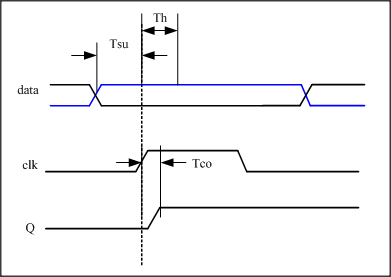

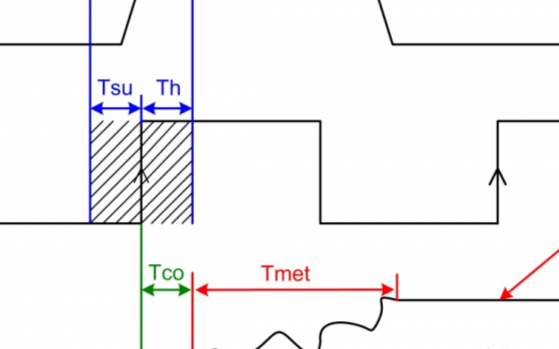

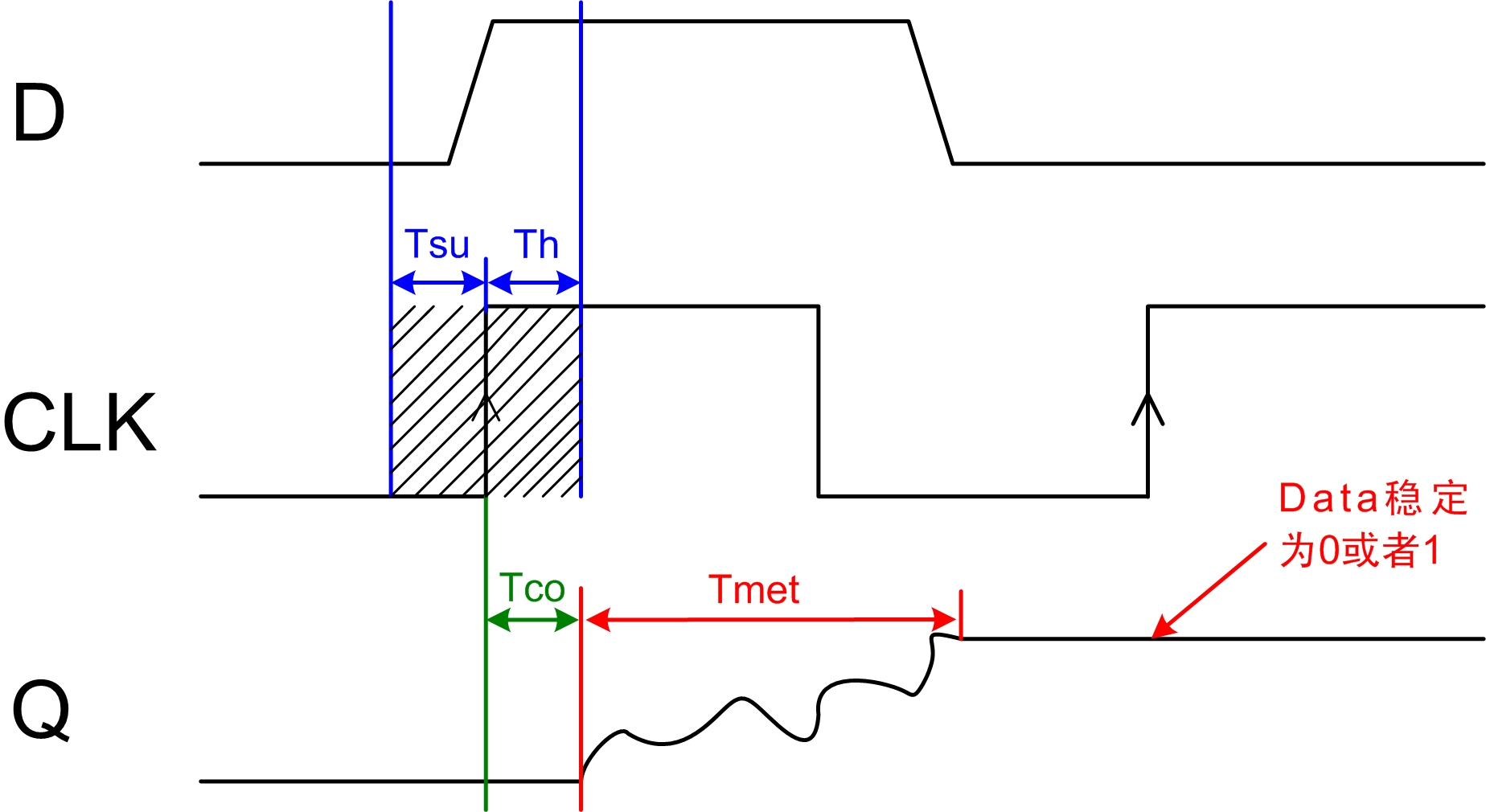

調(diào)整觸點(diǎn),使數(shù)據(jù)延遲,直到把它調(diào)到數(shù)據(jù)所需的最小建立時(shí)間窗口之后,在某一點(diǎn)時(shí),Q輸出會突然發(fā)生變化。這時(shí),數(shù)據(jù)到達(dá)的時(shí)間太晚了,Q輸出不會再轉(zhuǎn)換為HI,如同圖3.27所示的Q2一樣。觸發(fā)器不能在上升沿處鎖存D輸入的這個(gè)點(diǎn),稱為臨界轉(zhuǎn)換點(diǎn)。臨界轉(zhuǎn)換點(diǎn)位于觸發(fā)器生產(chǎn)商標(biāo)定的最小上升時(shí)間和保持時(shí)間之間。生產(chǎn)商會將這兩個(gè)值的標(biāo)定略加放寬,以保重在一個(gè)很大的溫度范圍之內(nèi),這個(gè)臨界轉(zhuǎn)換點(diǎn)都會落于這個(gè)限制之間。

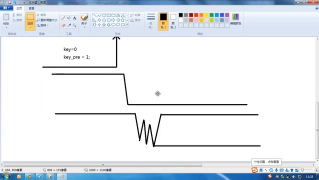

臨界轉(zhuǎn)換點(diǎn)之前到達(dá)的數(shù)據(jù)似乎總是可以被鎖存,臨界轉(zhuǎn)換點(diǎn)之后到達(dá)的數(shù)據(jù)似乎總是鎖存不到。這不是我們想要的嗎?沒錯(cuò),但我們必須進(jìn)一步理解亞穩(wěn)態(tài)問題的實(shí)質(zhì)。

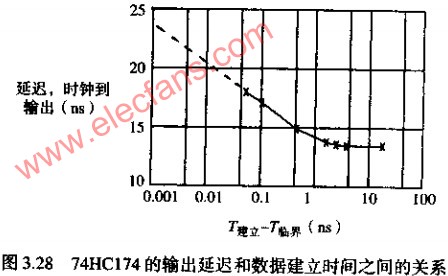

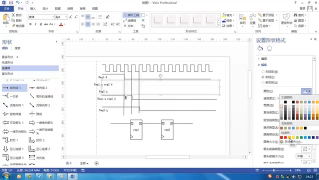

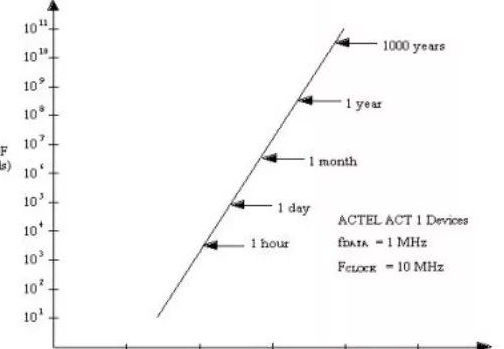

圖3.28繪出了由該電路得到的值,比較了觸發(fā)器時(shí)鐘到Q輸出的延遲與測量到的數(shù)據(jù)建立時(shí)間,在這個(gè)圖中,時(shí)間刻度用對數(shù)標(biāo)尺顯示了實(shí)際數(shù)據(jù)建立時(shí)間與臨界轉(zhuǎn)換點(diǎn)時(shí)間之間的差。無論何時(shí),當(dāng)數(shù)據(jù)在臨界轉(zhuǎn)換點(diǎn)3NS之前提前到達(dá)時(shí),時(shí)鐘到Q延遲總是保持13.5NS不變。當(dāng)數(shù)據(jù)向臨界轉(zhuǎn)換邊界移動時(shí),Q輸出仍然會變成高電平,但是時(shí)鐘到Q延遲會變長。當(dāng)數(shù)據(jù)到達(dá)時(shí)間非常接近臨界轉(zhuǎn)換點(diǎn)時(shí),Q延遲與數(shù)據(jù)上升時(shí)間與臨界轉(zhuǎn)換點(diǎn)之差的對數(shù)成正比。

該時(shí)鐘到輸出延遲的增加值是輸入信號建立時(shí)間的函數(shù),這種增加是亞穩(wěn)態(tài)特性的實(shí)質(zhì)。你不能在這個(gè)點(diǎn)附近工作,所有的觸發(fā)器都一樣,它會使高速同步設(shè)計(jì)遭到破壞。解決這個(gè)問題的最好方法是心量減少它的發(fā)生,但永遠(yuǎn)無法消除它。

時(shí)鐘到輸出延遲究竟通達(dá)到多大呢?這要看數(shù)據(jù)離臨界轉(zhuǎn)換點(diǎn)有多遠(yuǎn)。

電子發(fā)燒友App

電子發(fā)燒友App

評論