u-boot armv8鏈接腳本 在進(jìn)行源碼分析之前,首先看看u-boot的鏈接腳本,通過(guò)鏈接腳本可以從整體了解一個(gè)u-boot的組成,并且可以在啟動(dòng)分析中知道某些邏輯是在完成什么工作

2023-12-07 11:19:22 213

213 一、引言隨著電子技術(shù)的不斷發(fā)展,微控控制器(MCU)在各個(gè)領(lǐng)域的應(yīng)用越來(lái)越廣泛。其中,F(xiàn)T60F210-URT封裝SOT23-6處理器微控控制器MCU集成電路因其卓越的性能和廣泛的應(yīng)用范圍而備受關(guān)注

2023-11-27 21:11:26

汽車EE體系結(jié)構(gòu)中的功能域介紹

2023-11-15 11:37:40 167

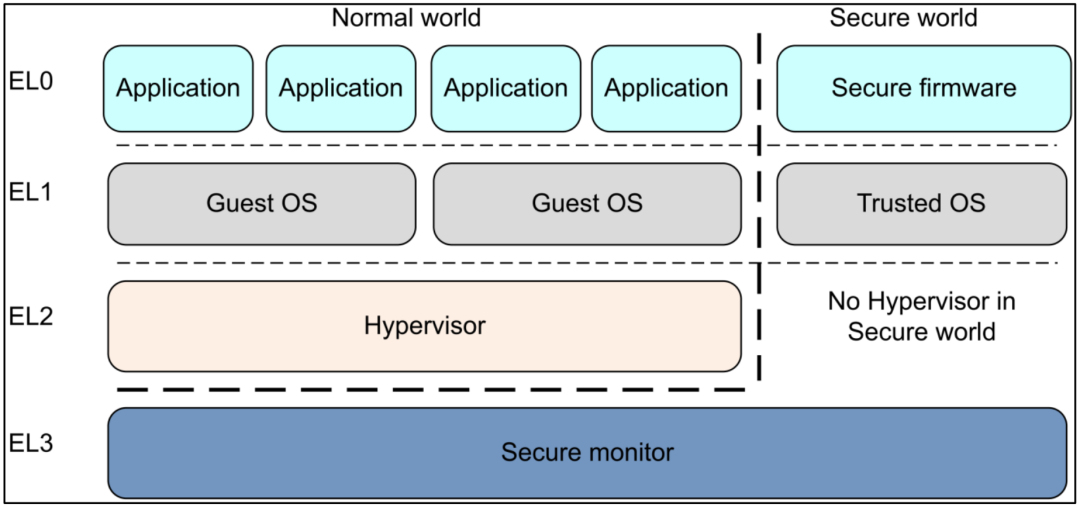

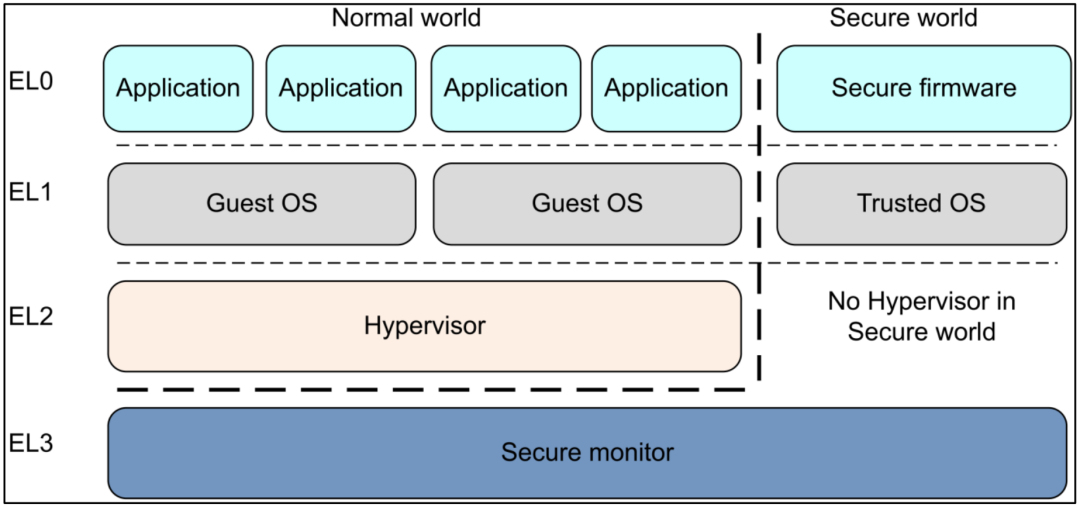

167 ),虛擬機(jī)管理器 EL3:最底層的安全固件,如 ARM Trusted Firmware(ATF/TF-A) ARMv8 提供了兩種安全狀態(tài):Secure 和 Non-secure,也就是安全和非安全,Non-secure 也就是正常

2023-09-11 16:34:29 634

634

本實(shí)驗(yàn)的目的是向您介紹意法半導(dǎo)體Cortex?-M3處理器,該處理器使用ARM?KEIL?MDK工具包,具有集成開(kāi)發(fā)環(huán)境μ?。

我們將在Keil MCBSTM32C評(píng)估板上使用串行線查看器(SWV

2023-09-04 08:01:31

本實(shí)驗(yàn)的目的是向您介紹意法半導(dǎo)體Cortex?-M4處理器,該處理器使用ARM?KEIL?MDK工具包,具有集成開(kāi)發(fā)環(huán)境μ?。

我們將使用串行線查看器(SWV)和板載ST-Link/V2調(diào)試適配器

2023-09-04 07:47:21

Cortex-M33 Cortex-M35P Cortex-M55 Cortex-M7 Cortex-M85指令集體系結(jié)構(gòu)ARMv6-M ARMv8-M基線ARMv7-M ARMv7-M ARMv8-

2023-08-29 07:00:04

此教程將概述使用 CoreSight Access 工具( CSAT) 進(jìn)行低級(jí)別調(diào)試的情況, 其目標(biāo)為 Armv8 。 低級(jí)別調(diào)試允許您操作單個(gè)登記器, 包括通常無(wú)法為應(yīng)用程序級(jí)別調(diào)試器訪問(wèn)

2023-08-28 06:28:31

ARM Cortex-M33處理器是第一款ARMv8-M處理器,旨在滿足嵌入式和物聯(lián)網(wǎng)市場(chǎng),特別是那些需要高效安全或數(shù)字信號(hào)控制的市場(chǎng)。

ARMv8-M引入了TrustZone,這構(gòu)成了嵌入式和物

2023-08-28 06:12:15

ARM Cortex-M55處理器是一款完全可合成的中端微控制器級(jí)處理器,實(shí)現(xiàn)了ARMv8.1-M主線架構(gòu),并支持M-Profile向量擴(kuò)展(MVE),也稱為ARM氦技術(shù)。

它是ARM最具人工智能

2023-08-25 07:46:47

本文檔描述了Cortex-R82微體系結(jié)構(gòu)的元素,這些元素會(huì)影響軟件性能,以便相應(yīng)地優(yōu)化軟件和編譯器。

微體系結(jié)構(gòu)細(xì)節(jié)僅限于對(duì)軟件優(yōu)化有用的細(xì)節(jié)。

文檔僅涉及Cortex-R82內(nèi)核的軟件可見(jiàn)行為,而不涉及該行為背后的硬件原理。

2023-08-25 06:56:57

Cortex-A72處理器是一款實(shí)現(xiàn)ARMv8-A架構(gòu)的高性能、低功耗處理器。

它在帶有L1和L2緩存子系統(tǒng)的單處理器設(shè)備中具有一到四個(gè)核心。

下圖顯示了四核Cortex-A72處理器配置的示例框圖。

2023-08-25 06:27:45

ARM Cortex-M7處理器是Cortex-M系列中性能最高的處理器,可用于設(shè)計(jì)復(fù)雜的MCU和SoC。

Cortex-M7提供業(yè)界領(lǐng)先的5.01核心標(biāo)記/MHz標(biāo)量性能,同時(shí)保持了ARMv

2023-08-25 06:25:54

ARM Cortex-M23處理器是一款非常緊湊的兩級(jí)流水線處理器,支持ARMv8-M基準(zhǔn)架構(gòu)。

配備TrustZone的Corest-M23是最受限制的物聯(lián)網(wǎng)和嵌入式應(yīng)用程序的理想處理器,這些

2023-08-25 06:19:14

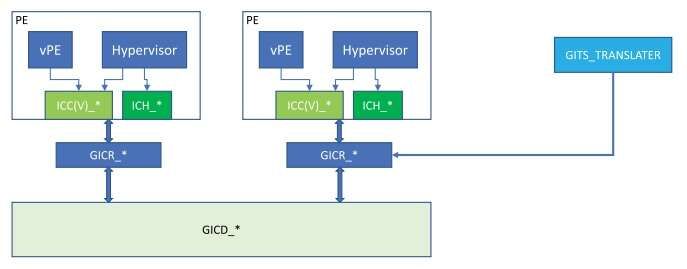

版(GICv2)的一些內(nèi)在限制,例如隨著系統(tǒng)規(guī)模的增加可擴(kuò)展性有限。

它還增加了幾個(gè)新功能。

例如,GICv2體系結(jié)構(gòu)規(guī)范將支持的處理器數(shù)量限制在最多8個(gè),而基于GICv3體系結(jié)構(gòu)規(guī)范的中斷控制器可以支持

2023-08-23 07:21:57

本文中,我們將研究采用氦技術(shù)的ARM Cortex-M55處理器與傳統(tǒng)DSP上的功能進(jìn)行比較的情況,以及VLIW(超長(zhǎng)指令字)體系結(jié)構(gòu)和氦方法在處理器流水線設(shè)計(jì)中的一些根本區(qū)別。

我們還將研究處理要求如何影響處理器的一級(jí)存儲(chǔ)系統(tǒng)設(shè)計(jì)和系統(tǒng)設(shè)計(jì)注意事項(xiàng)

2023-08-23 06:51:00

熟悉ARM軟件開(kāi)發(fā)。

它旨在幫助您編寫ARMv8-A處理器的引導(dǎo)代碼。

您可以參考本應(yīng)用筆記中的引導(dǎo)代碼示例,并為基于ARMv8-A處理器的裸機(jī)系統(tǒng)編寫自己的引導(dǎo)代碼。

2023-08-23 06:20:29

本文檔介紹ARMv8-A[ARMv8]的可伸縮向量擴(kuò)展[SVE]對(duì)在應(yīng)用程序處理器上以安全狀態(tài)執(zhí)行的軟件的影響。

本文檔考慮了部署現(xiàn)有ARMv8-A TrustZone軟件對(duì)實(shí)施SVE的系統(tǒng)的影響,并為實(shí)施SVE的系統(tǒng)更新該軟件和設(shè)計(jì)未來(lái)的安全軟件提供了建議

2023-08-23 06:17:45

ARMv8-A是針對(duì)應(yīng)用配置文件的最新一代ARM架構(gòu)。

在本書中,名稱ARMv8用于描述整個(gè)體系結(jié)構(gòu),它現(xiàn)在包括32位執(zhí)行狀態(tài)和64位執(zhí)行狀態(tài)。

ARMv8引入了使用64位寬寄存器執(zhí)行的能力,但提供

2023-08-22 07:22:29

rk3588是armv8嗎?rk3588 硬件資料 RK3588是一款高性能處理器,是Rockchip公司推出的最新芯片。本文將詳細(xì)介紹RK3588的硬件資料。 首先,我們需要了解一下RK3588

2023-08-21 17:32:46 1744

1744 ARM產(chǎn)品必須如何運(yùn)行的體系結(jié)構(gòu)規(guī)范。

此外,一些合作伙伴還授權(quán)實(shí)施符合架構(gòu)規(guī)范的自己的ARM處理器。

這導(dǎo)致了分層劃分為三個(gè)級(jí)別的規(guī)范,這些規(guī)范共同描述了整個(gè)SoC的行為和程序員模型

2023-08-21 07:28:01

近期關(guān)注了一下MA35D1處理器,剛才官網(wǎng)看了一下沒(méi)有看到相關(guān)的手冊(cè),只有相關(guān)介紹以及簡(jiǎn)述的接口,請(qǐng)問(wèn)有相關(guān)的資料鏈接文檔嘛?有的發(fā)一下,感謝!

2023-08-18 09:47:47

Cortex-R8處理器是一款用于深度嵌入式實(shí)時(shí)系統(tǒng)的中端處理器。

它實(shí)施ARMv7-R架構(gòu),并包括Thumb?-2技術(shù),以實(shí)現(xiàn)最佳代碼密度和處理吞吐量。

該流水線具有雙重算術(shù)邏輯單元(ALU

2023-08-18 08:28:22

Cortex?-M85處理器是一款完全可合成的高性能處理器,專為微控制器市場(chǎng)設(shè)計(jì)。

該處理器通過(guò)低功耗、快速中斷處理和具有廣泛斷點(diǎn)和跟蹤功能的可選增強(qiáng)型系統(tǒng)調(diào)試,在標(biāo)量和向量運(yùn)算中提供高計(jì)算性能

2023-08-18 07:59:40

Cortex-A34處理器以Verilog HDL語(yǔ)言描述的可合成寄存器傳輸級(jí)(RTL)形式交付。

在使用它之前,您必須實(shí)現(xiàn)、集成和編程它。

不同的參與方可以執(zhí)行以下每項(xiàng)任務(wù)。

每個(gè)任務(wù)都可以包括

2023-08-18 07:46:48

ARMv8-R標(biāo)準(zhǔn)的處理元件(PE)。

在Cortex-R52的背景下,PE和核心在概念上是相同的。

多個(gè)受保護(hù)的內(nèi)存系統(tǒng)架構(gòu)(PMSA)上下文可以在同一核上執(zhí)行,使用虛擬化技術(shù)來(lái)包含它們。

該處理器

2023-08-18 07:07:48

在本手冊(cè)中,以下術(shù)語(yǔ)指的是下面提供的描述。

核心A核心包括與數(shù)據(jù)處理單元、存儲(chǔ)系統(tǒng)和管理、電源管理以及核心級(jí)調(diào)試和跟蹤邏輯相關(guān)的所有邏輯。

在Cortex?-R82處理器環(huán)境中,CPU和內(nèi)核可以互換

2023-08-17 08:02:29

和糾正的糾錯(cuò)碼(ECC)功能在實(shí)現(xiàn)時(shí)包括在數(shù)據(jù)和指令高速緩存中。

Tcm接口支持實(shí)施外部ECC,以提供更高的可靠性并滿足與安全相關(guān)的應(yīng)用。

Cortex-M7處理器包括可選的浮點(diǎn)算術(shù)功能,支持單精度和雙精度算術(shù)。

請(qǐng)參見(jiàn)第8章浮點(diǎn)單元。

該處理器適用于需要快速中斷響應(yīng)功能的高性能、深度嵌入式應(yīng)用程序

2023-08-17 07:55:23

的代碼不能在缺乏這些功能的舊處理器上運(yùn)行。

在體系結(jié)構(gòu)的所有版本中,某些系統(tǒng)功能和行為都是由實(shí)現(xiàn)定義的。

例如,該體系結(jié)構(gòu)沒(méi)有為各個(gè)指令定義高速緩存大小或周期定時(shí)。

這些由各個(gè)處理器和SoC決定。

ARMv7架構(gòu)也有配置文件的概念。

這些是體系結(jié)構(gòu)的變體,描述了針對(duì)不同市場(chǎng)和用途的處理器。

2023-08-17 07:54:29

體系結(jié)構(gòu)是64位R-Profile ARM?體系結(jié)構(gòu),僅具有AArch64執(zhí)行狀態(tài)。

因此,Cortex?-R82處理器不支持AArch32執(zhí)行狀態(tài)。

Cortex?-R82處理器支持ARM?v8.4架構(gòu)

2023-08-17 07:45:14

Cortex-A8處理器是一款高性能、低功耗、高速緩存的應(yīng)用程序處理器,可提供完整的虛擬內(nèi)存功能。

該處理器的功能包括:

·完全實(shí)現(xiàn)ARM體系結(jié)構(gòu)v7-A指令集·具有高級(jí)可擴(kuò)展接口(AXI)的可配

2023-08-17 07:43:12

Cortex-A15 MPCore處理器是一款高性能、低功耗的多處理器,采用ARMv7-A架構(gòu)。

Cortex-A15 MPCore處理器在具有L1和L2緩存子系統(tǒng)的單個(gè)多處理器設(shè)備或MPCore設(shè)備中具有一到四個(gè)Cortex-A15處理器。

2023-08-17 07:37:22

Cortex-M23處理器是一款低門數(shù)、兩級(jí)和高能效處理器。

它適用于微控制器和深度嵌入式應(yīng)用,這些應(yīng)用需要在安全性是重要考慮因素的環(huán)境中使用區(qū)域優(yōu)化的低功耗處理器。

2023-08-17 07:28:12

Cortex?-M33處理器是一款低門數(shù)、高能效的處理器,適用于微控制器和深度嵌入式應(yīng)用。

該處理器基于ARM?V8-M架構(gòu),主要用于安全性非常重要的環(huán)境。

處理器支持的接口包括:

·Code

2023-08-17 07:23:50

Cortex-A5處理器是一款高性能、低功耗的ARM宏單元,具有提供完整虛擬內(nèi)存功能的一級(jí)高速緩存子系統(tǒng)。

Cortex-A5處理器實(shí)現(xiàn)了ARMv7架構(gòu),并在Jazelle狀態(tài)下運(yùn)行32位ARM指令、16位和32位Thumb指令以及8位JAVA?字節(jié)碼

2023-08-17 07:16:41

Cortex-A9處理器是一款高性能、低功耗的ARM宏單元,具有提供完整虛擬內(nèi)存功能的一級(jí)高速緩存子系統(tǒng)。

Cortex-A9處理器實(shí)現(xiàn)ARMv7-A架構(gòu),并在Jazelle狀態(tài)下運(yùn)行32位ARM

2023-08-17 06:53:00

本建議概括介紹了軟件對(duì)識(shí)別為CVE-2020-16273的漏洞的影響和緩解措施。

本咨詢中討論的方案涉及基于ARMv8-M的處理器,包括Cortex-M23、Cortex M33

2023-08-17 06:31:40

Cortex-R52處理器是一款中等性能的有序超標(biāo)量處理器,主要用于汽車和工業(yè)應(yīng)用。

它還適用于各種其他嵌入式應(yīng)用,如通信和存儲(chǔ)設(shè)備。

Cortex-R52處理器有一到四個(gè)內(nèi)核,每個(gè)內(nèi)核實(shí)現(xiàn)一個(gè)

2023-08-17 06:24:31

的外圍設(shè)備。

·無(wú)法從非安全世界訪問(wèn)安全資產(chǎn),包括在非安全模式下運(yùn)行的處理器上運(yùn)行的軟件,以及不安全的外圍設(shè)備。

·保護(hù)可以對(duì)代碼或數(shù)據(jù)存儲(chǔ)空間或任何操作硬件和程序狀態(tài)進(jìn)行編程的資產(chǎn)。

這包括避免通過(guò)使用能夠

2023-08-16 08:21:23

提前(AOT)編譯的特定支持。

·決定處理器如何運(yùn)行的模式和狀態(tài),包括當(dāng)前的執(zhí)行特權(quán)和安全性。

·例外模式。

·內(nèi)存模型,定義內(nèi)存排序和內(nèi)存管理:

-ARMv7-A架構(gòu)配置文件定義虛擬內(nèi)存系統(tǒng)架構(gòu)

2023-08-12 07:46:44

求助蜂鳥(niǎo)e203處理器開(kāi)源代碼中惡的Makefile編譯腳本和測(cè)試腳本怎么修改?有沒(méi)有大佬指點(diǎn)一下,萬(wàn)分感謝

2023-08-12 06:52:25

:

·最多四個(gè)Cortex-A53處理器。

·ARMv8-A體系結(jié)構(gòu)指令集的AArch32和AArch64版本。

·多數(shù)指令對(duì)稱雙發(fā)布的有序流水線。

·具有內(nèi)存管理單元(MMU)的哈佛一級(jí)(L1)內(nèi)存系統(tǒng)

2023-08-12 06:44:40

本手冊(cè)中的體系結(jié)構(gòu)描述使用了與Armv8體系結(jié)構(gòu)相同的術(shù)語(yǔ)。有關(guān)該術(shù)語(yǔ)的更多信息,請(qǐng)參閱Armv8-A架構(gòu)配置文件Armv8 Arm?架構(gòu)參考手冊(cè)A部分的介紹。此外,在適當(dāng)?shù)那闆r下使用AArch64

2023-08-11 07:45:48

ARM體系結(jié)構(gòu)已經(jīng)發(fā)展到支持跨多種性能點(diǎn)實(shí)施的程度。

超過(guò)20億個(gè)部件的出貨量,使其成為許多細(xì)分市場(chǎng)的主導(dǎo)架構(gòu)。

ARM處理器的架構(gòu)簡(jiǎn)單性傳統(tǒng)上導(dǎo)致了非常小的實(shí)現(xiàn),而小實(shí)現(xiàn)允許設(shè)備具有非常低的功耗。

實(shí)施規(guī)模、性能和非常低的功耗仍然是ARM架構(gòu)開(kāi)發(fā)的關(guān)鍵屬性。

2023-08-11 07:10:29

跟蹤支持是一種體系結(jié)構(gòu)擴(kuò)展,通常使用嵌入式跟蹤宏單元(ETM)實(shí)現(xiàn)。

ETM構(gòu)造與處理器的操作相對(duì)應(yīng)的實(shí)時(shí)跟蹤流。

跟蹤流是本地存儲(chǔ)在嵌入式跟蹤緩沖器(ETB)中以供獨(dú)立下載和分析,還是通過(guò)跟蹤端口

2023-08-11 06:52:28

。

在本文檔中,對(duì)PPU或PPU的引用是指實(shí)現(xiàn)該P(yáng)PU體系結(jié)構(gòu)的設(shè)備。除非上下文明確指出引用的是設(shè)備的可選或?qū)嵤┒x功能,否則這些引用描述了本規(guī)范的要求

2023-08-11 06:14:35

體系結(jié)構(gòu)功能。

該設(shè)計(jì)側(cè)重于數(shù)字信號(hào)處理(DSP)和機(jī)器學(xué)習(xí)等計(jì)算應(yīng)用。Cortex?-M85處理器能效高,在保持低功耗的同時(shí),實(shí)現(xiàn)了標(biāo)量和矢量運(yùn)算的高計(jì)算性能。

處理器可以配置為包括雙核鎖步(DCLS

2023-08-10 07:43:12

在本指南中,我們介紹了TrustZone。TrustZone通過(guò)內(nèi)置在CPU中的硬件強(qiáng)制隔離,提供了一種高效的全系統(tǒng)安全方法。

我們介紹了TrustZone添加到處理器體系結(jié)構(gòu)中的功能

2023-08-10 07:02:56

是ARM系統(tǒng)就緒計(jì)劃的SR和LS頻段的要求。

如果一個(gè)實(shí)現(xiàn)以適合該級(jí)別的目標(biāo)使用的性能級(jí)別實(shí)現(xiàn)該級(jí)別的所有功能,則該實(shí)現(xiàn)與該級(jí)別的服務(wù)器基本系統(tǒng)體系結(jié)構(gòu)的級(jí)別一致。這意味著一個(gè)級(jí)別的所有功能都可以被

2023-08-09 07:49:10

功能。

設(shè)計(jì)的重點(diǎn)是計(jì)算機(jī)應(yīng)用,如數(shù)字信號(hào)處理(DSP)和機(jī)器學(xué)習(xí)。Cortex?-M85處理器能效高,在標(biāo)量和向量運(yùn)算中實(shí)現(xiàn)高計(jì)算性能,同時(shí)保持低功耗。

處理器可以配置為包括雙核鎖定步驟(DCLS

2023-08-09 07:28:27

Cortex-M23處理器是一個(gè)可配置的兩級(jí)32位RISC處理器。它有一個(gè)AMBA 5AHB接口,并包括NVIC組件。它還具有可選的硬件調(diào)試、單周期I/O接口和內(nèi)存保護(hù)功能。

2023-08-09 06:20:47

本文檔描述了CoreSight體系結(jié)構(gòu),平臺(tái)和系統(tǒng)使用。

2023-08-09 06:08:20

本指南介紹了內(nèi)存系統(tǒng)資源分區(qū)和監(jiān)視(MPAM)Arm體系結(jié)構(gòu)的可選添加,以支持內(nèi)存系統(tǒng)分區(qū)。MPAM記錄在內(nèi)存系統(tǒng)資源分區(qū)和監(jiān)視(MPAM)中,用于A配置文件體系結(jié)構(gòu)Arm體系結(jié)構(gòu)參考手冊(cè)補(bǔ)充。

2023-08-09 06:08:10

本章總結(jié)了本增補(bǔ)與ARMv8 體系結(jié)構(gòu)參考手冊(cè)。

2023-08-08 07:53:09

本規(guī)范定義了基于Arm A配置文件體系結(jié)構(gòu)的處理器的動(dòng)態(tài)測(cè)量信任根(DRTM)體系結(jié)構(gòu)。本規(guī)范基于TCG D-RTM體系結(jié)構(gòu)[4]的概念,但作為一個(gè)獨(dú)立的獨(dú)立文檔發(fā)揮作用。它使用了TCG體系結(jié)構(gòu)

2023-08-08 07:45:00

ARM體系結(jié)構(gòu)包含大量功能,這些功能被描述為可選或定義的實(shí)施。來(lái)自平臺(tái)操作系統(tǒng)供應(yīng)商的反饋表明這種可變性對(duì)于系統(tǒng)代碼的開(kāi)發(fā)人員來(lái)說(shuō)是一個(gè)實(shí)質(zhì)性的問(wèn)題,由于操作系統(tǒng)必須滿足各種不同的系統(tǒng)配置,導(dǎo)致開(kāi)發(fā)

2023-08-08 07:40:40

本規(guī)范提供了ACPI[2]擴(kuò)展的詳細(xì)描述,這些擴(kuò)展是在支持Armv8-a RAS擴(kuò)展和a配置文件體系結(jié)構(gòu)規(guī)范的Arm體系結(jié)構(gòu)參考手冊(cè)補(bǔ)充可靠性、可用性和可服務(wù)性(RAS)定義的RAS系統(tǒng)體系結(jié)構(gòu)的系統(tǒng)中實(shí)現(xiàn)內(nèi)核優(yōu)先錯(cuò)誤處理所需的

2023-08-08 07:24:35

Cortex-M4處理器包含處理器核心、嵌套矢量中斷控制器(NVIC)、高性能總線接口、低成本調(diào)試解決方案和可選的浮點(diǎn)單元(FPU)。

Cortex-M4處理器包含以下功能:

?處理器核心。

?嵌套

2023-08-08 07:18:05

本增補(bǔ)件是Armv9-A體系結(jié)構(gòu)的Arm?體系結(jié)構(gòu)參考手冊(cè)增補(bǔ)件輪廓本書介紹了Armv9-A體系結(jié)構(gòu)擴(kuò)展,因此必須與Arm?體系結(jié)構(gòu)參考手冊(cè)一起閱讀A型架構(gòu)。

2023-08-08 07:07:05

Armv8體系結(jié)構(gòu)有幾個(gè)不同的配置文件。這些配置文件是體系結(jié)構(gòu)的變體針對(duì)不同的市場(chǎng)和用例。Armv8-M體系結(jié)構(gòu)就是其中之一配置文件。

Arm定義了三個(gè)體系結(jié)構(gòu)配置文件:應(yīng)用程序(A)、實(shí)時(shí)(R

2023-08-08 06:18:24

GAUDIRHL-2000是一款先進(jìn)的Al和DeepLearning Training處理器,利用專門構(gòu)建的體系結(jié)構(gòu),提供卓越的性能、可擴(kuò)展性、電源效率和成本節(jié)約。Gaudi HL-205夾層卡

2023-08-04 07:23:21

IntelXeon@D-2700和D-1700處理器為云、邊緣和5G網(wǎng)絡(luò)提供突破性的、密度優(yōu)化的性能、可擴(kuò)展性和價(jià)值。intel Xeon D集成了以太網(wǎng)和加速器的處理器,用于支持網(wǎng)絡(luò)、存儲(chǔ)、工業(yè)loT、數(shù)據(jù)中心邊緣等。

2023-08-04 07:07:26

TrustZone體系結(jié)構(gòu)為系統(tǒng)設(shè)計(jì)人員提供了一種幫助保護(hù)系統(tǒng)的方法TrustZone安全擴(kuò)展和安全外設(shè)。低級(jí)程序員應(yīng)該

理解TrustZone架構(gòu)對(duì)系統(tǒng)的設(shè)計(jì)要求;即使他們不使用安全功能。

ARM

2023-08-02 18:10:53

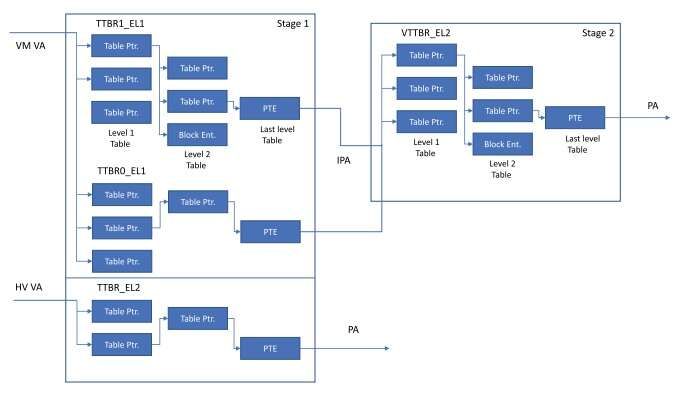

Armv8-A使用一個(gè)虛擬內(nèi)存系統(tǒng),其中代碼使用的地址(虛擬地址)是

轉(zhuǎn)換成物理地址,供存儲(chǔ)系統(tǒng)使用。這個(gè)翻譯是

由處理器中稱為內(nèi)存管理單元(MMU)的部分執(zhí)行。mmu的

Arm架構(gòu)使用存儲(chǔ)在內(nèi)存中

2023-08-02 17:29:58

Cortex-A9處理器是一款高性能、低功耗的ARM宏單元,具有L1緩存子系統(tǒng),可提供完整的虛擬內(nèi)存功能。Cortex-A9處理器實(shí)現(xiàn)ARMv7-A架構(gòu),在Jazelle?狀態(tài)下運(yùn)行32位ARM指令、16位和32位Thumb?指令以及8位Java字節(jié)碼。

2023-08-02 16:29:35

用于嵌入式產(chǎn)品的CoreLink SIE-200系統(tǒng)IP是互連、外圍和TrustZone?控制器組件的集合,用于符合ARMv8-M處理器體系結(jié)構(gòu)的處理器。

2023-08-02 16:25:27

高性能和高性能之間進(jìn)行權(quán)衡代碼密度。ARM922T處理器是哈佛高速緩存體系結(jié)構(gòu)處理器,其目標(biāo)是全內(nèi)存管理、高性能和低功率是至關(guān)重要的。此設(shè)計(jì)中的獨(dú)立指令和數(shù)據(jù)緩存每個(gè)大小為8KB,具有8字線長(zhǎng)度。ARM922T實(shí)現(xiàn)了增強(qiáng)型ARM體系結(jié)構(gòu)v4 MMU為指令和數(shù)據(jù)地址

2023-08-02 15:44:14

Arm Cortex-A32 Cortex-ACortex?A32處理器支持A32和T32指令集中的高級(jí)SIMD和浮點(diǎn)指令。

Cortex?A32浮點(diǎn)實(shí)現(xiàn):

?不生成浮點(diǎn)異常。

?在硬件中實(shí)現(xiàn)所有

2023-08-02 14:50:53

GIC-500是一個(gè)構(gòu)建時(shí)可配置的中斷控制器,最多支持128個(gè)內(nèi)核。GIC-500僅支持實(shí)現(xiàn)ARMv8架構(gòu)的內(nèi)核,以及具有標(biāo)準(zhǔn)GIC流協(xié)議接口的GIC CPU接口,如Cortex?-A57和Cortex-A53。它實(shí)現(xiàn)了ARM?通用中斷控制器體系結(jié)構(gòu)規(guī)范3.0版、GIC體系結(jié)構(gòu)3.0版和4.0版,以支持:

2023-08-02 14:02:08

本指南介紹在Cortex-M處理器中實(shí)現(xiàn)的Armv8-M異常模型。本指南還提供了示例,以幫助解釋其介紹的概念。

Arm架構(gòu)分為多個(gè)配置文件,針對(duì)不同細(xì)分市場(chǎng)的需求。微控制器配置文件或“M配置文件

2023-08-02 13:14:49

高速緩存體系結(jié)構(gòu)處理器,適用于全內(nèi)存管理、高性能和低功耗至關(guān)重要的多程序應(yīng)用。此設(shè)計(jì)中的獨(dú)立指令和數(shù)據(jù)緩存大小分別為16KB,具有8字線長(zhǎng)度。ARM920T處理器實(shí)現(xiàn)了一個(gè)增強(qiáng)的ARM架構(gòu)v4-MMU,為

2023-08-02 13:05:00

可合成的ARM968E-S處理器是ARM9Thumb系列的一員,實(shí)現(xiàn)了ARMv5TE體系結(jié)構(gòu)。它支持32位ARM指令集和16位Thumb指令集。ARM968E-S處理器適用于要求高性能、低系統(tǒng)成本、小芯片尺寸和低功耗的各種嵌入式應(yīng)用。

2023-08-02 12:08:51

ARM1136JF-S處理器包含一個(gè)整數(shù)單元,用于實(shí)現(xiàn)ARM體系結(jié)構(gòu)v6。它支持ARM和Thumb指令集,支持直接執(zhí)行Java字節(jié)碼的Jazelle技術(shù),以及一系列對(duì)32位寄存器中的16位或8位數(shù)

2023-08-02 11:46:41

本文介紹了ARM中可用的硬件同步原語(yǔ)體系結(jié)構(gòu),并提供了系統(tǒng)級(jí)程序員如何使用它們的示例。

2023-08-02 10:59:00

包含一個(gè)簡(jiǎn)短的介紹,以幫助讀者。與體系結(jié)構(gòu)兼容的實(shí)現(xiàn)必須

遵守本規(guī)范中的所有規(guī)則。

一些體系結(jié)構(gòu)規(guī)則伴隨著解釋為什么指定體系結(jié)構(gòu)的基本原理陳述

事實(shí)就是這樣。基本原理陳述用字母X表示。

有些部分

2023-08-02 10:55:31

本指南描述了GICv3和GICv4體系結(jié)構(gòu)中對(duì)虛擬化的支持。它涵蓋了管理程序可用于生成和管理虛擬中斷的控件。指南是對(duì)于任何需要了解中斷控制器功能的人來(lái)說(shuō)編寫軟件來(lái)管理虛擬中斷。

本指南描述了

2023-08-02 10:43:36

。

?在硬件中實(shí)現(xiàn)所有標(biāo)量操作,支持以下各項(xiàng)的所有組合:

--舍入模式。

--沖洗至零。

--默認(rèn)非數(shù)字(NaN)模式。

Armv8體系結(jié)構(gòu)在AArch64執(zhí)行狀態(tài)下消除了高級(jí)SIMD和浮點(diǎn)支持的版本號(hào)概念

2023-08-02 10:42:05

本指南介紹Armv8-A體系結(jié)構(gòu)中的內(nèi)存系統(tǒng)。這些系統(tǒng)詳細(xì)通過(guò)內(nèi)存模型、內(nèi)存類型、內(nèi)存屬性和屏障。

在以下情況下,您必須了解內(nèi)存系統(tǒng)的操作和訪問(wèn)順序您的代碼直接與硬件或在其他核心上執(zhí)行的代碼交互

2023-08-02 10:38:22

本教程概述了如何使用CoreSight Access Tool執(zhí)行低級(jí)調(diào)試(CSAT)與Armv8目標(biāo)。低級(jí)調(diào)試允許您:

?操作單個(gè)寄存器,包括不能正常訪問(wèn)的調(diào)試寄存器

應(yīng)用程序級(jí)調(diào)試器。

?執(zhí)行

2023-08-02 10:27:29

的內(nèi)核,該單元為標(biāo)記為共享的存儲(chǔ)器維護(hù)L1數(shù)據(jù)緩存一致性。Cortex-A5 MPCore處理器實(shí)現(xiàn)ARMv7體系結(jié)構(gòu),運(yùn)行32位ARM指令、16位和32位Thumb指令以及8位Java

2023-08-02 10:00:07

。

NEON MPE支持ARM?體系結(jié)構(gòu)參考手冊(cè)、ARMv7-A和ARMv7-R版本中描述的所有尋址模式和操作。

NEON MPE的功能包括:

?SIMD和標(biāo)量單精度浮點(diǎn)計(jì)算。

?標(biāo)量雙精度浮點(diǎn)計(jì)算

2023-08-02 09:58:22

Arm體系結(jié)構(gòu)經(jīng)過(guò)幾次重大修訂,已發(fā)展到支持實(shí)現(xiàn)的程度在廣泛的性能點(diǎn)上,每年生產(chǎn)超過(guò)10億個(gè)零件。最新Armv7版本通過(guò)定義一組架構(gòu)概要文件正式承認(rèn)了這種多樣性架構(gòu)以適應(yīng)不同的市場(chǎng)需求。一個(gè)關(guān)鍵因素

2023-08-02 09:43:30

,您將能夠:

?描述基本的虛擬化概念

?構(gòu)建和運(yùn)行示例代碼來(lái)演示Armv8-R的虛擬化特性

體系結(jié)構(gòu)

本指南中的源代碼和注冊(cè)表圖是特定于Cortex-R52處理器的是第一個(gè)實(shí)現(xiàn)Armv8-R架構(gòu)的處理器。其他處理器與Cortex-R52處理器,但是本指南中的想法仍然相關(guān)。

2023-08-02 09:27:55

Cortex-A57處理器是一款高性能、低功耗的處理器,可實(shí)現(xiàn)ARMv8-a建筑學(xué)它在帶有L1和L2緩存子系統(tǒng)的單個(gè)處理器設(shè)備中有一到四個(gè)核心。

2023-08-02 09:12:53

Cortex-A72處理器加密引擎支持ARMv8加密擴(kuò)展。加密擴(kuò)展添加了高級(jí)SIMD可以用來(lái)加速AES、SHA1和SHA2-256算法執(zhí)行的新指令。

2023-08-02 08:54:44

ARM體系結(jié)構(gòu)的ABl版本2包括本文檔1.2美元中列出的十個(gè)組件。ARM體系結(jié)構(gòu)的ABl(基礎(chǔ)標(biāo)準(zhǔn))[BSABI]。

ABl的第2版旨在在不引入不兼容性的情況下擴(kuò)展和澄清第1版。例如,它在第1版的九

2023-08-02 08:53:35

助開(kāi)發(fā)人員為他們的項(xiàng)目做出正確選擇的背景下進(jìn)行考慮。

Cortex-R處理器是利基市場(chǎng),但有一些獨(dú)特的功能,使它們非常適合他們的目標(biāo)市場(chǎng)。即使在這一細(xì)分市場(chǎng)中,ARM也在繼續(xù)創(chuàng)新,支持

2023-08-02 07:39:39

指令集體系結(jié)構(gòu)(ISA)是計(jì)算機(jī)抽象模型的一部分。它定義了軟件控制處理器。

Arm ISA允許您編寫符合Arm規(guī)范的軟件和固件。

這意味著,如果您的軟件或固件符合規(guī)范,任何基于arm的處理器將以同樣

2023-08-02 06:33:42

特定功能。ARMv8?M處理器的體系結(jié)構(gòu)包含故障通過(guò)異常處理功能,以及用于處理系統(tǒng)級(jí)的非屏蔽中斷(NMI)

錯(cuò)誤,例如,褐化檢測(cè)。特定于實(shí)現(xiàn)的功能,如錯(cuò)誤此處不包括存儲(chǔ)器的糾正代碼(ECC

2023-08-02 06:28:02

本指南主要介紹Armv7系統(tǒng)和Armv8系統(tǒng)中跟蹤的高級(jí)視圖,最高可達(dá)Armv8.4版本。

該指南涵蓋:

?跟蹤是什么以及如何使用

?跟蹤體系結(jié)構(gòu)是如何定義的,以及它如何映射到不同的跟蹤組件實(shí)現(xiàn)

?在Arm系統(tǒng)中可以看到哪些跟蹤組件

?一些跟蹤系統(tǒng)的示例

2023-08-02 06:11:37

ARMv8-M異常模型描述了處理器如何響應(yīng)異常與每個(gè)異常關(guān)聯(lián)的屬性,例如其優(yōu)先級(jí)和異常返回行為。通常有一個(gè)異常處理程序與每個(gè)異常類型相關(guān)聯(lián)。

ARMv8-M處理器與其他ARM處理器系列之間存在差異

2023-08-02 06:09:37

架構(gòu)。不需要事先了解 Arm 體系結(jié)構(gòu),但假定對(duì)處理器和編程及其術(shù)語(yǔ)大致熟悉。在本指南的最后,您可以檢查您的知識(shí).您將了解 Arm 架構(gòu)的不同配置文件,以及某些功能是特定于架構(gòu)還是特定于微架構(gòu)。

2023-08-01 14:35:14

從 2160 數(shù)據(jù)表中得到消息,核心支持所有 ARMv8 功能,但寄存器 id_aa64mmfr1_el1 的值為 0。

2.我應(yīng)該配置CONFIG_KVM來(lái)重新配置中斷向量表嗎?el2_setup 函數(shù)配置了 el1_sync。

2023-06-08 07:21:41

會(huì)觸發(fā)一個(gè)與MMU相關(guān)的缺頁(yè)異常。在RISC-V體系結(jié)構(gòu)中,根據(jù)處理器的虛擬地址位寬,提供了Sv32、Sv39、Sv48多種物理轉(zhuǎn)換機(jī)制。實(shí)操在BenOS里面實(shí)現(xiàn)虛擬地址映射到同等數(shù)值的物理地址上,即

2023-04-17 00:43:06

ARMv8基本概念

(1)執(zhí)行狀態(tài)(execution state):處理器運(yùn)行時(shí)的環(huán)境,包括寄存器的位寬、支持的指令集、異常模型、內(nèi)存管理及編程模型等。ARMv8體系結(jié)構(gòu)定義了兩個(gè)執(zhí)行狀態(tài):

AArch64:64位的執(zhí)行狀態(tài)

提供31個(gè)64位的通用寄存器

2023-04-16 10:45:38 4300

4300 芯馳D9處理器 四核Cortex-A55+Cortex-R5 核心板基于芯馳D9處理器設(shè)計(jì),嚴(yán)格滿足工業(yè)級(jí)標(biāo)準(zhǔn),廣泛應(yīng)用于電力電子、工業(yè)自動(dòng)化、工程機(jī)械

2023-04-03 17:06:43

最近有幸讀了一本介紹RISC-V的書籍《RISC-V體系結(jié)構(gòu)編程與實(shí)踐》,這是一本非常有價(jià)值的書籍,它介紹了RISC-V體系結(jié)構(gòu)的各個(gè)方面,包括指令集、寄存器、內(nèi)存管理、中斷等等。在閱讀完本書

2023-03-28 11:41:50

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論