兩個月前,也就是曾經(jīng)的FPGA巨頭Altera被英特爾收購的4年之后,英特爾推出了“全面借助自身能力”開發(fā)的新一代FPGA產(chǎn)品——Agilex。與此前Altera推出的Stratix、Arria、Cyclone、Max等產(chǎn)品系列完全不同,Agilex是一個全新的FPGA系列,“體現(xiàn)了你能想象到的所有與Intel相關(guān)的技術(shù)資源”,被英特爾寄予了更多的期待。

這里所提到的“相關(guān)技術(shù)資源”,基本上等同于英特爾在2018年底“架構(gòu)日”上所提出的制程和封裝、架構(gòu)、內(nèi)存和存儲、互連、安全、軟件這“六大技術(shù)支柱”。盡管當時英特爾官方表示將會盡快把六大技術(shù)支柱運用于自己的整個工程部門,落實在已經(jīng)或即將推出的產(chǎn)品與技術(shù)規(guī)劃中。但只用了不到半年的時間,Agilex FPGA就成為“六大技術(shù)支柱”落地的最佳載體,英特爾強大的系統(tǒng)研發(fā)和整合能力可見一斑。

窺一斑而知全豹

Agilex是Agile(敏捷)和Flexible(靈活)兩個詞語的結(jié)合體,而這兩個特點也正是現(xiàn)代FPGA技術(shù)最為核心的兩大要點。英特爾在2015年時就承諾說未來會根據(jù)不同的客戶需求提供不同點5的異構(gòu)架構(gòu),包括:分立的CPU+FPGA、封裝集成的CPU+FPGA、以及將Intel CPU/FPGA/ARM三者進行管芯集成的FPGA。

理由是顯而易見的。通過集成,不但能夠降低延時,提高效能和性能/瓦,更可以統(tǒng)一處理器和FPGA之間的工具流程,為不同的性能需求提供更廣泛的體系結(jié)構(gòu)支持。4年之后,Agilex FPGA通過異構(gòu)架構(gòu),實現(xiàn)了對不同制程工藝、不同邏輯單元之間的集成,在靈活性和定制化方面實現(xiàn)了突破。

根據(jù)英特爾2月份的基準測試,Agilex在最大時鐘速率(Fmax)上比Stratix 10提高了40%,而總能耗降低高達40%。此外,Agilex還具有高達40 TFLOP的DSP性能(FP16配置)和92 TOP DSP性能(INT8配置)。

坦率的說,僅憑異構(gòu)架構(gòu)這一點,Agilex FPGA其實是無法實現(xiàn)上述性能指標的,那么,Agilex FPGA中還隱藏著哪些不為人知的“黑科技”呢?

.10納米工藝和高級3D封裝

對于英特爾這樣擁有“端到端”解決方案的半導體巨頭來說,擁有先進的半導體制程技術(shù)和封裝技術(shù),是構(gòu)建領(lǐng)先產(chǎn)品的基礎(chǔ)與關(guān)鍵。在架構(gòu)日以及隨后的CES 2019展上,英特爾相繼展示了覆蓋云到端的10納米產(chǎn)品,包括“Ice Lake”PC 處理器、“Lakefield”客戶端平臺、“Snow Ridge”網(wǎng)絡(luò)系統(tǒng)芯片、“Ice Lake”英特爾至強可擴展處理器,以及被外界視為繼2018年推出的嵌入式多芯片互連橋接(EMIB)封裝技術(shù)之后,又一個具備“里程碑”意義的創(chuàng)新突破——“Foveros”3D封裝技術(shù)。

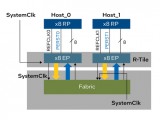

為了確保性能的一致性,Agilex FPGA器件核心的FPGA邏輯結(jié)構(gòu)芯片同樣采用了英特爾10納米芯片制程技術(shù)構(gòu)建,這也是目前世界上最先進的FinFET制程技術(shù)之一。同時,Agilex還融合了英特爾專有嵌入式多芯片互連橋接(EMIB)集成的 3D 異構(gòu)系統(tǒng)級封裝(SiP)技術(shù),它提供了一種高性能、低成本的方法,有助于將Chiplets和FPGA邏輯結(jié)構(gòu)芯片集成至相同的封裝中。

.第二代英特爾HyperFlex架構(gòu)和Chiplets架構(gòu)

Agilex FPGA的邏輯結(jié)構(gòu)芯片采用了第二代英特爾HyperFlex架構(gòu),除了與第一代架構(gòu)一樣,在整個核心結(jié)構(gòu)中都使用額外的寄存器Hyper-Registers外,二代架構(gòu)還提升了整體結(jié)構(gòu)性能,同時最大限度地降低了功耗,其中最顯著的一項改進是在超級寄存器中添加了高速旁路。

而Chiplets是一種物理IP模塊,可通過封裝級集成方法和標準化接口集成其他Chiplets。借助Chiplets這種混合搭配模式,收發(fā)器數(shù)量不再受通道數(shù)量的限制。設(shè)計人員要想增加或減少收發(fā)器通道數(shù)量,只需添加所需的收發(fā)器Chiplets即可,無需重新布局芯片以集成不同數(shù)量的通道。僅此一項,英特爾就將單個收發(fā)器通道的速度從58Gbps提升到112Gbps。

.高性能處理器接口

在數(shù)據(jù)中心里作為CPU的硬件加速器,用來加速深度學習的模型訓練、金融計算、網(wǎng)絡(luò)功能卸載等各類應(yīng)用,是當前FPGA的一個主要應(yīng)用場景。但該領(lǐng)域亟待解決的核心問題之一,就是緩存一致性。換句話說,就是必須要明確CPU與硬件加速器之間的內(nèi)存互聯(lián)協(xié)議。

今年3月,英特爾宣布聯(lián)合微軟、阿里、思科、戴爾EMC、Facebook、谷歌、惠普企業(yè)HPE和華為等公司,共同推出一個全新的互聯(lián)標準,取名為Compute Express Link(CXL),應(yīng)用目標鎖定互聯(lián)網(wǎng)數(shù)據(jù)中心、通信基礎(chǔ)設(shè)施、云計算與云服務(wù)等領(lǐng)域,而這也正是FPGA大顯身手的重要平臺。

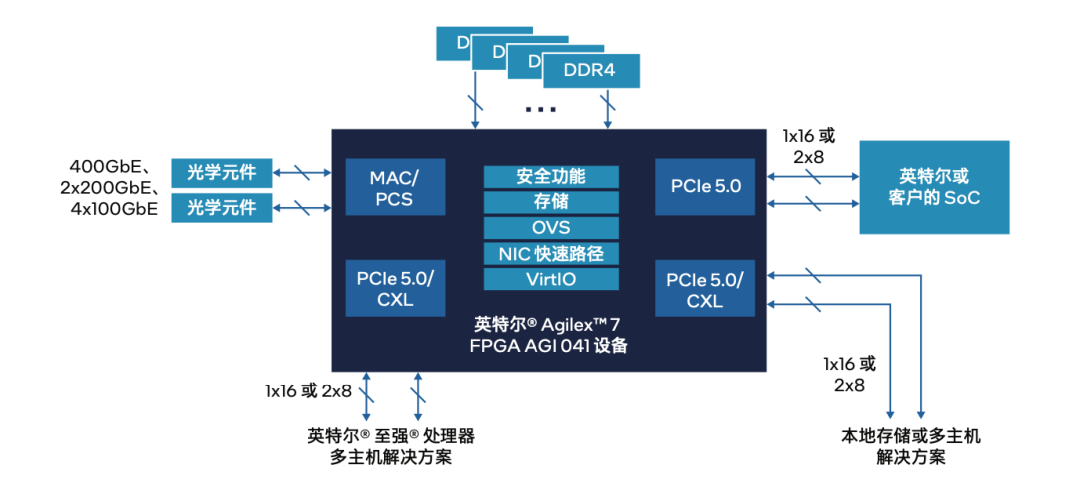

為了確保高性能在線處理和處理器負載加速,英特爾Agilex FPGA支持最新一代高性能處理器接口,包括PCIe Gen 5和CXL,并將成為首款采用Xeon可擴展處理器的一致的高速緩存和內(nèi)存互聯(lián)結(jié)構(gòu)的FPGA。

.先進的內(nèi)存層級結(jié)構(gòu)

Agilex FPGA 支持各個層級的內(nèi)存資源,包括通過專用接口提供的嵌入式內(nèi)存資源、封裝內(nèi)內(nèi)存和片外內(nèi)存。該層級結(jié)構(gòu)的第一層是嵌入式片上內(nèi)存,包括MLAB、塊RAM和eSRAM,每種內(nèi)存均可提供不同的容量,以滿足不同的處理需求。此外,英特爾在設(shè)計中還使用SIP技術(shù)將高帶寬內(nèi)存(HBM)直接集成至Agilex FPGA器件中,有助于縮減電路板尺寸和成本,簡化與降低電源需求。

另一個值得關(guān)注的重點是Agilex平臺還集成了eASIC技術(shù)。這種集成eASIC芯片定制技術(shù)能夠?qū)崿F(xiàn)從FPGA到結(jié)構(gòu)化ASIC的遷移。換句話說,用戶可以利用eASIC自身具備的可復用 IP 的自定義邏輯連續(xù)體,在整個產(chǎn)品生命周期內(nèi)進行靈活優(yōu)化,快速從FPGA轉(zhuǎn)移到ASIC。

.軟件

全新硬件架構(gòu)每一個數(shù)量級的性能提升,軟件能相應(yīng)帶來兩個數(shù)量級的性能提升。在新一代Agilex FPGA上,配套支持軟件Quartus Prime可縮短硬件開發(fā)者30%的編譯時間,內(nèi)存利用率也提高了15%。同時,新一代的Agilex FPGA也納入到One API的架構(gòu)當中。

即將于今年第四季度推出的“OneAPI”軟件編程框架,,為軟件開發(fā)者提供了單一源的異構(gòu)編程環(huán)境,支持常見的性能庫API、Intel VTune和Advisor等軟件開發(fā)工具,能夠?qū)④浖ヅ涞侥茏畲蟪潭燃铀佘浖a的硬件上,用以簡化包括FPGA、CPU、GPU、人工智能和其它加速器在內(nèi)的各種計算引擎的編程接口,降低各種架構(gòu)和工作負載下的開發(fā)復雜性,加速六大技術(shù)支柱的大規(guī)模部署。

迎接多元化計算時代

讓我們先暫時跳出FPGA這個小圈子,來看看為什么英特爾要提出“六大技術(shù)支柱”?

有人說這“六大技術(shù)支柱”是英特爾為抵御NVIDIA、AMD和賽靈思等公司而筑起的堅固城防,也有人不惜溢美之詞,將其稱之為英特爾引領(lǐng)未來計算發(fā)展的“創(chuàng)新矩陣”。但其實無論叫法如何,在英特爾看來,這六大技術(shù)支柱之間是相互關(guān)聯(lián)、緊密耦合的,既能夠帶來指數(shù)級的創(chuàng)新,也是英特爾未來十年甚至未來五十年的主要驅(qū)動力。

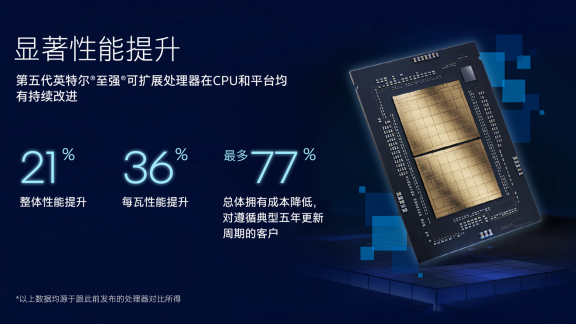

從英特爾發(fā)布的數(shù)據(jù)來看,其10nm工藝下的晶體管密度達到了100.8Mtr/mm2,大約是上一代的14nm工藝的2.7倍。也就是說在2015-2018這3年左右的時間內(nèi),英特爾實現(xiàn)了晶體管密度2.7倍的增長。同時,英特爾還正在積極研究如納米線晶體管、III-V材料(如砷化鎵和磷化銦)晶體管、硅晶片3D堆疊、高密度內(nèi)存與互聯(lián)、紫外光(EUV)光刻技術(shù)、自旋電子、神經(jīng)元計算等前沿項目。

發(fā)展半導體精尖制造技術(shù)和平臺,生產(chǎn)世界上最好的芯片,持續(xù)推動制程和封裝工藝技術(shù)創(chuàng)新,當然是英特爾的使命,但還不是全部。

我們現(xiàn)在正逐漸轉(zhuǎn)向以數(shù)據(jù)為中心的時代。預期到2020年,普通用戶每天產(chǎn)生的數(shù)據(jù)量為1.5GB,智慧醫(yī)院每天3TB,自動駕駛每天達4TB,而聯(lián)網(wǎng)飛機和智慧工廠每天分別達到了40TB和1PB!

這意味著伴隨著數(shù)據(jù)量的爆炸式增長,數(shù)據(jù)類型也發(fā)生革命性變化,人工智能、5G、自動駕駛、云計算、物聯(lián)網(wǎng)等新興應(yīng)用帶來了更加多元化的計算需求。例如在嵌入式應(yīng)用領(lǐng)域和邊緣設(shè)備端,用戶的需求是能夠?qū)崟r抽取包括圖像、視頻和視覺信息在內(nèi)的數(shù)據(jù);在通信基礎(chǔ)設(shè)施端,用戶需要高帶寬融合處理能力;在云端,相關(guān)企業(yè)的需求則是能夠高效的管理、組織和處理激增的數(shù)據(jù)。

也就是說,當我們從更高的維度來看數(shù)據(jù)架構(gòu)時,就會明顯的意識到,在這個海量數(shù)據(jù)推動計算架構(gòu)快速演進并呈指數(shù)級擴展的時代,沒有一種單一的技術(shù)可以全面滿足消費者或企業(yè)客戶對未來的計算需求,不可能只通過直接的標量架構(gòu)就能解決所有應(yīng)用,他們需要的是在多樣化的層級結(jié)構(gòu)中連接多樣化的架構(gòu),比如分別應(yīng)用于CPU、GPU、AI和FPGA產(chǎn)品中的標量(Scalar)、矢量(Vector)、矩陣(Matrix)和空間(Spatial)架構(gòu)。

同時,隨著從高度動態(tài)、非結(jié)構(gòu)化自然數(shù)據(jù)中進行收集、分析和決策的需求越來越高,對計算的需求也超越了經(jīng)典的CPU和GPU架構(gòu)。雖然領(lǐng)先的制程和CPU仍然至關(guān)重要,但要想充分把握數(shù)據(jù)爆發(fā)帶來的機遇,還需要在包括制程和封裝、架構(gòu)、內(nèi)存和存儲、互連、安全、軟件在內(nèi)的一系列基礎(chǔ)構(gòu)建模塊上極速創(chuàng)新。那種不去研究數(shù)據(jù)的產(chǎn)生、類別、以及所需要的處理能力,是不行的。這和以前的通用數(shù)據(jù)處理不一樣,只單純強調(diào)某一種處理器算力的做法是行不通的。

英特爾希望能通過六大技術(shù)支柱引領(lǐng)“超異構(gòu)計算”時代。即通過提供多樣化的標量、矢量、矩陣和空間計算架構(gòu)組合,以先進制程技術(shù)進行設(shè)計,由顛覆性內(nèi)存層次結(jié)構(gòu)提供支持,通過先進封裝集成到系統(tǒng)中,使用光速互連進行超大規(guī)模部署,提供統(tǒng)一的軟件開發(fā)接口以及安全功能。

以英特爾在CES 2019上展示的下一代CPU微架構(gòu)Sunny Cove為例,它包含了可加速人工智能和加密等專用計算任務(wù)的新功能,旨在提高通用計算任務(wù)下每時鐘計算性能和降低功耗。在即將量產(chǎn)的10納米PC處理器Ice Lake中,就高度整合了Sunny Cove微架構(gòu)、AI使用加速指令集以及英特爾第11代核心顯卡。

為什么要把制程封裝和架構(gòu)設(shè)計組合在一起?因為通過超異構(gòu)計算,英特爾可以集成不同架構(gòu)、不同制程、3D封裝、互連和OneAPI等技術(shù),確保可以最有效地實現(xiàn)產(chǎn)品多樣性,提升產(chǎn)品穩(wěn)定度,快速滿足客戶定制化和市場化的需求。

在向數(shù)據(jù)公司轉(zhuǎn)型的過程中,英特爾將自身定義為端到端方案提供商,即產(chǎn)品線覆蓋云端、網(wǎng)絡(luò)傳輸端和終端。其中,核心來自云端的大規(guī)模數(shù)據(jù)處理,而布局端到端則可以讓英特爾掌握“數(shù)據(jù)什么時候來、是什么樣的數(shù)據(jù)、需要怎么來處理”。

為了增進處理新數(shù)據(jù)的能力,加快技術(shù)發(fā)展的步伐,并推動PC和服務(wù)器以外的計算,英特爾過去六年來不但一直在研究能夠加快經(jīng)典計算平臺的專用架構(gòu),還同時加大了對人工智能(AI)和神經(jīng)擬態(tài)計算的投資和研發(fā)。完成了制造和封裝的首款自主學習神經(jīng)擬態(tài)測試芯片Loihi、已交付的49量子位超導量子測試芯片、在300毫米晶圓制程上發(fā)明的自旋量子位制造流程等,均被業(yè)界視作英特爾對未來計算的提前布局,旨在顛覆未來計算格局。

隨著人工智能、物聯(lián)網(wǎng)、傳感器等技術(shù)的融合應(yīng)用及進一步發(fā)展,越來越多無人干預的機器設(shè)備和應(yīng)用場景成為可能,“自能(Autonomous)”也正取代“智能”,成為帶動新一輪創(chuàng)新發(fā)展的新趨勢。在這樣的時代大背景下,英特爾戰(zhàn)略性地跳出了單純比拼工藝和算力的低層次競爭格局,站在更高的起點上,通過構(gòu)建全新的六大技術(shù)創(chuàng)新組合,將CPU、GPU、FPGA、AI加速器、通信系統(tǒng)、高速存儲等部分有機的結(jié)合到一起,重新定義了產(chǎn)品開發(fā)設(shè)計的模式,Agilex FPGA就是最佳印證之一。我們也期待看到更多基于六大技術(shù)支柱打造的產(chǎn)品上市,引領(lǐng)產(chǎn)業(yè)更好地解決多元化計算需求的挑戰(zhàn)。

電子發(fā)燒友App

電子發(fā)燒友App

評論