現代集成電路芯片中,隨著設計規模的不斷擴大。一個系統中往往含有數個時鐘。多時鐘帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步 FIFO(First In First Out)是解決這個問題的一種簡便、快捷的解決方案。##異步FIFO的VHDL語言實現

2014-05-28 10:56:41 3405

3405 存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序的讀出數據,其數據地址由內部讀寫指針自動加1完成,不能像普通存儲器那樣可以由地址線決定讀取或寫入某個指定的地址。 用途1: 異步FIFO讀寫分別采用相互異步的不同時鐘。在現代集

2018-06-21 11:15:25 6164

6164

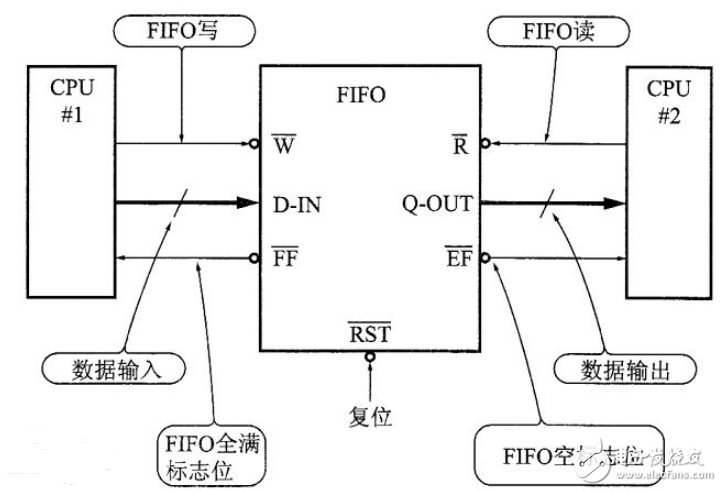

是這個問題的一種簡便、快捷的解決方案,使用異步 FIFO 可以在兩個不同時鐘系統之間快速而方便地傳輸實時數據。

2020-07-16 17:41:46 1050

1050

FIFO (先入先出, First In First Out )存儲器,在 FPGA 和數字 IC 設計中非常常用。 根據接入的時鐘信號,可以分為同步 FIFO 和異步 FIFO 。

2023-06-27 10:24:37 1199

1199

FIFO存儲器是系統的緩沖環節,如果沒有FIFO存儲器,整個系統就不可能正常工作,它主要有幾方面的功能:1)對連續的數據流進行緩存,防止在進機和存儲操作時丟失數據;2)數據集中起來進行進棧和存儲,可

2022-01-18 10:03:06

。音頻處理器通常與軟件或固件綁定,經設計執行某些回聲消除或降噪功能。 FPGA器件使用基于柵級的架構,適用于并行模式下的信號處理。它還具有內部存儲器、硬件乘法器和累加器,以及充足的I/O靈活性。某些

2016-12-07 16:05:03

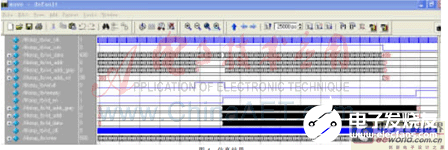

實例內部系統功能框圖如圖9.72所示。我們通過IP核例化一個異步FIFO,定時寫入數據,然后再讀出所有數據。通過QuartusII集成的在線邏輯分析儀SignalTap II,我們可以觀察FPGA片內

2019-05-06 00:31:57

的所有內部數據的地址。簡單的說,RAM是一種寫地址,讀數據的存儲單元;CAM與RAM恰恰相反。 除了塊RAM,Xilinx和Lattice的FPGA還可以靈活地將LUT配置成RAM、ROM、FIFO等

2016-08-23 10:33:54

的所有內部數據的地址。簡單的說,RAM是一種寫地址,讀數據的存儲單元;CAM與RAM恰恰相反。 除了塊RAM,Xilinx和Lattice的FPGA還可以靈活地將LUT配置成RAM、ROM、FIFO等

2016-09-18 11:15:11

的所有內部數據的地址。簡單的說,RAM是一種寫地址,讀數據的存儲單元;CAM與RAM恰恰相反。 除了塊RAM,Xilinx和Lattice的FPGA還可以靈活地將LUT配置成RAM、ROM、FIFO等

2016-10-08 14:43:50

應用,這種快樂試試你就會懂的。話不多說,上貨。半導體存儲器和可編程邏輯器件簡介半導體存儲器是一種能存儲大量二值信息的半導體器件。在電子計算機以及其他一些數字系統的工作過程中,都需要對大量的數據進行存儲

2023-02-23 15:24:55

涉及到溫度采集,與微處理器通信,串口輸出,控制數模轉換芯片等多個組成部分。本文提出一種高效實用的FPGA 接口設計,它能夠完成協調各個組成部分有序工作,準確、快速實現數據傳輸,嚴格控制信號時序等工作

2019-06-18 05:00:08

摘要:針對現有小型無人機導航系統的解算速度慢、多處理器核心臃腫可靠性差的缺點,實現了一種僅使用單一FPGA作為數據處理核心的小型高速導航解算系統。該系統對飛機運動方程組和導航方程組進行并行化分

2019-07-03 06:57:34

**第一至第三章**Q1. 若存儲器的數據總線寬度為32位,存取周期為200ns,則存儲器的帶寬是多少?存儲器的帶寬指單位時間內從存儲器進出信息的最大數量。存儲器帶寬 = 1/200ns ×32位

2021-07-28 06:23:01

ADSP-21160內部存儲器block0和block1中必須分別存放程序和數據,還是說可以在某block中既放程序又放數據

2016-12-29 16:58:48

具體應用情況:5509A DSP 的CE1空間外接了一個異步存儲器(FIFO),由DSP提供的異步讀時鐘 ARE 的頻率是怎么控制的呢?是主頻/(建立時間+選通時間+保持時間)嗎?當然這三個時間可由

2015-01-13 20:33:46

取出、掉電丟失。在各類邏輯系統中運用非常廣泛。在FPGA高級應用四的這個標題下,我們將會從內部存儲器到外部存儲器,介紹FIFO、ram、ddr幾種常用的存儲器設計。第一期我們介紹FIFOFIFO,全稱是first in first out (先入先出存儲隊列) 。在程序中FIFO作為數據的隊列通道,

2021-06-28 09:27:19

【作者】:趙宇紅;曾雷;白皛;謝人超;閻利早;【來源】:《電聲技術》2010年02期【摘要】:針對串行數字接口(SDI),提出了一種基于FPGA的音頻數據IP模塊解嵌方案。介紹了相關協議標準,重點

2010-04-22 11:54:44

概述該工程實例內部系統功能框圖如圖所示。我們通過IP核例化一個異步FIFO,這個FIFO的讀寫時鐘頻率不同,并且讀寫位寬也不同。定時對這個異步FIFO寫入數據,然后再讀出所有數據。通過ISE集成的在線

2016-03-07 11:32:16

一丶存儲器的分類和層次半導體存儲芯片:片選器:用來選取芯片有兩種譯碼驅動方式:線選法:一維排列,結構簡單,適合容量不大的存儲芯片重合法:二維陣列,適合容量大為什么線選法不適合大的呢?我們以9組

2021-07-23 08:20:14

時序一 什么是FIFOFirst In First Out ,是一種先進先出的數據緩存器,他與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序的讀出數據,其

2021-12-27 08:05:35

入的指令先完成并引退,跟著才執行第二條指令。 1.什么是FIFO? FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,他與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序的讀出數據,其數據地址由內部讀寫指針自動加1完成

2022-02-16 06:55:41

FIFO是FPGA處理跨時鐘和數據緩存的必要IP,可以這么說,只要是任意一個成熟的FPGA涉及,一定會涉及到FIFO。但是我在使用異步FIFO的時候,碰見幾個大坑,這里總結如下,避免后來者入坑。

2021-02-04 06:23:41

內存儲器可以在FPGA配置時自動初始化,相當于提供了一種非易失性的功能。片內存儲器的最佳應用場合包括作為常見的緩存、點到點的緩存、查找表以及FIFO等。緩存,由于其具有低反應延時,片內存儲器在微處理器中作為

2016-10-10 17:08:22

In First Out),即先入先出,這是一種典型的計算機數據或指令處理機制,和中國人所謂的“先來后到”理念有異曲同工之妙。而我們這里要說的FIFO存儲器,和前面帶有地址可直接定位操作的ROM或RAM存儲器

2016-12-23 17:48:03

該工程實例內部系統功能框圖如圖9.72所示。我們通過IP核例化一個異步FIFO,定時寫入數據,然后再讀出所有數據。通過QuartusII集成的在線邏輯分析儀SignalTap II,我們可以觀察

2018-08-28 09:39:16

強大的硬件支持。SOPC是Ahera公司提出的一種靈活、高效的片上系統(SOC)解決方案,它將處理器、存儲器、I/O口等系統設計所需要的功能模塊集成到一個可編程器件上,從而構成一個可編程的片上系統

2018-12-07 10:27:46

本文介紹一種基于虛擬存儲器的USB下載線設計。

2021-05-27 06:07:33

作者:王烈洋 黃小虎 占連樣 珠海歐比特控制工程股份有限公司隨著電子技術的飛速發展, 存儲器的種類日益繁多,每一種存儲器都有其獨有的操作時序,為了提高存儲器芯片的測試效率,一種多功能存儲器芯片

2019-07-26 06:53:39

如何利用Xilinx FPGA和存儲器接口生成器簡化存儲器接口?

2021-05-06 07:23:59

本文介紹了一種0.13微米CMOS T藝下FPGA中嵌入式存儲器模塊的設計與實現。

2021-04-09 06:02:09

擴展存儲器讀寫實驗的目的是什么?怎樣去設計一種擴展存儲器讀寫的電路?擴展存儲器讀寫實驗的流程有哪些?

2021-07-14 07:04:49

通過對FPGA芯片內部EBRSRAM的深入研究,提出了一種利用格雷碼對地址進行編碼的異步FIFO設計方案。

2021-04-13 06:41:03

嗨, 我正在尋找具有內部存儲器的CPLD。我想將程序存儲在CPLD中,這樣每次打開電源時,我都不必重新編程IC。有沒有這樣的CPLD?謝謝,阿文德古普塔。

2019-08-06 08:27:34

隨著集成電路制造工藝水平的提高,半導體芯片上可以集成更多的功能,為了讓產品有別于競爭對手的產品特性,在ASIC上集成存儲器可以降低成本和功耗、改善性能、增加系統級芯片的可靠性。隨著對嵌入式存儲器需求的持續增長,其復雜性、密度和速度也日益增加,從而需要提出一種專用存儲器設計方法。

2019-11-01 07:01:17

結合高速嵌入式數據采集系統,提出一種基于CvcloneⅢ FPGA實現的異步FIFO和鎖相環(PLL)結構來實現高速緩存,該結構可成倍提高數據流通速率,增加數據采集系統的實時性。采用FPGA設計高速緩存,能針對外部硬件系統的改變,通過修改片內程序以應用于不同的硬件環境。

2021-04-30 06:19:52

FIFO的基本結構和工作原理異步FIFO設計中的問題與解決辦法FPGA內部軟異步FIFO設計

2021-04-08 07:07:45

致性協議用于維護由于多個處理器共享數據引發的多處理器數據一致性問題。論述了一個適用于64位多核處理器的共享緩存設計,包括如何實現多處理器緩存一致性及其全定制后端實現。本文介紹了一種共享高速存儲器模塊

2021-02-23 07:12:38

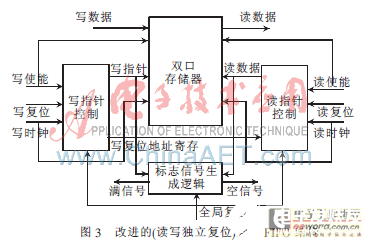

本32X8 FIFO的設計,采用了雙體存儲器的交替讀寫機制,使得在對其中一個存儲器寫操作的同時可以對另一個存儲器進行讀操作;對其中一個存儲器讀操作的同時可以對另一個存儲器進行寫操作。實現了高速數據緩沖,速度比單體存儲器的FIFO提高了一倍。

2021-04-26 06:54:22

解碼器需要一個恒速的傳輸流)。雖然存儲器對同步的要求似乎很小,但當涉及到多個碼流時它可能很顯著。這種同步可以由一個異步FIFO實現。 2) 幀存儲: 幀存儲在這些地方需要:任何暫時的處理如幀率轉換

2011-07-15 09:18:00

我有一個應用程序可能會更好用一個真正的,沒有時鐘的異步fifo,對于年輕人的說服力,這是一種想法,但不需要這個尺寸。http://www.ti.com/lit/ds/symlink

2019-04-23 13:44:46

你好,我當前正在運用ADI公司的AD9954芯片,我想用它自帶的內部存儲器來產生任意波形,可是搞了10天了還是沒有任何的進展,在此希望能夠得到ADI技術人員的幫助,或是給我們些有關內部存儲器的程序

2018-11-26 10:07:00

打算用line-in或者mic-in錄制一段10s音頻,然后再播放,這10s音頻臨時存儲在ddr存儲器,需要怎么編程,不是很懂。

2019-06-17 06:08:10

怎么設計一種面向嵌入式存儲器測試和修復的IIP?如何解決設計和制造過程各個階段的良品率問題?嵌入式存儲器測試和修復技術的未來趨勢是什么?STAR存儲器系統的功能是什么?

2021-04-15 06:05:51

為什么要設計一種異步FIFO?異步FIFO的設計原理是什么?怎樣去設計一種異步FIFO?

2021-06-18 09:20:29

怎樣去設計一種高效率音頻功率放大器?如何對高效率音頻功率放大器進行測試驗證?

2021-06-02 06:11:23

檢錯與糾錯的原理是什么?基于CPLD的容錯存儲器的設計實現

2021-05-07 06:02:42

網絡存儲器技術是如何產生的?怎樣去設計一種網絡存儲器?

2021-05-26 07:00:22

座跨越溝壑的橋梁--一種非易失性的RAM。當一個電場被加到鐵電晶體時,中心原子順著電場的方向在晶體里移動。當原子移動時,它通過一個能量壁壘,從而引起電荷擊穿。內部電路感應到電荷擊穿并設置存儲器。移去電場后

2011-11-19 11:53:09

座跨越溝壑的橋梁--一種非易失性的RAM。當一個電場被加到鐵電晶體時,中心原子順著電場的方向在晶體里移動。當原子移動時,它通過一個能量壁壘,從而引起電荷擊穿。內部電路感應到電荷擊穿并設置存儲器。移去電場后

2011-11-21 10:49:57

首先介紹異步FIFO 的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法; 在傳統設計的基礎上提出一種新穎的電路結構并對其進行綜合仿真和FPGA 實現。

2009-04-16 09:25:29 46

46 介紹了PCI 9054 接口芯片的性能及數據傳輸特點,提出了一種基于PCI 9054 外擴異步FIFO(先進先出)的FPGA(現場可編程門陣列)實現方法。由于PCI 9054 內部FIFO存儲器主要用于數據

2010-01-06 15:20:10 44

44 本文主要研究了用FPGA 芯片內部的EBRSRAM 來實現異步FIFO 設計方案,重點闡述了異步FIFO 的標志信號——空/滿狀態的設計思路,并且用VHDL 語言實現,最后進行了仿真驗證。

2010-01-13 17:11:58 40

40 介紹了異步FIFO在Camera Link接口中的應用,將Camera Link接口中的幀有效信號FVAL和行有效信號LVAL引入到異步FIFO的設計中。分析了FPGA中設計異步FIFO的難點,解決了異步FIFO設計中存在的兩

2010-07-28 16:08:06 32

32 摘要:使用FIFO同步源自不同時鐘域的數據是在數字IC設計中經常使用的方法,設計功能正確的FUFO會遇到很多問題,探討了兩種不同的異步FIFO的設計思路。兩種思路

2006-03-24 12:58:33 680

680

摘要:首先介紹異步FIFO的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法;在傳統設計的基礎上提出一種新穎的電路結構并對其進行

2009-06-20 12:46:50 3667

3667

FPGA設計的高速FIFO電路技術

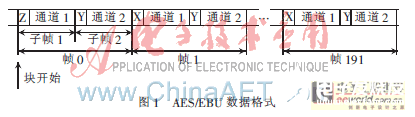

本文主要介紹高速FIFO電路在數據采集系統中的應用,相關電路主要有高速A/D轉換器、FPGA、SDRAM存儲器等。圖1為本方案的結構框圖。在大容量

2010-05-27 09:58:59 2226

2226

文中給出了異步FIFO的實現代碼和FPGA與DSP的硬件連接電路。經驗證,利用異步FIFO的方法,在FPGA與DSP通信中的應用,具有傳輸速度快、穩定可靠、實現方便的優點。

2011-12-12 14:28:22 51

51 異步SRAM存儲器接口電路設計(Altera FPGA開發板)如圖所示:

2012-08-15 14:37:05 3862

3862

異步FIFO結構及FPGA設計,解決亞穩態的問題

2015-11-10 15:21:37 4

4 異步FIFO在FPGA與DSP通信中的運用

2016-05-19 11:17:11 0

0 基于異步FIFO在FPGA與DSP通信中的運用

2017-10-19 10:30:56 10

10 摘要 利用異步FIFO實現FPGA與DSP進行數據通信的方案。FPGA在寫時鐘的控制下將數據寫入FIFO,再與DSP進行握手后,DSP通過EMIFA接口將數據讀入。文中給出了異步FIFO的實現

2017-10-30 11:48:44 1

1 提出了一種基于FPGA實現的PCI-I2S音頻系統方法。通過在FPGA中將PCI軟核、FIFO以及設計的接口電路等相結合,在FPGA上實現了 PCI、I2C、I2S等多種總線,并且結合音頻解碼器實現

2017-11-17 08:17:52 2562

2562

在現代電路設計中,一個系統往往包含了多個時鐘,如何在異步時鐘間傳遞數據成為一個很重要的問題,而使用異步FIFO可以有效地解決這個問題。異步FIFO是一種在電子系統中得到廣泛應用的器件,文中介紹了一種基于FPGA的異步FIFO設計方法。使用這種方法可以設計出高速、高可靠的異步FIFO。

2018-07-17 08:33:00 7873

7873

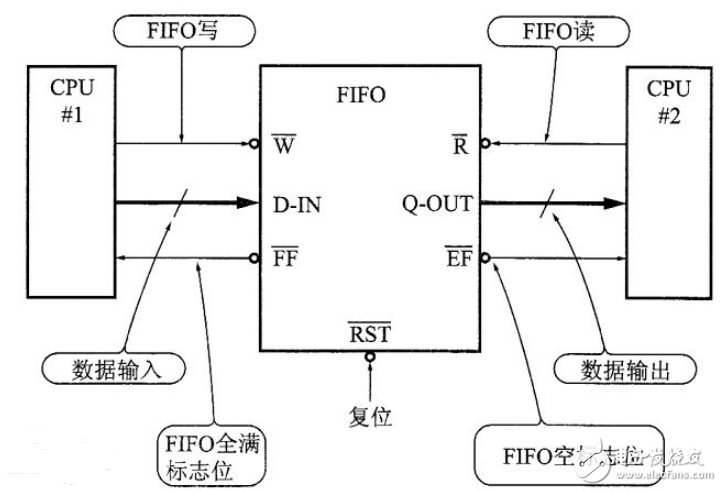

FIFO( First In First Out)簡單說就是指先進先出。由于微電子技術的飛速發展,新一代FIFO芯片容量越來越大,體積越來越小,價格越來越便宜。作為一種新型大規模集成電路,FIFO芯片以其靈活、方便、高效的特性。

2017-12-06 14:29:31 10173

10173

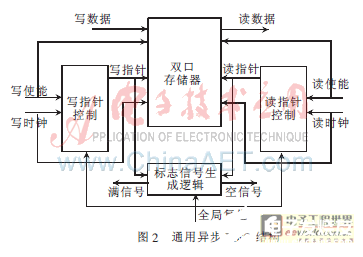

問題一種簡便、快捷的解決方案。使用異步FIFO可以在兩個不同時鐘系統之間快速而方便地傳輸實時數據。在網絡接口、圖像處理等方面,異步FIFO得到了廣泛的應用。 異步FIFO是一種先進先出的電路,使用在需要產時數據接口的部分,用來存儲、緩沖在兩個異步時鐘

2018-02-07 14:22:54 0

0 本文主要介紹了fifo存儲器芯片型號有哪些?FIFO存儲器是系統的緩沖環節,如果沒有FIFO存儲器,整個系統就不可能正常工作,它主要有幾方面的功能:1)對連續的數據流進行緩存,防止在進機和存儲操作

2018-04-08 16:11:32 23894

23894

異步FIFO(Fist-In-First-Out)是一種先入先出的數據緩沖器[1]。由于可以很好地解決跨時鐘域問題和不同模塊之間的速度匹配問題,而被廣泛應用于全局異步局部同步[2](Globally

2018-06-19 15:34:00 2870

2870

介紹了TI公司TMS320C67系列DSP的EMIF(外部存儲器接口)與異步FIFO(先進先出)存儲器的硬件接口設計,著重描述了用EDMA(擴展的直接存儲器訪問)方式讀取FIFO存儲器數據的軟件設計

2019-07-31 16:40:47 20

20 本文檔的主要內容詳細介紹的是FIFO存儲器的尺寸圖免費下載。

2019-08-15 08:00:00 2

2 問題的有效方法。異步FIFO是一種在電子系統中得到廣泛應用的器件,多數情況下它都是以一個獨立芯片的方式在系統中應用。本文介紹一種充分利用FPGA內部的RAM資源,在FPGA內部實現異步FIFO模塊的設計方法。這種異步FIFO比外部 FIFO 芯片更能提高系統的穩定性。

2020-07-21 17:09:36 1326

1326

在FPGA開發板上都有幾種不同的存儲器,比如SDRAM,FLASH,EPCS,還有內部

2020-10-09 11:41:41 2921

2921 FIFO 是英文 First In First Out 的縮寫,是一種先進先出的數據緩存器,它與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序的讀出數據,其數據地址由內部讀寫指針自動加 1 完成,不能像普通存儲器那樣可以由地址線決定讀取或寫入某個指定的地址。

2020-12-22 13:11:00 1

1 提出了一種節能并可升級的異步FIFO的FPGA實現。此系統結構利用FPGA內自身的資源控制時鐘的暫停與恢復,實現了高能效、高工作頻率的數據傳輸。該系統在Xilinx的VC4VSX55芯片中實現,實際

2021-02-02 15:15:00 16

16 FIFO是FPGA處理跨時鐘和數據緩存的必要IP,可以這么說,只要是任意一個成熟的FPGA涉及,一定會涉及到FIFO。但是我在使用異步FIFO的時候,碰見幾個大坑,這里總結如下,避免后來者入坑。

2021-03-12 06:01:34 12

12 一:fifo是什么 FIFO的完整英文拼寫為FirstIn First Out,即先進先出。FPGA或者ASIC中使用到的FIFO一般指的是對數據的存儲具有先進先出特性的一個存儲器,常被用于數據

2021-03-12 16:30:48 2796

2796

1.定義 FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,他與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序

2021-04-09 17:31:42 4697

4697

入的指令先完成并引退,跟著才執行第二條指令。 1.什么是FIFO? FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,他與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序的讀出數據,其數據地址由內部讀寫指針自動加1完成

2021-12-17 18:29:31 10

10 異步fifo詳解 一. 什么是異步FIFO FIFO即First in First out的英文簡稱,是一種先進先出的數據緩存器,與普通存儲器的區別在于沒有外部讀寫的地址線,缺點是只能順序的讀取

2022-12-12 14:17:41 2790

2790 FIFO(First In First Out )先入先出存儲器,在FPG設計中常用于跨時鐘域的處理,FIFO可簡單分為同步FIFO和異步FIFO。

2023-04-25 15:55:28 2893

2893

FIFO是異步數據傳輸時常用的存儲器,多bit數據異步傳輸時,無論是從快時鐘域到慢時鐘域,還是從慢時鐘域到快時鐘域,都可以使用FIFO處理。

2023-05-26 16:12:49 978

978

異步FIFO主要由五部分組成:寫控制端、讀控制端、FIFO Memory和兩個時鐘同步端

2023-05-26 16:17:20 911

911

異步FIFO包含"讀"和"寫“兩個部分,寫操作和讀操作在不同的時鐘域中執行,這意味著Write_Clk和Read_Clk的頻率和相位可以完全獨立。異步FIFO

2023-09-14 11:21:45 545

545

簡單的一種,其特點是輸入和輸出都與時鐘信號同步,當時鐘到來時,數據總是處于穩定狀態,因此容易實現數據的傳輸和存儲。 而異步FIFO則是在波形的上升沿和下降沿上進行處理,在輸入輸出端口處分別增加輸入和輸出指針,用于管理數據的讀寫。異步FIFO的輸入和輸出可同時進行,中間可以

2023-10-18 15:23:58 790

790 請問異步FIFO的溢出操作時怎么樣判斷的? 異步FIFO是數據傳輸的一種常用方式,在一些儲存器和計算機系統中,常常會用到異步FIFO。作為一種FIFO,異步FIFO經常面臨兩種情況:溢出

2023-10-18 15:28:41 299

299 ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 1.1片上存儲(on-chip ram) ? ? ? ? ? ? ? 在實際應用中任何場合都離不開數據,只要有數據的地方就有存儲器,一般存儲分為了2種,一種時可以讀寫,一種時只讀

2023-11-17 14:00:02 179

179

電子發燒友App

電子發燒友App

評論