本文對無線傳感器網(wǎng)絡(luò)體系結(jié)構(gòu)進行了較為深入的研究,從物理體系結(jié)構(gòu)、軟件體系結(jié)構(gòu)和通信體系結(jié)構(gòu)三個層面進行了分析。

2011-11-03 16:24:51 7582

7582

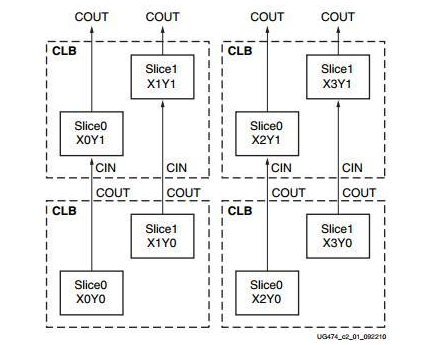

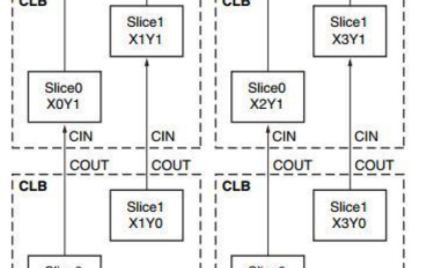

Xilinx_FPGA_內(nèi)部結(jié)構(gòu)深入分析存儲單元存儲單元可以配置為D觸發(fā)器,就是我們常說的FF,Xilinx稱之為FD;也可以配置為鎖存器,Xilinx稱之為LD。輸出和三態(tài)通路各有一對寄存器外加一

2012-08-02 22:48:10

關(guān)于無線火災(zāi)報警系統(tǒng)的體系結(jié)構(gòu)研究,不看肯定后悔

2021-06-01 06:55:33

VITE標(biāo)準(zhǔn)體系結(jié)構(gòu)分析VITE實現(xiàn)體系結(jié)構(gòu)VITE核心信息模型結(jié)構(gòu)

2021-05-12 06:31:48

ARMSOC 體系結(jié)構(gòu)

2016-11-22 10:54:31

介紹ARM 的片上系統(tǒng)體系結(jié)構(gòu)

2016-03-31 23:03:45

本帖最后由 eehome 于 2013-1-5 09:52 編輯

ARM SoC體系結(jié)構(gòu)(中文版)

2012-10-26 21:36:12

ARM SoC體系結(jié)構(gòu)。

2020-01-28 13:57:51

ARM7體系結(jié)構(gòu)

2012-01-10 08:58:29

;><strong>ARM體系結(jié)構(gòu)與編程<br/></strong></font&

2009-11-24 17:19:16

跟蹤支持是一種體系結(jié)構(gòu)擴展,通常使用嵌入式跟蹤宏單元(ETM)實現(xiàn)。

ETM構(gòu)造與處理器的操作相對應(yīng)的實時跟蹤流。

跟蹤流是本地存儲在嵌入式跟蹤緩沖器(ETB)中以供獨立下載和分析,還是通過跟蹤端口

2023-08-11 06:52:28

本帖最后由 eehome 于 2013-1-5 09:47 編輯

ARM體系結(jié)構(gòu)和編程

2012-12-04 03:35:56

ARM體系結(jié)構(gòu)是怎樣的?

2021-11-05 06:40:10

ARM體系結(jié)構(gòu)包含大量功能,這些功能被描述為可選或定義的實施。來自平臺操作系統(tǒng)供應(yīng)商的反饋表明這種可變性對于系統(tǒng)代碼的開發(fā)人員來說是一個實質(zhì)性的問題,由于操作系統(tǒng)必須滿足各種不同的系統(tǒng)配置,導(dǎo)致開發(fā)

2023-08-08 07:40:40

本文介紹了ARM中可用的硬件同步原語體系結(jié)構(gòu),并提供了系統(tǒng)級程序員如何使用它們的示例。

2023-08-02 10:59:00

ARM嵌入式體系結(jié)構(gòu)與接口技術(shù).pdf{:1:}{:1:}{:1:}ARM SoC體系結(jié)構(gòu)(中文版).pd

2013-03-23 16:04:52

ARM的體系結(jié)構(gòu)是由哪些部分組成的?ARM的編程模式有哪幾種?為什么要劃分這幾種編程模式呢?

2021-10-21 06:23:36

包含一個簡短的介紹,以幫助讀者。與體系結(jié)構(gòu)兼容的實現(xiàn)必須

遵守本規(guī)范中的所有規(guī)則。

一些體系結(jié)構(gòu)規(guī)則伴隨著解釋為什么指定體系結(jié)構(gòu)的基本原理陳述

事實就是這樣。基本原理陳述用字母X表示。

有些部分

2023-08-02 10:55:31

ARM裸機全集之ARM體系結(jié)構(gòu)

2021-07-01 06:12:57

本手冊中的體系結(jié)構(gòu)描述使用了與Armv8體系結(jié)構(gòu)相同的術(shù)語。有關(guān)該術(shù)語的更多信息,請參閱Armv8-A架構(gòu)配置文件Armv8 Arm?架構(gòu)參考手冊A部分的介紹。此外,在適當(dāng)?shù)那闆r下使用AArch64

2023-08-11 07:45:48

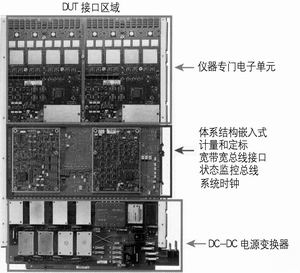

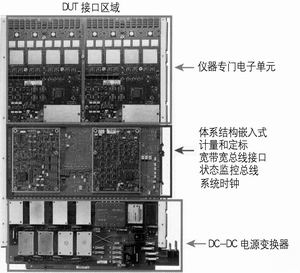

ATE開放式體系結(jié)構(gòu)的硬件基礎(chǔ),總結(jié)的太棒了

2021-05-31 06:16:22

SoCFPGA器件在一個器件中同時集成了處理器和FPGA體系結(jié)構(gòu)。將兩種技術(shù)合并起來具有很多優(yōu)點,包括更高的集成度、更低的功耗、更小的電路板面積,以及處理器和FPGA之間帶寬更大的通信等等。這一同類最佳的器件發(fā)揮了處理器與FPGA系統(tǒng)融合的優(yōu)勢,同時還保留了獨立處理器和FPGA方法的優(yōu)點。

2019-09-26 07:59:27

本文檔描述了CoreSight體系結(jié)構(gòu),平臺和系統(tǒng)使用。

2023-08-09 06:08:20

本規(guī)范描述了電源策略單元(PPU)體系結(jié)構(gòu)。它定義了PPU體系結(jié)構(gòu)的1.1版本。

PPU規(guī)范的1.1版增加了對操作模式的支持。由于功能或更高粒度的功率控制原因,這使得能夠支持特定于組件的功率模式

2023-08-11 06:14:35

本增補件是Armv9-A體系結(jié)構(gòu)的Arm?體系結(jié)構(gòu)參考手冊增補件輪廓本書介紹了Armv9-A體系結(jié)構(gòu)擴展,因此必須與Arm?體系結(jié)構(gòu)參考手冊一起閱讀A型架構(gòu)。

2023-08-08 07:07:05

本規(guī)范定義了基于Arm A配置文件體系結(jié)構(gòu)的處理器的動態(tài)測量信任根(DRTM)體系結(jié)構(gòu)。本規(guī)范基于TCG D-RTM體系結(jié)構(gòu)[4]的概念,但作為一個獨立的獨立文檔發(fā)揮作用。它使用了TCG體系結(jié)構(gòu)

2023-08-08 07:45:00

Menu軟件體系結(jié)構(gòu)的基本概念幾種常見的嵌入式軟件結(jié)構(gòu)輪轉(zhuǎn)結(jié)構(gòu)(round-robin architecture)Example特點帶有中斷的輪轉(zhuǎn)結(jié)構(gòu)( round-robin

2021-12-17 06:52:59

第二章 ARM微處理器概述與編程模型ARM體系結(jié)構(gòu)及其發(fā)展歷史處理器的體系結(jié)構(gòu)處理器微架構(gòu) Microarchitecture指令集體系結(jié)構(gòu) Architecture幾種常見的指令集X86Inter

2021-12-14 07:13:43

rfid技術(shù)是什么?rfid技術(shù)有哪些應(yīng)用?RFID閱讀器的軟件體系結(jié)構(gòu)是怎樣構(gòu)成的?

2021-05-26 06:52:32

STM32標(biāo)準(zhǔn)外設(shè)庫是什么?有什么優(yōu)勢?STM32F10xxx標(biāo)準(zhǔn)外設(shè)庫體系結(jié)構(gòu)由什么組成?功能是什么?

2021-09-27 06:56:59

SoC設(shè)計中的片上通信體系結(jié)構(gòu)研究,不看肯定后悔

2021-05-26 06:30:47

Stratix III FPGA與Xilinx Virtex-5的體系結(jié)構(gòu)對比Stratix III FPGA與Xilinx Virtex-5的性能對比

2021-05-07 07:00:14

。該體系結(jié)構(gòu)為軟件開發(fā)人員公開了一個通用的指令集和工作流程,也稱為程序員模型。這有助于確保架構(gòu)的不同實現(xiàn)之間的互操作性,以便軟件可以在不同的 Arm 設(shè)備上運行。本指南為任何對此感興趣的人介紹了 Arm

2023-08-01 14:35:14

模塊一知識點1.了解計算機硬件體系結(jié)構(gòu)2.掌握常見的計算機硬件設(shè)備3.了解計算機軟件體系結(jié)構(gòu)4.掌握主板結(jié)構(gòu)的組成5.了解CPU、內(nèi)存、硬盤的發(fā)展歷程6.掌握CPU、內(nèi)存、硬盤的結(jié)構(gòu)、性能指標(biāo)及相關(guān)

2021-09-17 09:03:49

馮·諾依曼結(jié)構(gòu)的特點是什么?馮·諾依曼計算機體系結(jié)構(gòu)缺陷有哪些?哈佛結(jié)構(gòu)具有哪些特點應(yīng)用場景?

2021-12-24 07:36:10

馮諾依曼計算機體系結(jié)構(gòu)是怎樣組成的?微型系統(tǒng)地結(jié)構(gòu)是怎樣組成的?

2022-02-10 06:15:45

分享一款不錯的基于DSP技術(shù)的汽車定位防盜系統(tǒng)體系結(jié)構(gòu)研究

2021-05-18 07:04:13

HY,我想在xilinx Blockset中估計FFT7.1塊的各個體系結(jié)構(gòu)的資源。有沒有辦法做到這一點?當(dāng)我嘗試使用“資源估計器”-Block時,結(jié)果總是43個IOB。問候Jan以上來自于谷歌翻譯

2018-10-16 07:21:32

可重構(gòu)體系結(jié)構(gòu)分為哪幾種?典型動態(tài)可重構(gòu)系統(tǒng)結(jié)構(gòu)有哪幾種?動態(tài)可重構(gòu)系統(tǒng)有哪些應(yīng)用實例?

2021-04-28 06:13:00

體系結(jié)構(gòu)能夠有效地實現(xiàn)并行運算。數(shù)字濾波器:數(shù)字濾波器通常用于修正和改變時域或頻域中信號的特性。最為普通的數(shù)字濾波器就是線性時間不變(LinearTime-Invariant,LTI)濾波器。通常分為有限

2021-12-15 06:30:00

在虛擬機部署樹莓派系統(tǒng)后報 軟件包體系結(jié)構(gòu)(armhf)與本機系統(tǒng)體系結(jié)構(gòu)(i386)不符

2022-03-30 17:59:51

如何實現(xiàn)在Linux操作系統(tǒng)下ARM體系結(jié)構(gòu)的處理器與DSP的數(shù)據(jù)通信?

2021-05-28 06:11:36

目錄一. 嵌入式體系結(jié)構(gòu)二. 開發(fā)過程中的分工三. 嵌入式軟件體系結(jié)構(gòu)四. 嵌入式Linux 一. 嵌入式體系結(jié)構(gòu)這本書的前三章脈絡(luò)很清晰, 按照嵌入式系統(tǒng)結(jié)構(gòu)從下往上, 從底層的硬件, 電路

2021-11-05 07:10:25

目錄一、嵌入式微處理器體系結(jié)構(gòu)1、馮諾依曼體系結(jié)構(gòu)2、哈弗體系結(jié)構(gòu)二、嵌入式系統(tǒng)的硬件結(jié)構(gòu)1、嵌入式微控制器MCU(CPU+片內(nèi)內(nèi)存+片內(nèi)外設(shè))2、嵌入式微處理器MPU(CPU)3、嵌入式數(shù)字信號

2021-11-08 06:57:02

工業(yè)以太網(wǎng)發(fā)展?fàn)顩r是怎樣的工業(yè)以太網(wǎng)協(xié)議可以分成哪幾類體系結(jié)構(gòu)?在單個FPGA平臺上采用多種工業(yè)以太網(wǎng)標(biāo)準(zhǔn)進行設(shè)計

2021-04-15 06:48:39

Microwindows最新版本0. 9有哪些特性?怎樣去設(shè)計Microwindows的體系結(jié)構(gòu)?Microwindows在仿真環(huán)境下有哪些應(yīng)用?

2021-04-27 06:05:26

PCI總線作為處理器系統(tǒng)的局部總線,主要目的是為了連接外部設(shè)備,而不是作為處理器的系統(tǒng)總線連接Cache和主存儲器。但是PCI總線、系統(tǒng)總線和處理器體系結(jié)構(gòu)之間依然存在著緊密的聯(lián)系。

2019-08-06 06:02:46

②和③D.①、②和③62、D[解析] 體系結(jié)構(gòu)描述系統(tǒng)的分解、全局控制流、錯誤處理策略、子系統(tǒng)間的通信協(xié)議和接口、系統(tǒng)安全策略等系統(tǒng)的整體架構(gòu),不關(guān)心子系統(tǒng)的詳細設(shè)計和實現(xiàn)。輸入信號預(yù)處理、主控制過程和網(wǎng)絡(luò)接口等都屬于體系結(jié)構(gòu)設(shè)計的范疇。例2?? 系統(tǒng)分析模型應(yīng)明確體現(xiàn)的.

2021-12-22 06:09:49

今天和大家來聊聊 嵌入式系統(tǒng)需求分析與體系結(jié)構(gòu)設(shè)計的一些基礎(chǔ)知識:1.1軟件需求分析1.1.1 關(guān)于選擇裸機開發(fā)還是基于實時操作系統(tǒng)一是采用在裸機上直接開發(fā)的方式,且關(guān)鍵部分采用匯編語言編寫,可以保證該控制系統(tǒng)的實時性;二是由于該軟件系統(tǒng)由多種周期的...

2021-12-22 08:10:03

萌新求助,求大佬詳細介紹ARM Cortex -M體系結(jié)構(gòu)

2021-10-25 09:06:56

第一部分 IO基礎(chǔ)知識計算機系統(tǒng)軟件體系結(jié)構(gòu)采用一種層的結(jié)構(gòu),有人說過一句名言:“Any problem in computer science can be solved by anther

2022-01-07 06:42:57

計算機網(wǎng)絡(luò)體系結(jié)構(gòu)的通信協(xié)議有哪幾層?是如何劃分的?

2021-09-30 08:22:31

計算機軟件體系結(jié)構(gòu)由哪幾部分組成?

2021-10-25 08:24:43

怎樣去設(shè)計嵌入式系統(tǒng)軟件體系結(jié)構(gòu)?

2021-04-27 07:18:46

微處理器體系結(jié)構(gòu)由哪幾部分組成?超標(biāo)量處理器的微體系結(jié)構(gòu)由哪幾部分組成?

2022-02-28 07:31:47

面向計算體系結(jié)構(gòu)的電機控制,看完你就懂了

2021-05-18 07:03:03

軟件體系結(jié)構(gòu)對軟件的穩(wěn)定性、軟件維護和軟件演化等各方面的性能很重要。該文引入構(gòu)件運算的方法描述體系結(jié)構(gòu),分析調(diào)用運算、協(xié)作運算和條件運算的相關(guān)性和構(gòu)件的復(fù)雜度

2009-04-23 10:28:01 18

18 本文以C4ISR 體系結(jié)構(gòu)框架2.0 為體系結(jié)構(gòu)的描述規(guī)范,在分析C4ISR 體系結(jié)構(gòu)和我軍軍事信息系統(tǒng)體系結(jié)構(gòu)的基礎(chǔ)上,總結(jié)了體系結(jié)構(gòu)設(shè)計的主要技術(shù)與方法,結(jié)合C4ISR 體系結(jié)構(gòu)的通用

2009-06-11 09:14:28 17

17

ARM SoC體系結(jié)構(gòu)(中文版)的主要內(nèi)容:

第1章 處理器設(shè)計導(dǎo)論

第2章 ARM體系結(jié)構(gòu)

第3章 ARM匯編語言編程

第4章 ARM的組織和實現(xiàn)

第5章 ARM的指令集

2009-07-25 17:53:02 0

0 選擇適合您FPGA系統(tǒng)的I/O體系結(jié)構(gòu):即使在幾年前, 設(shè)計師還主要是把FPGA作為設(shè)計原型的工具。但隨著近十年來FPGA 數(shù)據(jù)速率的迅速提高, 現(xiàn)在已完全能與CMOS ASIC相匹敵。系統(tǒng)性能的急

2009-11-20 17:41:32 21

21 本文圍繞作戰(zhàn)分析仿真系統(tǒng)的體系結(jié)構(gòu)的分析和設(shè)計進行了相關(guān)的研究。這些研究和實現(xiàn)工作是當(dāng)前作戰(zhàn)分析仿真系統(tǒng)研究的一個新課題,為相關(guān)研究提供了基于Web 服務(wù)的新思路和

2009-12-30 11:01:02 16

16 ARM體系結(jié)構(gòu)與編程

2010-02-11 09:35:32 157

157 在對B/S結(jié)構(gòu)和C/S結(jié)構(gòu)進行充分分析比較的情況下,簡述了今后發(fā)展的前景,并提出了一種新的體系結(jié)構(gòu)。

2006-03-11 13:22:49 1161

1161

開放式體系結(jié)構(gòu)的概念在2002

2006-03-13 13:59:08 1721

1721

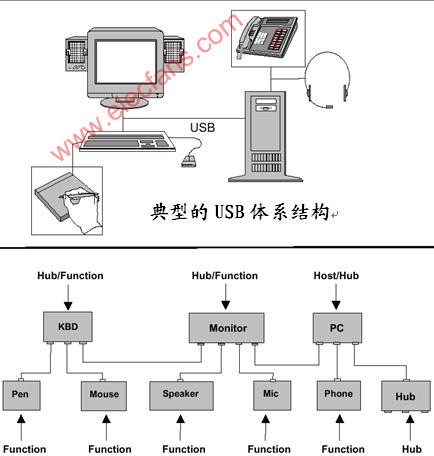

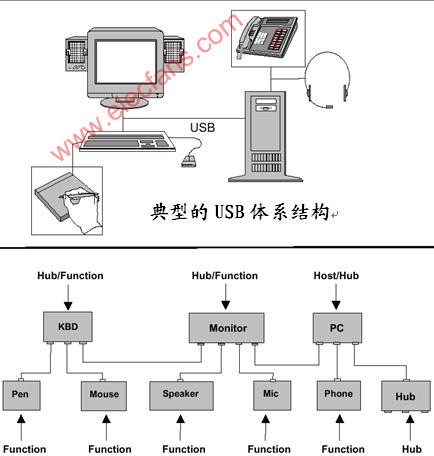

USB體系結(jié)構(gòu)概述

本章主要內(nèi)容是關(guān)于USB的概述和一些關(guān)鍵的概念。USB是一種電纜總線,支持在主機和各式各樣的即插即

2009-04-15 20:43:01 1763

1763

LTE體系結(jié)構(gòu)

LTE體系結(jié)構(gòu)可以借助SAE 體系結(jié)構(gòu)來做詳細描述。在SAE 體系結(jié)構(gòu)中,RNC部分功能、GGSN、SGSN 節(jié)點將被融合為一個新的節(jié)點,

2009-06-16 13:09:41 9535

9535 網(wǎng)絡(luò)體系結(jié)構(gòu),什么是網(wǎng)絡(luò)體系結(jié)構(gòu)

通過通信信道和設(shè)備互連起來的多個不同地理位置的計算機系統(tǒng),要使其能協(xié)同工作實現(xiàn)信息交換和資源共享

2010-04-06 16:30:05 1607

1607 摘要:以流計算模型為基礎(chǔ)的流體系結(jié)構(gòu),是面向未來的單片上集成超10億只晶體管和上千ALU時代的新型體系結(jié)構(gòu),正成為微處理器體系結(jié)構(gòu)研究關(guān)注的前沿焦點之一。首先分析流計算的背景;總結(jié)現(xiàn)有的具有代表性的流體系結(jié)構(gòu),并對它們的結(jié)構(gòu)、執(zhí)行模式、并行性、

2011-02-28 09:56:24 51

51 研究體系結(jié)構(gòu)需要一套特定的開發(fā)工具,國外已經(jīng)開發(fā)了多種體系結(jié)構(gòu)工具,其中SA(System Architect)是先進成熟的體系結(jié)構(gòu)分析、設(shè)計、可視化建模與驗證工具,在體系結(jié)構(gòu)研究中發(fā)揮

2011-07-11 10:33:32 0

0 軟件通信體系結(jié)構(gòu)是美國國防部的聯(lián)合計劃辦公室JPO發(fā)布的關(guān)于軟件無線電體系架構(gòu)的唯一標(biāo)準(zhǔn),當(dāng)前基于軟件通信體系結(jié)構(gòu)的波形組件的開發(fā)存在可移植性差、重用性低等問題。論文

2011-09-09 12:08:06 43

43 《ARM體系結(jié)構(gòu)與程序設(shè)計》是ARM體系結(jié)構(gòu)與程序設(shè)計的一本實用指導(dǎo)書籍,通過案例詳細介紹了ARM體系結(jié)構(gòu)與程序設(shè)計,案例中的程序都取自實際的項目,且對程序有詳細注解。

2011-10-27 16:37:27 2269

2269 關(guān)于家庭網(wǎng)絡(luò)體系結(jié)構(gòu)與中間件的闡述

2011-11-09 18:00:27 35

35 無線傳感器網(wǎng)絡(luò)的體系結(jié)構(gòu)及應(yīng)用......

2016-01-04 15:26:58 11

11 ARM體系結(jié)構(gòu)(1),有需要的朋友下來看看。

2016-01-08 14:46:55 0

0 ARM SoC體系結(jié)構(gòu),非常實用和贊的文檔。

2016-01-15 16:07:06 3

3 ARM體系結(jié)構(gòu),感興趣的小伙伴們可以看看。

2016-11-08 18:13:29 3

3 多核ARM體系結(jié)構(gòu),很不錯的資料

2017-04-11 10:53:00 0

0 ARM7體系結(jié)構(gòu)的詳細介紹

2017-05-03 09:21:40 29

29 ARM體系結(jié)構(gòu)和應(yīng)用系統(tǒng)設(shè)計示例

2017-10-30 09:38:26 4

4 會出現(xiàn)由于內(nèi)部組件失效或外部攻擊而導(dǎo)致的級聯(lián)故障乃至系統(tǒng)崩潰。首次將軟件系統(tǒng)視為復(fù)雜系統(tǒng),對軟件體系結(jié)構(gòu)的脆性進行相關(guān)分析,并結(jié)合數(shù)據(jù)抽象和面向?qū)ο箫L(fēng)格的軟件體系結(jié)構(gòu),通過蟻群算法及GROD算法指出該體系結(jié)構(gòu)脆性

2017-11-24 10:34:24 15

15 based methodology)的體系結(jié)構(gòu)建模方法,構(gòu)建了相應(yīng)的偵察衛(wèi)星應(yīng)用信息鏈體系結(jié)構(gòu)模型。本文首先分析了偵察衛(wèi)星應(yīng)用信息鏈的組成結(jié)構(gòu)和任務(wù)活動,爾后依據(jù)DoDAF體系結(jié)構(gòu)的設(shè)計步驟和偵察

2018-01-10 16:58:13 1

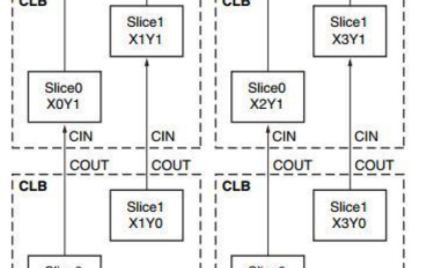

1 Xilinx UltraScale?體系結(jié)構(gòu)包括高性能FPGA、MPSOC和RFSOC系列,這些系列解決了廣泛的系統(tǒng)需求,重點是通過大量創(chuàng)新技術(shù)進步降低總功耗。

2019-02-22 10:53:23 18

18 Xilinx的FPGA的基本結(jié)構(gòu)是一樣的,主要由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核等。

2019-06-11 14:28:17 3600

3600

《ARM體系結(jié)構(gòu)與編程》分14章對ARM處理器的體系結(jié)構(gòu)、指令系統(tǒng)和開發(fā)工具作了比較全面的介紹。

2019-11-25 09:18:57 1660

1660

在面試中經(jīng)常會問MySQL的體系結(jié)構(gòu),接下來詳細分析MySQL的體系結(jié)構(gòu)之前先理解數(shù)據(jù)庫和實例兩個概念。

2020-05-03 17:28:00 2014

2014 Xilinx7系列FPGA的體系結(jié)構(gòu)具有靈活的內(nèi)部內(nèi)存資源,可以配置為各種不同的大小。本白皮書詳細介紹了可用的功能,說明了各種可用內(nèi)存大小,并顯示了使用不同資源執(zhí)行不同大小內(nèi)存功能的利弊。

2020-12-09 16:15:00 8

8 微處理器體系結(jié)構(gòu)說明。

2021-04-12 11:42:14 13

13 《微處理器體系結(jié)構(gòu)》適合作為高等院校集成電路設(shè)計相關(guān)專業(yè)工程碩士的教材,并可以作為微處理器硬件與軟件設(shè)計相關(guān)專業(yè)高年級本科生和研究生的教材。

《微處理器體系結(jié)構(gòu)》是一本系統(tǒng)介紹各種類型微處理器

2021-04-14 10:29:03 0

0 軟件無線電的體系結(jié)構(gòu)講解免費下載。

2021-04-20 14:13:53 9

9 軟件無線電的體系結(jié)構(gòu)總結(jié)說明。

2021-04-28 09:58:20 9

9 軟件無線電的體系結(jié)構(gòu)說明。

2021-05-31 16:46:27 12

12 Oracle體系結(jié)構(gòu)講解(開關(guān)電源技術(shù)的節(jié)能意義)-該文檔為Oracle體系結(jié)構(gòu)講解文檔,是一份十分不錯的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,,,,,,

2021-09-27 10:27:43 3

3 CSKY體系結(jié)構(gòu)用戶指南

2021-10-08 15:39:31 9

9 《RVfpga:理解計算機體系結(jié)構(gòu)》3.0版本更新上線,掃碼進入官網(wǎng)注冊申請獲取。《RVfpga:理解計算機體系結(jié)構(gòu)》(以下簡稱“《RVfpga》”)是Imagination推出的完整RISC-V

2024-01-18 08:27:31 161

161

電子發(fā)燒友App

電子發(fā)燒友App

評論