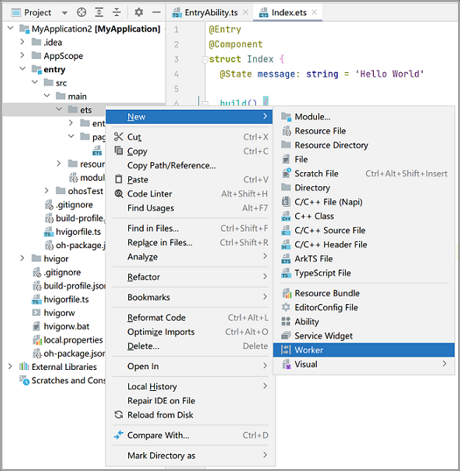

一、CPU密集型任務(wù)開發(fā)指導(dǎo) CPU密集型任務(wù)是指需要占用系統(tǒng)資源處理大量計(jì)算能力的任務(wù),需要長(zhǎng)時(shí)間運(yùn)行,這段時(shí)間會(huì)阻塞線程其它事件的處理,不適宜放在主線程進(jìn)行。例如圖像處理、視頻編碼、數(shù)據(jù)

2024-02-18 10:17:31 628

628

美國(guó)加州時(shí)間2013年1月4日Tensilica今日宣布,推出業(yè)界最小面積,最低功耗的HiFi Mini DSP(數(shù)字信號(hào)處理器)內(nèi)核,該款DSP IP核支持隨時(shí)傾聽的語(yǔ)音觸發(fā)和語(yǔ)音指令功能。這款小面積低功耗

2013-01-05 13:39:00 1915

1915 DSP+FPGA+AD控制系統(tǒng),FPGA負(fù)責(zé)AD7606的采集,將電機(jī)參數(shù)采集后,傳輸至DSP ,DSP將數(shù)據(jù)進(jìn)行變換后輸出PWM進(jìn)而控制電機(jī)的轉(zhuǎn)速。DSP采用TI公司的TMS320F28335

2016-07-18 16:59:22

`DSP28335+FPGA高速實(shí)時(shí)采集系統(tǒng)核心板,經(jīng)過(guò)了一個(gè)月的磨練,DSP和FPGA通訊終于調(diào)試好使了。本人交流qq,956250037`

2015-11-23 11:04:06

1 引言在信息技術(shù)高速發(fā)展的今天,電子系統(tǒng)數(shù)字化已經(jīng)成為有目共睹的趨勢(shì),從傳統(tǒng)應(yīng)用中小規(guī)模芯片構(gòu)造電路系統(tǒng)到廣泛地應(yīng)用單片機(jī),到今天DSP及FPGA在系統(tǒng)設(shè)計(jì)中的應(yīng)用,電子設(shè)計(jì)技術(shù)已邁入了一個(gè)全新

2021-10-29 08:55:40

的加工數(shù)據(jù)輸入FPGA(EP1C6T144C8)內(nèi)部的加工模塊,控制FPGA輸出加工信號(hào)。在系統(tǒng)運(yùn)轉(zhuǎn)的整個(gè)過(guò)程中,DSP還要通過(guò)建于FPGA內(nèi)部的通訊模塊和單片機(jī)交換數(shù)據(jù),獲取有關(guān)人機(jī)界面和諸如限位

2008-06-27 17:02:29

DSP的FPGA的高速數(shù)據(jù)采集系統(tǒng)的研究與設(shè)計(jì),大家可以看看

2015-04-03 21:23:48

,從而幫助將功耗降到最低。因?yàn)镽TC是唯一能與芯片其余部分完全隔離的模塊。它可以在芯片其余部分?jǐn)嚯姇r(shí)被供電,反之亦然。DSP上的其它外設(shè)和模塊的閑置不會(huì)影響RTC。 4.將片內(nèi)模數(shù)轉(zhuǎn)換器(ADC)的時(shí)鐘

2020-09-01 14:39:51

本帖最后由 eehome 于 2013-1-5 09:56 編輯

XC5VLX330大型FPGA開發(fā)驗(yàn)證平臺(tái)ARM + DSP + FPGA高級(jí)通信系統(tǒng)原型開發(fā)平臺(tái)ARM + DSP

2010-12-25 15:47:19

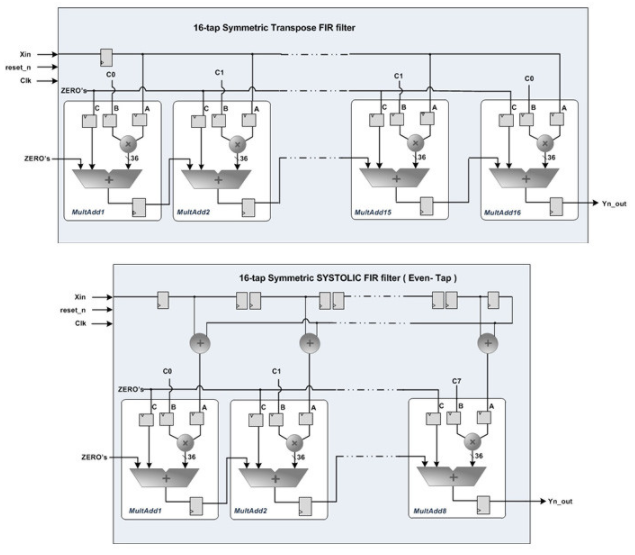

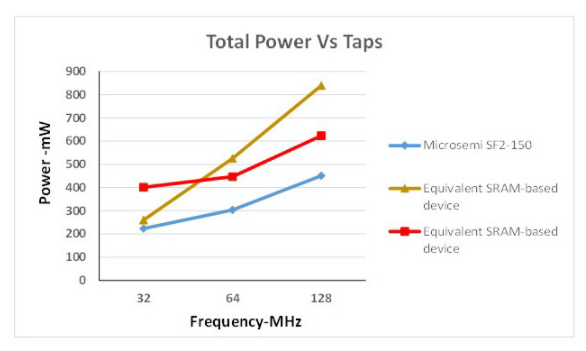

的多通道流量,那么單純基于DSP的硬件系統(tǒng)就可能需要更大的面積,成本或功耗。一個(gè)FPGA僅在一個(gè)器件上就能高提供多達(dá)550個(gè)并行乘法和累加運(yùn)算,從而以較少的器件和較低的功耗提供同樣的性能。但對(duì)于定期系數(shù)更新,決策控制任務(wù)或者高速串行處理任務(wù),FPGA的優(yōu)化程度遠(yuǎn)不如DSP。

2019-08-30 06:31:29

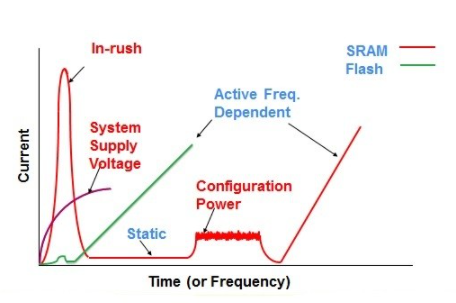

突破FPGA系統(tǒng)功耗瓶頸 FPGA作為越來(lái)越多應(yīng)用的“核心”,其功耗表現(xiàn)也“牽一發(fā)而動(dòng)全身”。隨著工藝技術(shù)的越來(lái)越前沿化,FPGA器件擁有更多的邏輯、存儲(chǔ)器和特殊功能,如存儲(chǔ)器接口、DSP模塊

2018-10-23 16:33:09

在雷達(dá)信號(hào)處理、數(shù)字圖像處理等領(lǐng)域中,信號(hào)處理的實(shí)時(shí)性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢(shì)及DSP芯片在復(fù)雜算法處理上的優(yōu)勢(shì),DSP+FPGA的實(shí)時(shí)信號(hào)處理系統(tǒng)的應(yīng)用越來(lái)越廣泛

2018-12-04 10:39:29

在雷達(dá)信號(hào)處理、數(shù)字圖像處理等領(lǐng)域中,信號(hào)處理的實(shí)時(shí)性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢(shì)及DSP芯片在復(fù)雜算法處理上的優(yōu)勢(shì),DSP+FPGA的實(shí)時(shí)信號(hào)處理系統(tǒng)的應(yīng)用越來(lái)越廣泛

2019-06-19 05:00:08

FPGA是一種可編程的硅芯片,DSP是數(shù)字信號(hào)處理,當(dāng)系統(tǒng)設(shè)計(jì)人員在項(xiàng)目的架構(gòu)設(shè)計(jì)階段就面臨到底采用FPGA還是DSP的重要問(wèn)題。本文將首先分別介紹FPGA和DSP的特點(diǎn),然后再?gòu)膬?nèi)部資源、編程語(yǔ)言

2019-05-07 01:28:40

,半導(dǎo)體技術(shù)將更多晶體管集成到FPGA中,在提高其性能的同時(shí)進(jìn)一步降低自身功耗。那么,DSP又是如何在高性能與低功耗之間尋求最佳平衡點(diǎn)的? FPGA加速滲透 CEVA/德州儀器扛DSP大旗 作為全球

2014-01-09 17:52:31

,限制了器件的靈活布線,因此CPLD利用率較FPGA器件低。6、應(yīng)用范圍的不同 數(shù)字邏輯系統(tǒng)分為兩大類: (1)控制密集型(邏輯密集型),對(duì)數(shù)據(jù)處理能力要求低,但邏輯關(guān)系復(fù)雜,輸入輸出較多,適合

2020-08-28 15:41:47

:FPGA中的寄存器和片上內(nèi)存(BRAM)是屬于各自的控制邏輯的,無(wú)需不必要的仲裁和緩存。2)通信需求:FPGA每個(gè)邏輯單元與周圍邏輯單元的連接在重編程時(shí)就已經(jīng)確定了,并不需要通過(guò)共享內(nèi)存來(lái)通信。計(jì)算密集型

2018-08-16 09:54:23

摘要:在雷達(dá)信號(hào)處理、數(shù)字圖像處理等領(lǐng)域中,信號(hào)處理的實(shí)時(shí)性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢(shì)及DSP芯片在復(fù)雜算法處理上的優(yōu)勢(shì),DSP+FPGA的實(shí)時(shí)信號(hào)處理系統(tǒng)

2019-06-21 05:00:04

,適用于控制密集型系統(tǒng); FPGA邏輯能力較弱但寄存器多,適于數(shù)據(jù)密集型系統(tǒng)。 CPLD和FPGA的優(yōu)點(diǎn): 1.規(guī)模越來(lái)越大,實(shí)現(xiàn)功能越來(lái)越強(qiáng),同時(shí)可以實(shí)現(xiàn)系統(tǒng)集成。 2.研制開發(fā)費(fèi)用低,不承擔(dān)投

2020-07-16 10:46:21

; Xplorer和TCL腳本操作實(shí)例;動(dòng)手實(shí)例18. Smart Guide操作實(shí)例;演示實(shí)例第二天? 課程目標(biāo)通過(guò)本天課程的學(xué)習(xí),掌握DSP系統(tǒng)設(shè)計(jì)流程以及在FPGA

2009-07-21 09:22:42

存儲(chǔ)較長(zhǎng)時(shí)間的擾動(dòng)信號(hào)。LCD模塊采用的是3.3 V單電源供電的320x240大屏幕點(diǎn)陣液晶ZXM320240E1,有足夠的空間將多路的情況同時(shí)顯示在屏幕上,而且由于系統(tǒng)選用FPGA的管腳電壓為

2020-09-04 09:56:23

在高速數(shù)字設(shè)計(jì)中使用TDR

2019-07-23 12:28:09

在高清晰LCD HDTV 中使用Cyclone III FPGA引言當(dāng)今的液晶顯示(LCD) 技術(shù)在高清晰電視(HDTV) 領(lǐng)域得到了廣泛應(yīng)用,其挑戰(zhàn)在于如何獲得更高的分辨率,實(shí)現(xiàn)更快的數(shù)據(jù)速率

2008-10-16 15:44:08

系統(tǒng)設(shè)計(jì)人員在使用FPGA時(shí)通常要考慮哪些功耗?成功的低功耗設(shè)計(jì)是取決于結(jié)構(gòu)還是工藝?

2021-05-08 07:48:13

描述此參考設(shè)計(jì)面向目前使用 FPGA 或 ASIC 將高速數(shù)據(jù)轉(zhuǎn)換器連接到基帶處理器的寬帶接收器系統(tǒng)開發(fā)人員,他們需要縮短產(chǎn)品上市時(shí)間,同時(shí)增強(qiáng)性能并大大降低成本、功率和尺寸。此參考設(shè)計(jì)包括首個(gè)廣泛

2018-09-20 09:07:06

),MCU的功耗將大大的降低。如果在進(jìn)入深度休眠模式前,關(guān)閉所有外設(shè),則進(jìn)入深度休眠模式后,功耗可降至20uA以下。

2022-05-31 14:39:35

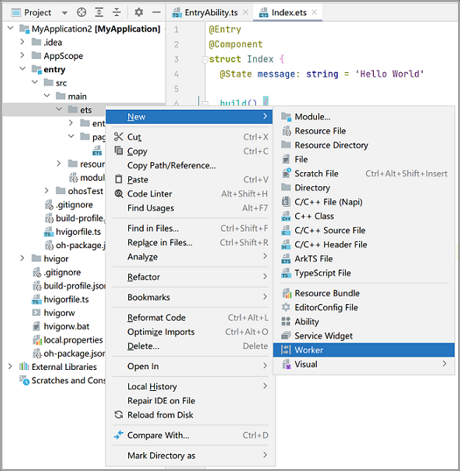

一、CPU密集型任務(wù)開發(fā)指導(dǎo)

CPU密集型任務(wù)是指需要占用系統(tǒng)資源處理大量計(jì)算能力的任務(wù),需要長(zhǎng)時(shí)間運(yùn)行,這段時(shí)間會(huì)阻塞線程其它事件的處理,不適宜放在主線程進(jìn)行。例如圖像處理、視頻編碼、數(shù)據(jù)分析等

2023-09-26 16:29:45

存儲(chǔ)較長(zhǎng)時(shí)間的擾動(dòng)信號(hào)。LCD模塊采用的是3.3 V單電源供電的320x240大屏幕點(diǎn)陣液晶ZXM320240E1,有足夠的空間將多路的情況同時(shí)顯示在屏幕上,而且由于系統(tǒng)選用FPGA的管腳電壓為

2020-08-31 18:54:17

; Xplorer和TCL腳本操作實(shí)例;動(dòng)手實(shí)例18. Smart Guide操作實(shí)例;演示實(shí)例第二天? 課程目標(biāo)通過(guò)本天課程的學(xué)習(xí),掌握DSP系統(tǒng)設(shè)計(jì)流程以及在FPGA

2009-07-21 09:20:11

TMS320C6748的使用,了解其新特性。2、學(xué)習(xí)利用dsp實(shí)現(xiàn)一些高級(jí)濾波算法。3、將dsp與fpga結(jié)合實(shí)現(xiàn)高速數(shù)據(jù)采集。4、分享5篇左右的開發(fā)板使用心得。

2015-10-09 15:10:00

信號(hào),控制系統(tǒng)開始結(jié)束采集。3.AD控制模塊:為AD芯片提供各種控制信號(hào),并接收AD轉(zhuǎn)換后的數(shù)據(jù)。4.異步FIFO模塊:實(shí)現(xiàn)數(shù)據(jù)緩存,將AD傳送的數(shù)據(jù)緩存。再通過(guò)FPGA的控制將數(shù)據(jù)高速傳給DSP

2015-11-06 10:01:48

引言DSP+FPGA廣泛地應(yīng)用于各種數(shù)字信息處理系統(tǒng)中。在某些特殊的應(yīng)用場(chǎng)合中,往往需要系統(tǒng)在高溫的環(huán)境下工作,而系統(tǒng)功耗又不明顯增加。雖然一般基于SRAM工藝的FPGA的顯現(xiàn)配置方法已經(jīng)多種多樣

2019-06-13 05:00:07

對(duì)數(shù)據(jù)采集與處理系統(tǒng)提出了新的更高的要求,即高速度、高精度和高實(shí)時(shí)性。對(duì)數(shù)據(jù)采集與處理系統(tǒng)的設(shè)計(jì),有以下3種方案可供選擇:(1)A/D+DSP方案在傳統(tǒng)的高速信號(hào)處理中,大多采用這種方案。將A/D、D

2019-07-05 06:41:27

`FPGA是一種可編程的硅芯片,DSP是數(shù)字信號(hào)處理,當(dāng)系統(tǒng)設(shè)計(jì)人員在項(xiàng)目的架構(gòu)設(shè)計(jì)階段就面臨到底采用FPGA還是DSP的重要問(wèn)題。本文將首先分別介紹FPGA和DSP的特點(diǎn),然后再?gòu)膬?nèi)部資源、編程

2016-12-23 16:56:04

計(jì)算密集型任務(wù),如矩陣運(yùn)算、圖像處理、機(jī)器學(xué)習(xí)等。與CPU相比,FPGA在這些任務(wù)上具有更高的性能和更低的延遲。 此外,FPGA在通信密集型任務(wù)中也具有顯著優(yōu)勢(shì)。由于FPGA上的收發(fā)器可以直接接上高速

2024-02-21 16:10:49

`密集型光波復(fù)用(DWDM)是能組合一組光波長(zhǎng)用一根光纖進(jìn)行傳送。這是一項(xiàng)用來(lái)在現(xiàn)有的光纖骨干網(wǎng)上提高帶寬的激光技術(shù)。更確切地說(shuō),該技術(shù)是在一根指定的光纖中,多路復(fù)用單個(gè)光纖載波的緊密光譜間距,以便

2018-03-30 14:33:02

。FPGA采用Altera 公司的40nm Stratix IV 系列FPGA。通過(guò)SRIO協(xié)議,DSP可與FPGA的進(jìn)行高速通信。由于集成了DSP和FPGA各自優(yōu)點(diǎn),HPS6678可在高速無(wú)線通信、多媒體系統(tǒng)、雷達(dá)及衛(wèi)星系統(tǒng)、醫(yī)療系統(tǒng)、高清圖像處理等多個(gè)領(lǐng)域中發(fā)揮重要的作用。

2019-09-24 08:29:12

描述對(duì)于目前使用 FPGA 或 ASIC 連接到高速數(shù)據(jù)轉(zhuǎn)換器、需要在縮短上市時(shí)間的同時(shí)提高性能并顯著降低成本、功耗和尺寸的現(xiàn)代雷達(dá)系統(tǒng)開發(fā)人員,此參考設(shè)計(jì)包含集成了 JESD204B 接口和數(shù)

2018-07-13 12:05:33

基于DSP和FPGA的高速串行通信系統(tǒng)設(shè)計(jì)

2015-03-16 15:47:04

為了實(shí)現(xiàn)—是彈武器瞄準(zhǔn)自動(dòng)化,本文設(shè)計(jì)了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統(tǒng),采用QUartuBn在AJtera的FPGA器件CYCLONEII上設(shè)計(jì)了CCD驅(qū)動(dòng)時(shí)序電路,采用

2014-11-07 14:54:07

集成化程度的提高,不僅可使系統(tǒng)的體積變小、重量減輕、功耗降低,更重要的是可使系統(tǒng)的可靠性大大地提高,因此電子系統(tǒng)日趨數(shù)字化、復(fù)雜化和大規(guī)模集成化。而由于可編程邏輯器件(如FPGA、CPLD)是一種

2019-07-12 08:32:59

基于FPGA+DSP的高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

2012-06-27 17:23:53

隨著現(xiàn)代電子信息技術(shù)的發(fā)展,人機(jī)交互、圖形圖像數(shù)據(jù)的輸出顯示在系統(tǒng)設(shè)計(jì)中越來(lái)越重要,一方面要求各種參數(shù)的輸入,另一方面要求將數(shù)據(jù)結(jié)構(gòu)顯示出來(lái)。文中設(shè)計(jì)的基于DSP和FPGA的系統(tǒng)結(jié)構(gòu),實(shí)現(xiàn)了人機(jī)交互

2019-07-03 08:08:33

非常廣闊。本文作者創(chuàng)新點(diǎn):將FPGA+DSP并行處理架構(gòu)應(yīng)用于光纖傳感信號(hào)處理系統(tǒng),提高系統(tǒng)的實(shí)時(shí)處理速度,并針對(duì)載波相位延遲造成的解調(diào)信號(hào)幅度衰減提出了解決方法。系統(tǒng)在光纖產(chǎn)業(yè)的工程化應(yīng)用具有良好的前景。

2021-07-05 11:23:33

使得高速模擬信號(hào)的數(shù)字處理得以可能。(個(gè)人理解OS:相對(duì)與DSP而言,FPGA在高速計(jì)算和可擴(kuò)展性方面具有更好的彈性)FPGA的彈性設(shè)計(jì)表現(xiàn)在使得每一個(gè)數(shù)字系統(tǒng)設(shè)計(jì)擁有最為高效的資源匹配。對(duì)一個(gè)有經(jīng)驗(yàn)的...

2021-07-23 08:06:59

設(shè)計(jì)根據(jù)系統(tǒng)功能要求,FPGA的任務(wù)主要分為4大部分。(1)控制數(shù)據(jù)在系統(tǒng)中的傳輸邏輯在設(shè)計(jì)時(shí),將圖2控制總線中的所有信號(hào)都連接到FPGA中,由FPGA來(lái)統(tǒng)一調(diào)度數(shù)據(jù)在DSP之間以及DSP與外部存儲(chǔ)器之間

2019-05-21 05:00:19

高速傳輸,但DSP價(jià)格過(guò)于昂貴。而利用FPGA和USB接口芯片結(jié)合的方案,具有功耗低、時(shí)鐘頻率高、速度快、效率高、組合形式靈活等特點(diǎn),是單片機(jī)和DSP所無(wú)法比擬的。

2019-09-05 07:22:57

硬件是用DSP來(lái)實(shí)現(xiàn)的;FPGA技術(shù)近兩年才達(dá)到可以實(shí)現(xiàn)大點(diǎn)數(shù)FFT的水平,并且體積、速度、靈活性等各種性能都優(yōu)于DSP,但開發(fā)難度大,研制費(fèi)用高。本文將討論基于FPGA的大點(diǎn)數(shù)超高速FFT算法。

2009-06-14 00:19:55

處理功能,使設(shè)計(jì)達(dá)到更低價(jià)位點(diǎn)。 Spartan-3器件用作協(xié)處理器或預(yù)/后處理器是非常理想的,它們將運(yùn)算密集型功能從可編程DSP上卸載下來(lái)以增強(qiáng)系統(tǒng)性能。

2019-06-27 06:12:26

如何將噪聲影響降至最低?如何防止緩沖器偏移?

2021-05-13 06:19:38

的邏輯處理和控制算法,能實(shí)現(xiàn)多軸高速高精度的伺服控制。利用DSP與FPGA設(shè)計(jì)運(yùn)動(dòng)控制器,其中DSP用于運(yùn)動(dòng)軌跡規(guī)劃、速度控制及位置控制等功能;FPGA完成運(yùn)動(dòng)控制器的精插補(bǔ)功能,用于精確計(jì)算步進(jìn)電機(jī)或伺服驅(qū)動(dòng)元件的控制脈沖,同時(shí)接收并處理脈沖型位置反饋信號(hào)。那么,我們具體該怎么做呢?

2019-08-06 06:27:00

高速連續(xù)數(shù)據(jù)采集系統(tǒng)的背景及功能是什么?如何利用FPGA實(shí)現(xiàn)高速連續(xù)數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)?FPGA在高速連續(xù)數(shù)據(jù)采集系統(tǒng)中的應(yīng)用有哪些?

2021-04-08 06:19:37

大型的幾乎所有數(shù)字電路系統(tǒng),dsp主要完成復(fù)雜的數(shù)字信號(hào)處理,如fft,通常一個(gè)復(fù)雜系統(tǒng)可以由單片機(jī)、arm、fpga、dsp中的一種或幾種構(gòu)成,各有優(yōu)勢(shì)和不足。dsp通常用于運(yùn)算密集型,fpga用于

2018-10-10 18:02:03

使用XIP平臺(tái),而新的密集高速處理平臺(tái)正在向新的代碼映射存儲(chǔ)器架構(gòu)發(fā)展。XIP的優(yōu)勢(shì)包括經(jīng)典架構(gòu)(軟件不用變化)、較低的功耗和較短的啟動(dòng)時(shí)間。而代碼映射架構(gòu)可以提供更好的成本定位和更高的速度(新特點(diǎn)

2009-10-08 15:53:49

這樣的電路甚至可以利用電源濾波來(lái)進(jìn)一步減小電源噪聲的影響。 怎樣將單元模塊中的相位噪聲和抖動(dòng)降至最低 在設(shè)計(jì)單元模塊時(shí)可以采用以下技術(shù)來(lái)減小抖動(dòng):1.利用尾電流--時(shí)序電路中使

2009-10-13 17:23:19

。隨著前沿技術(shù)的快速發(fā)展和自研技術(shù)的深入,往往還會(huì)產(chǎn)生相當(dāng)一部分自定義的運(yùn)算模塊。此類模塊通常也是計(jì)算密集型的操作,無(wú)法使用CPU高效實(shí)現(xiàn),因此還需要通用的計(jì)算密集型處理單元(比如DSP、GPU)來(lái)實(shí)現(xiàn)

2022-08-11 15:55:37

電磁感應(yīng)加熱的原理是什么?有什么方法可以將電磁感應(yīng)加熱應(yīng)用的IGBT功率損耗降至最低嗎?

2021-05-10 06:41:13

人工智能學(xué)習(xí)1. 人工智能應(yīng)用場(chǎng)景網(wǎng)絡(luò)安全、電子商務(wù)、計(jì)算模擬、社交網(wǎng)絡(luò) … …2. 人工智能必備三要素?cái)?shù)據(jù),算法,計(jì)算力計(jì)算力之CPU、GPU對(duì)比:CPU主要適合I\O密集型的任務(wù)GPU主要適合

2021-09-07 06:14:03

高速DSP系統(tǒng)PCB板的特點(diǎn)有哪些?設(shè)計(jì)高速DSP系統(tǒng)中的PCB板應(yīng)注意哪些問(wèn)題?

2021-04-21 07:21:09

非常復(fù)雜,在許多情況下單個(gè) DSP 實(shí)現(xiàn)方案根本沒(méi)有足夠的處理能力。同時(shí),系統(tǒng)架構(gòu)也不能滿足多芯片系統(tǒng)帶來(lái)的成本、復(fù)雜性和功耗要求。FPGA 已成為需要高性能 DSP 功能的系統(tǒng)的理想選擇。事實(shí)上

2018-08-15 09:46:21

工藝。對(duì)于任何電子系統(tǒng),降低功耗當(dāng)然也就意味著降低了運(yùn)營(yíng)成本以及總體擁有成本。Cyclone V FPGA中使用的成本最優(yōu)28LP工藝定制滿足了低成本和低功耗應(yīng)用需求。通過(guò)采用各種技術(shù),包括使用比

2015-02-09 15:02:06

CPU密集型任務(wù)是指需要占用系統(tǒng)資源處理大量計(jì)算能力的任務(wù),需要長(zhǎng)時(shí)間運(yùn)行,這段時(shí)間會(huì)阻塞線程其它事件的處理,不適宜放在主線程進(jìn)行。例如圖像處理、視頻編碼、數(shù)據(jù)分析等。

基于多線程并發(fā)機(jī)制處理CPU

2024-03-19 14:14:20

能力,而在于I/O操作的速度和效率。這種任務(wù)通常需要頻繁地進(jìn)行磁盤讀寫、網(wǎng)絡(luò)通信等操作。此處以頻繁讀寫系統(tǒng)文件來(lái)模擬I/O密集型并發(fā)任務(wù)的處理。

定義并發(fā)函數(shù),內(nèi)部密集調(diào)用I/O能力。

import

2024-03-21 14:57:56

軟件密集型裝備故障的靜態(tài)檢測(cè):軟件密集型裝備是指軟件和硬件緊密結(jié)合的裝備,軟件密集型裝備中的故障多由軟件與硬件相互作用引發(fā)。本文對(duì)程序流程違反硬件工作時(shí)序引起

2009-06-21 22:35:28 16

16 復(fù)用器的密集型光波復(fù)用

2010-01-07 14:26:09 873

873 TI業(yè)內(nèi)最低功耗16位DSP平臺(tái)再添新成員

日前,德州儀器 (TI) 宣布旗下業(yè)界最低功耗 16 位數(shù)字信號(hào)處理器 (DSP) 平臺(tái) C5000 新增兩款器件:TMS320C5514 與 TMS320C5515。此外,為幫

2010-01-20 08:40:23 982

982 Cyclone V FPGA簡(jiǎn)介 Altera公司的28nm Cyclone V FPGA器件是目前市場(chǎng)上功耗最低、成本最低的28nm FPGA。該系列通過(guò)集成,前所未有的同時(shí)實(shí)現(xiàn)了高性能、低系統(tǒng)成本和低功耗,非常適合工業(yè)、無(wú)線

2012-09-04 13:44:54 2117

2117 Cyclone V FPGA功耗優(yōu)勢(shì):采用低功耗28nm FPGA活的最低系統(tǒng)功耗(英文資料)

2012-09-05 16:04:11 40

40 基于雙DSP和雙FPGA的高速圖像處理系統(tǒng)設(shè)計(jì)_吳雷

2017-03-16 09:28:51 2

2 計(jì)算高度密集型應(yīng)用在異構(gòu)多核DSP上的運(yùn)行方法研究

2017-10-19 11:00:44 5

5 基于FPGA和DSP的高速圖像處理系統(tǒng)

2017-10-19 13:43:31 19

19 基于FPGA的高速DSP與液晶模塊接口的實(shí)現(xiàn)

2017-10-19 13:46:23 3

3 隨著微電子技術(shù)的高速發(fā)展,新器件的應(yīng)用導(dǎo)致現(xiàn)代 EDA 設(shè)計(jì)的電路布局密度大,而且信號(hào)的頻率也很高,隨著高速器件的使用,高速 DSP(數(shù)字信號(hào)處理)系統(tǒng)設(shè)計(jì)會(huì)越來(lái)越多,處理高速 DSP 應(yīng)用系統(tǒng)

2017-11-07 11:00:43 0

0 隨著高性能信號(hào)處理系統(tǒng)對(duì)運(yùn)算速度、通信速率等要求的不斷提高,單獨(dú)的處理器(如FPGA或DSP)無(wú)法滿足高速實(shí)時(shí)信號(hào)處理的需求。TI公司的多核DSP處理性能強(qiáng)大,但是并行性不強(qiáng),難以適應(yīng)計(jì)算異常密集

2017-11-17 03:11:01 28802

28802

針對(duì)噴油器霧化粒徑測(cè)量系統(tǒng)實(shí)時(shí)數(shù)據(jù)處理的特點(diǎn),將FPGA技術(shù)與DSP技術(shù)相結(jié)合,研究一種基于FPGA和DSP的電控噴油器粒徑檢測(cè)系統(tǒng);為滿足動(dòng)態(tài)測(cè)量的要求,設(shè)計(jì)了應(yīng)用高性能的多路開關(guān)和超低輸入偏置電流運(yùn)放的多通道微電流高速采集板;詳細(xì)介紹了檢測(cè)系統(tǒng)中基于FPGA和DSP的軟硬件設(shè)計(jì)和工作原理。

2017-12-06 17:03:04 1728

1728

針對(duì)急劇上升的大規(guī)模數(shù)據(jù),傳統(tǒng)的數(shù)據(jù)密集型計(jì)算已經(jīng)無(wú)法再在此種場(chǎng)景下適用.對(duì)此,大量的學(xué)者們對(duì)算法進(jìn)行不斷的改進(jìn),并提出利用新型的處理器來(lái)進(jìn)行復(fù)雜的數(shù)據(jù)密集型計(jì)算.在眾多的新型處理器中,FPGA

2018-01-10 14:08:24 0

0 賽靈思公司為成本敏感型應(yīng)用推出靈活的 I/O 密集型器件——Spartan-7 FPGA系列。該新型系列器件可滿足汽車、消費(fèi)類電子、工業(yè)物聯(lián)網(wǎng)、數(shù)據(jù)中心、有線/無(wú)線通信和便攜式醫(yī)療解決方案等多種

2018-08-20 10:48:00 1464

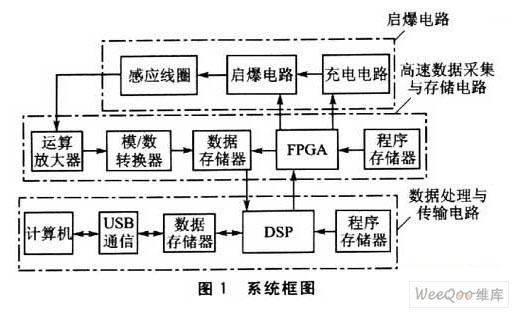

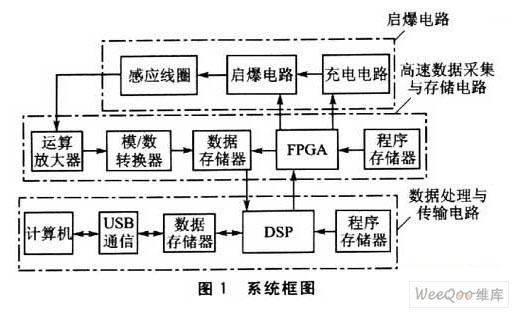

1464 整個(gè)系統(tǒng)的組成如圖1所示。當(dāng)啟爆電路在DSP和FPGA的控制下啟爆時(shí),感應(yīng)線圈取出啟爆電流,首先是高速數(shù)據(jù)采集與存儲(chǔ)電路,以FPGA為核心,對(duì)數(shù)據(jù)進(jìn)行高速采集與存儲(chǔ)。數(shù)據(jù)存儲(chǔ)完畢,FPGA發(fā)信號(hào)告知DSP采集完畢,開始對(duì)采集的數(shù)據(jù)進(jìn)行相關(guān)的處理。

2018-10-07 12:03:03 2981

2981

型到大型的幾乎所有數(shù)字電路系統(tǒng),dsp主要完成復(fù)雜的數(shù)字信號(hào)處理,如fft,通常一個(gè)復(fù)雜系統(tǒng)可以由單片機(jī)、arm、fpga、dsp中的一種或幾種構(gòu)成,各有優(yōu)勢(shì)和不足。dsp通常用于運(yùn)算密集型,fpga

2018-09-11 11:49:53 303

303 對(duì)于高速的DSP密集型系統(tǒng)設(shè)計(jì),降低功率變得越來(lái)越重要。例如,在通信系統(tǒng)中,通信必須以周期猝發(fā)方式來(lái)實(shí)施,以避免放大器和系統(tǒng)其余部分電路持續(xù)消耗功率。在傳感器網(wǎng)絡(luò)中的要求是定期關(guān)斷工作的傳感器(比如

2018-11-02 16:37:11 707

707 介紹了1種基于FPGA和DSP的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn),其FPGA采用Altera公司ACEX 1K系列的EPIK50Tcl443器件,DSP芯片采用TI公司TMs320系列

2018-11-07 17:18:24 18

18 軟FMCOMMS1-EBZ高速模擬模塊設(shè)計(jì)用于展示最新一代的高速數(shù)據(jù)轉(zhuǎn)換器。FMCOMMS1-EBZ為眾多計(jì)算密集型FPGA無(wú)線電應(yīng)用提供模擬前端。

2019-07-26 06:21:00 1904

1904 型到大型的幾乎所有數(shù)字電路系統(tǒng),dsp主要完成復(fù)雜的數(shù)字信號(hào)處理,如fft,通常一個(gè)復(fù)雜系統(tǒng)可以由單片機(jī)、arm、fpga、dsp中的一種或幾種構(gòu)成,各有優(yōu)勢(shì)和不足。 dsp通常用于運(yùn)算密集型,fpga用于控制密集型,許多人都用dsp高算法,用fpga作外圍控制

2020-10-25 09:50:06 3085

3085 德州儀器 (TI) 推出的業(yè)界最低功耗 6 核 DSP,該款 TMS320C6472 器件旨在滿足要求極低功耗的處理密集型應(yīng)用的需求。

2020-12-02 12:59:00 1337

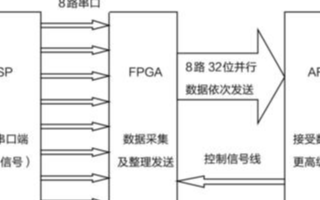

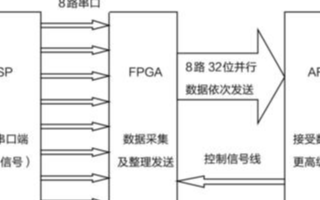

1337 隨著集成電路技術(shù)的發(fā)展,FPGA和DSP以及ARM以其體積小、速度快、功耗低、設(shè)計(jì)靈活、利于系統(tǒng)集成、擴(kuò)展升級(jí)等優(yōu)點(diǎn),被廣泛地應(yīng)用于高速數(shù)字信號(hào)傳輸及數(shù)據(jù)處理,以DSP+FPGA+ARM的架構(gòu)組成滿足實(shí)時(shí)性要求的高速數(shù)字處理系統(tǒng)已成為一種趨勢(shì),本文主要研究FPGA在高速多路數(shù)據(jù)傳輸中的應(yīng)用。

2021-04-24 09:04:49 4553

4553

布局電源板以將EMI降至最低:第2部分

2021-04-24 15:23:01 4

4 布局電源板以將EMI降至最低:第3部分

2021-04-28 14:04:37 7

7 布局電源板以將EMI降至最低:第1部分

2021-04-28 15:54:26 8

8 AN-601:將IMEMS?加速度計(jì)的功耗降至最低

2021-05-10 08:24:41 3

3 FPGA可用于處理多元計(jì)算密集型任務(wù),依托流水線并行結(jié)構(gòu)體系,FPGA相對(duì)GPU、CPU在計(jì)算結(jié)果返回時(shí)延方面具備技術(shù)優(yōu)勢(shì)。

2022-11-10 09:49:28 674

674 (DataIntensiveComputing)就是大數(shù)據(jù)的核心支撐技術(shù)。什么是數(shù)據(jù)密集型計(jì)算先來(lái)了解一下基本概念:數(shù)據(jù)密集型計(jì)算指能推動(dòng)前沿技術(shù)發(fā)展的對(duì)海量和高速變化的數(shù)據(jù)的獲取、管理、分析和理解

2021-10-29 18:08:04 495

495

(DataIntensiveComputing)就是大數(shù)據(jù)的核心支撐技術(shù)。什么是數(shù)據(jù)密集型計(jì)算先來(lái)了解一下基本概念:數(shù)據(jù)密集型計(jì)算指能推動(dòng)前沿技術(shù)發(fā)展的對(duì)海量和高速變化的數(shù)據(jù)的獲取、管理、分析和理解

2021-11-01 15:49:16 387

387

電子發(fā)燒友網(wǎng)站提供《云優(yōu)化性能:使用基于閃存的存儲(chǔ)的I/O密集型工作負(fù)載.pdf》資料免費(fèi)下載

2023-08-28 10:04:34 0

0 在這篇文章中,我想探討和比較用于邊緣密集型星載處理的微處理器和FPGA。一些應(yīng)用需要從不同帶寬的多個(gè)傳感

器(如RF、LIDAR、成像和GNSS)獲取大量數(shù)據(jù),同時(shí)需要實(shí)時(shí)做出關(guān)鍵決策,如用

2023-09-14 14:34:38 1

1

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論