在FPGA 上設計一個高性能、靈活的、面積小的通信體系結構是一項巨大的挑戰。大多數基于FPGA 的片上網絡都是運行在一個單一時鐘下。隨著FPGA 技術的發展,Xilinx 公司推出了Virtex-4 平臺

2011-10-21 16:13:51 1270

1270

致力于提供功率、安全、可靠與高性能半導體技術產品的領先供應商美高森美公司(Microsemi Corporation,紐約納斯達克交易所代號:MSCC)宣布推出雙通道ZL30240和單通道ZL30241時鐘發生器產品,用于包括通信設備、企業路由器和交換、網絡存儲設備和服務器等多種應用。

2013-04-23 13:42:44 1208

1208 針對不同類型的器件,Xilinx公司提供的全局時鐘網絡在數量、性能等方面略有區別,下面以Virtex-4系列芯片為例,簡單介紹FPGA全局時鐘網絡結構。

2013-11-28 18:49:00 12149

12149

的高性能時鐘發生器系列產品,特別針對10/25/100G應用提供業界最高集成度的時鐘解決方案。新型Si5332時鐘系列產品利用Silicon Labs經過驗證的MultiSynth小數時鐘合成技術,提供

2017-09-26 12:24:08 9289

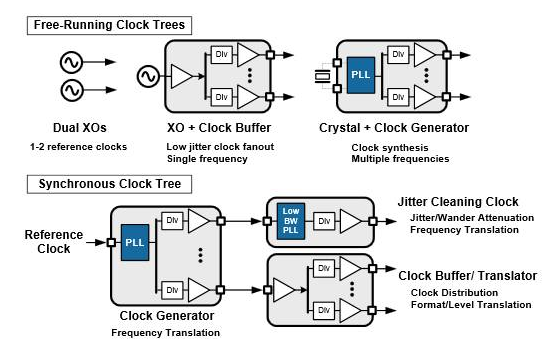

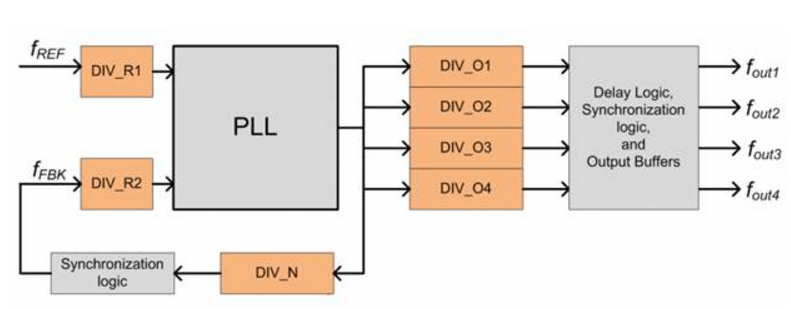

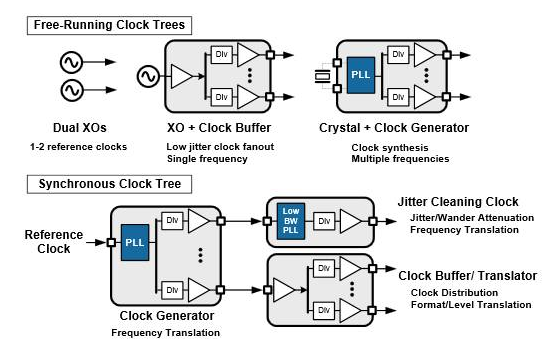

9289 在高性能應用中,例如通信、無線基礎設施、服務器、廣播視頻以及測試和測量裝置,當系統集成更多功能并需要提高性能水平時,硬件設計就變得日益復雜,為系統提供參考時序的板級時鐘樹也走向這種趨勢。在進行時鐘

2017-10-31 09:45:13 5550

5550

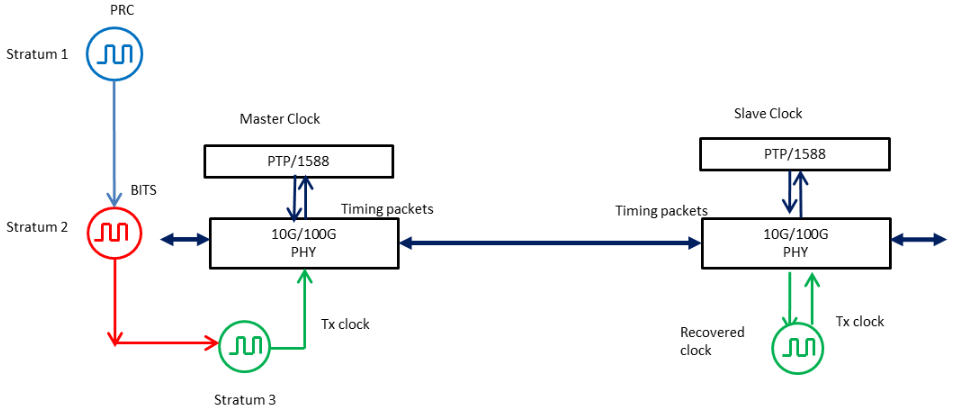

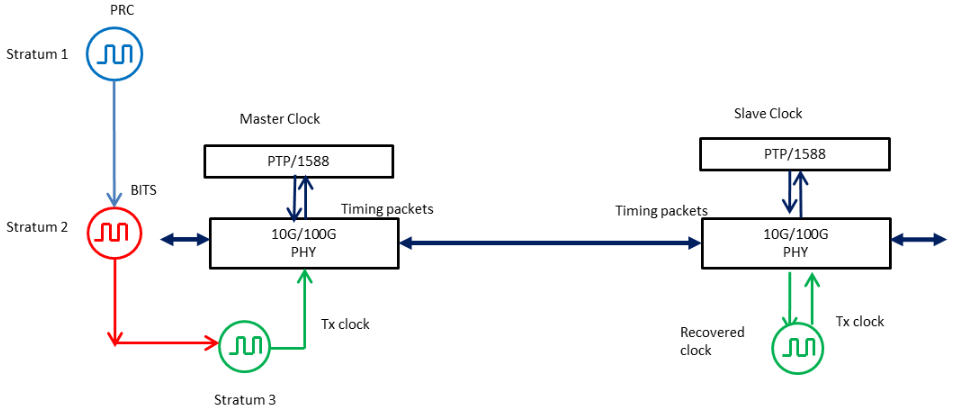

同步以太網是一種采用以太網鏈路碼流恢復時鐘的技術, 簡稱SyncE。同步以太網通過從串行數據碼流中恢復出發送端的時鐘,從而實現網絡時鐘同步。但SyncE不能提供時間同步。

2020-05-12 09:24:02 1945

1945

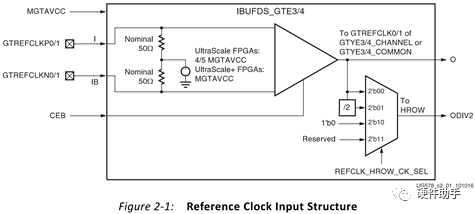

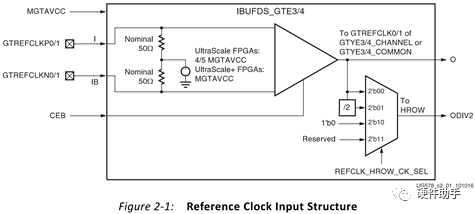

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。 參考時鐘的模式 參考時鐘可以配置為輸入模式也可以是輸出模式,但是在運行期間不能切換。作為

2020-11-14 11:39:15 13866

13866

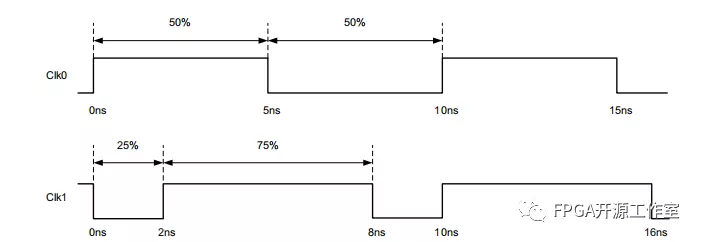

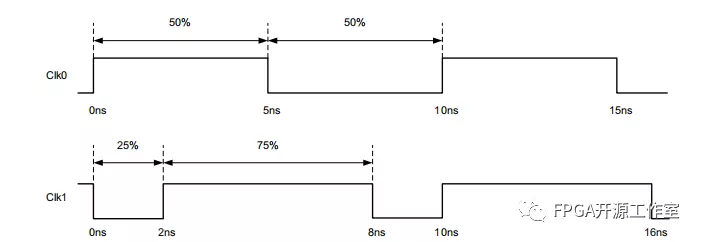

1. 時鐘介紹 在數字設計中,時鐘代表從寄存器(register)到寄存器可靠傳輸數據的時間基準。Xilinx Vivado集成設計環境(IDE)時序引擎使用ClocK特征計算時序路徑要求,并通過

2020-11-29 10:51:45 5359

5359

7系列FPGA擁有豐富的時鐘資源。各種緩沖器類型、時鐘輸入管腳和時鐘連接,可以滿足許多不同的應用需求。選擇合適的時鐘資源可以改善布線、性能和一般FPGA資源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 7系列FPGA時鐘資源通過專用的全局和區域I/O和時鐘資源管理符合復雜和簡單的時鐘要求。時鐘管理塊(CMT)提供時鐘頻率合成、減少偏移和抖動過濾等功能。非時鐘資源,如本地布線,不推薦用于時鐘功能。

2022-07-28 09:07:34 1276

1276 。Xilinx FPGA7系列分為全局時鐘(Global clock)和局部時鐘(Regional clock)資源。目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期

2023-07-24 11:07:04 655

655

通過上一篇文章“時鐘管理技術”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結合,Xilinx 7系列FPGA可實現高性能和可靠的時鐘分配

2023-08-31 10:44:31 1032

1032

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

2023-09-15 09:14:26 1956

1956

新推出的精密時序主時鐘,搭配網關時鐘和最快速的高性能邊界時鐘,增強5G移動網絡的相位保護。

2020-04-22 14:32:03 711

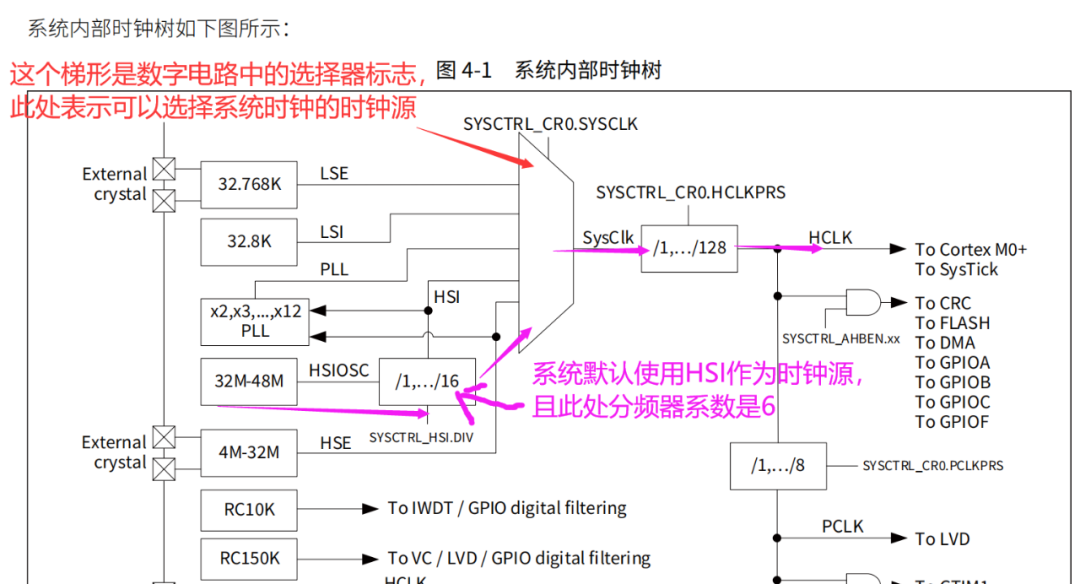

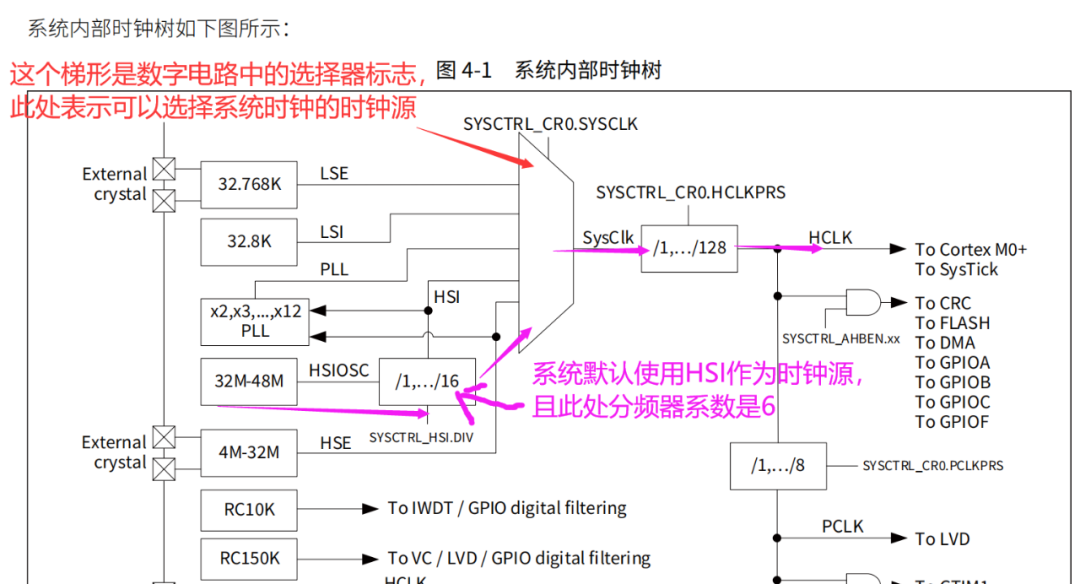

711 學習STM32的同學知道,STM32有好多時鐘,如32.768Khz,8Mhz,被時鐘樹搞迷糊了,下面一一解析。HSE:高速外部時鐘信號(4--16Mhz常用的為8Mhz)HSI:高速內部時鐘信號

2017-04-27 16:34:26

嗨,我想了解7系列收發器的Kintex xc7k325tffg900-2 FPGA。https://www.xilinx.com/support/documentation/user_guides

2020-05-11 08:09:08

引言: 我們在進行FPGA原理圖和PCB設計時,都會涉及到FPGA芯片管腳定義和封裝相關信息,本文就Xilinx 7系列FPGA給出相關參考,給FPGA硬件開發人員提供使用。通過本文,可以了解到

2021-05-28 09:23:25

系列有哪些主要特性/優勢? Kintex UltraScale系列產品的主要優勢來自于UltraScale在架構上的重要創新,包括: o 類似ASIC時鐘功能,實現可擴展性、高性能和低動態功耗

2013-12-17 11:18:00

時鐘設備設計使用 I2C 可編程小數鎖相環 (PLL),可滿足高性能時序需求,這樣可以產生零 PPM(百萬分之一)合成誤差的頻率。高性能時鐘 IC 具有多個時鐘輸出,用于驅動打印機、掃描儀和路由器等

2019-08-12 06:50:43

在本文中,我們將討論抖動傳遞及其性能,以及相位噪聲測量技術的局限性。 時鐘抖動和邊沿速率 圖1顯示了由一個通用公式表述的三種波形。該公式包括相位噪聲項“φ(t)”和幅度噪聲項“λ(t)。對評估的三個

2022-11-23 07:59:49

的主要缺點是,您放棄了實現dc、地震、音頻和更高帶寬應 用的絕對最高可能性能所需的自定義和優化。在急于重用和完 成設計的過程中,往往會犧牲精確性能。其容易忽略和忽視 的一個主要方面是時鐘。在本文中,我們將討論時鐘的重要性, 并為正確設計高性能轉換器提供指導。

2021-01-27 07:27:36

。一般的頻譜分析儀的噪底高于高性能時鐘緩沖的噪底。正確測量時鐘緩沖的相噪和附加抖動需要專業的信號分析儀。圖5 國產廠商無錫有容微電子時鐘緩沖GM50101的相位噪聲測試圖圖5是國產廠商無錫有容微電子高性能

2022-06-08 12:54:33

時鐘設備設計使用 I2C 可編程小數鎖相環 (PLL),可滿足高性能時序需求,這樣可以產生零 PPM(百萬分之一)合成誤差的頻率。高性能時鐘 IC 具有多個時鐘輸出,用于驅動打印機、掃描儀和路由器等

2018-08-27 09:46:58

對于廣大初次接觸STM32的讀者朋友(甚至是初次接觸ARM器件的讀者朋友)來說,在熟悉了開發環境的使用之后,往往“栽倒”在同一個問題上。這問題有個關鍵字叫:時鐘樹。眾所周知,微控制器(處理器)的運行

2011-10-21 14:36:05

Aurix系列單片機時鐘系統有哪些特點

2024-02-04 06:48:15

,FPGA上的全局時鐘管腳用完了就出現不夠用的情況。FPGA全局時鐘約束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

LPC1768時鐘解析:

2016-12-29 17:41:01

STM32系統架構基礎名詞有哪些呢?STM32時鐘系統有哪些性能呢?

2021-12-14 07:49:07

Xilinx Virtex 4 和高性能時鐘合成器 LMX2531 來滿足 9 位 ENOB 高速數字轉換器的系統要求。 特性2 個 GSPS 模數轉換通道大于 9 位 ENOB 超寬輸入頻率范圍面向測試和測量系統的低成本雙通道高速數字轉換器原型

2022-09-20 07:01:22

ZN-81CCG高性能高級維修電工技能培訓考核裝置有什么特點?

2021-10-20 06:15:11

單元每個7系列的FPGA都有最高24個時鐘管理單元(CMTs),每個時鐘管理單元都包含一個混合時鐘管理(MMCM)部分和一個鎖相環(PLL)。混合模式時鐘管理器和鎖相環有很多相同的特點,例如都能實現

2016-11-01 15:52:18

我有一個關于多個Xilinx芯片時鐘的問題。我正在審查另一位數字工程師的設計。有多個機箱,每個機箱都有自己的Xilinx芯片(XC9500)。一些Xilinx芯片正在與其他芯片進行交互。但是,每個

2019-01-09 10:41:26

基于V7的高性能PCIe信號處理板是什么?基于V7的高性能PCIe信號處理板有哪些主要功能?基于V7的高性能PCIe信號處理板有哪些應用?

2021-06-25 06:21:15

老化效應抖動ClockEdge 確實是 STA 的補充, ClockEdge 將成為您的時鐘簽核工具。所有設備老化模型均由您的代工廠提供。作為 ClockEdge 性能的一個例子,它運行在一個有

2022-11-04 11:08:00

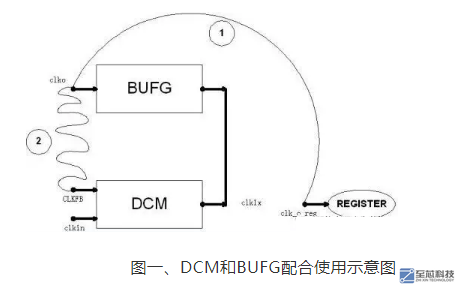

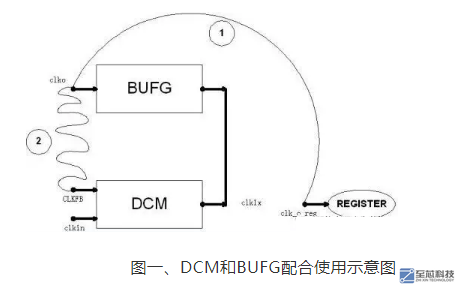

個數字時鐘管理模塊(DCM)。與全局時鐘資源相關的原語常用的與全局時鐘資源相關的Xilinx器件原語包括:IBUFG、IBUFGDS、BUFG、BUFGP、BUFGCE、BUFGMUX、BUFGDLL和DCM等。

2019-10-22 06:01:34

您好請教一下 10MHz的參考時鐘clkref進入 要使一個板子上的FPGA(Xilinx zynq 7020)和ADC(AD9211)同步,FPGA工作和ADC的工作頻率都是256MHz現在方案有

2018-08-02 09:02:02

在FPGA 上設計一個高性能、靈活的、面積小的通信體系結構是一項巨大的挑戰。大多數基于FPGA 的片上網絡都是運行在一個單一時鐘下。隨著FPGA 技術的發展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

本文針對全方位的信號路徑系統中的高速全差分運放及高頻寬14位模擬/數字轉換器的隨機及固定時鐘抖動,具體分析、研究了超低噪聲兼時鐘抖動濾除技術。研究選用雙級聯PLLatinum架構,配置高性能壓控振蕩器(VCXO),很好地實現了降噪和時鐘抖動濾除的作用。

2019-07-05 07:47:46

請大神指教,fpga提供的pll有最低時鐘輸出限制,請問有pll之外的什么方式輸出高性能時鐘?

2013-08-26 10:53:39

嗨,我在級聯模式下使用Xilinx DCM(數字時鐘管理器),使用6.144 MHz時鐘生成48 kHz時鐘。但是,由于我的設計相當大(在區域內),這種配置無法滿足時序約束并對整個設計產生影響。因此

2019-03-25 14:09:18

描述適用于 GSPS 數據轉換器的低成本、高性能時鐘解決方案。此參考設計討論如何使用低噪聲頻率合成器 TRF3765 為 4 GSPS 模數轉換器 (ADC12J4000) 生成采樣時鐘。實驗展示了

2018-08-16 06:56:42

X12XX系列實時時鐘的特點及應用:

2009-05-22 13:25:24 18

18 系統時鐘源的比較選擇及高性能PLL的發展趨勢安森美半導體公司 供稿在所有電子系統中,時鐘相當于心臟,時鐘的性能和穩定性直接決定著整個系統的性能。典型的系統時序

2009-12-20 09:28:06 31

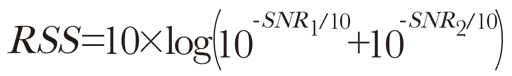

31 無線基礎設施、寬帶和儀器儀表應用通常需要高性能的時鐘電路,它們主要需要時鐘的器件是高速數據轉換器。這些系統的時鐘電路所需的幾個關鍵性能指標包括低相位噪聲和抖

2009-07-06 18:37:55 449

449

安森美時鐘管理產品系列增加新的時鐘和數據驅動IC

應用于綠色電子產品的首要高性能、高能效硅方案供應商安森美半導體(宣布擴充公司的時鐘驅動器系列,推出NB7L

2010-02-01 13:42:09 866

866 MAX3679A高性能四路輸出時鐘發生器(Maxim)

Maxim推出用于以太網設備的高性能、四路輸出時鐘發生器MAX3679A。器件采用低噪聲

2010-04-14 16:51:49 778

778 討論了物理設計中時鐘網絡的設計技術,并以現有的CPU時鐘網絡的為例,介紹了高性能CPU的時鐘網絡設計技術。

2011-12-27 15:28:56 46

46 高性能的時鐘同步系統是任何通信傳輸領域必不可少的,并且在很大程度上決定了整個傳輸系統的性能,可稱之為傳輸系統的心臟 時鐘同步系統是基于鎖相環路的同步原理,跟蹤一個高

2011-12-28 16:39:39 41

41 ADI最近宣布收購Multigig,Inc.,這家小型私營企業位于加利福尼亞州圣何塞,專注于高度創新的高性能時鐘技術。

2012-04-18 09:19:40 565

565 DLL在_FPGA時鐘設計中的應用,主要說明DLL的原理,在Xilinx FPGA中是怎么實現的。

2015-10-28 14:25:42 1

1 當Xilinx 7Series FPGA中,存在3種主要的時鐘網絡:BUFG,BUFR,BUFIO以及他們所衍生出的各種變種。那么他們有什么主要特點和區別呢? BUFIO是IO時鐘網絡,顧名思義

2017-02-08 05:31:40 2048

2048

談到數字邏輯,談到FPGA設計,每位工程師都離不開時鐘。這里我們簡單介紹一下xilinx 7 系列中的時鐘資源。時鐘設計的好壞,直接影響到布局布線時間、timing的收斂情況,FPGA的時鐘

2017-02-08 05:33:31 561

561

1. Xilinx 時鐘資源 xilinx 時鐘資源分為兩種:全局時鐘和第二全局時鐘。 1. 全局時鐘資源 Xilinx 全局時鐘采用全銅工藝實現,并設計了專用時鐘緩沖與驅動結構,可以到達芯片內部

2017-02-09 08:43:41 1315

1315 我們知道,SERDES對參考時鐘有嚴格的相位噪聲性能要求。通常,SERDES供應商會根據其SERDES采用的PLL以及CDR架構特點,以及性能數據,提出對參考時鐘的相位噪聲的具體要求。

2017-02-10 18:40:10 5965

5965

PLL),再到Virtex-6基于PLL的新型混合模式時鐘管理器MMCM(Mixed-Mode Clock Manager),實現了最低的抖動和抖動濾波,為高性能的FPGA設計提供更高性能的時鐘管理功能。

2017-02-11 09:14:01 1030

1030

現議價。不幸的是,相對較少信息已出現在晶體電路和工程師們常常把水晶電路視為一種黑色藝術,最好留給幾個熟練的從業者(見盒子),關于石英水晶。 事實上,最高性能的晶體時鐘電路要求各種復雜的考慮和微妙實現技術。然而,

2017-05-05 11:38:25 14

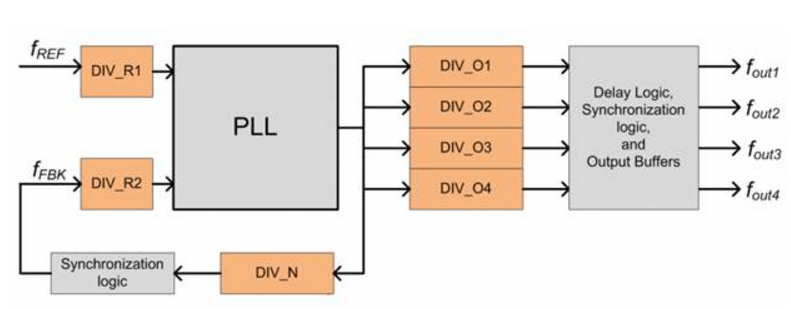

14 時鐘設備設計使用I2C可編程小數鎖相環(PLL),可滿足高性能時序需求,這樣可以產生零PPM(百萬分之一)合成誤差的頻率。高性能時鐘IC具有多個時鐘輸出,用于驅動打印機、掃描儀和路由器等應用系統的子系統,例如處理器、FPGA、數據轉換器等。

2017-08-30 11:04:04 4285

4285

高性能CPU的時鐘網絡設計

2017-10-30 15:28:58 23

23 樹結構 針對不同類型的器件,Xilinx公司提供的全局時鐘網絡在數量、性能等方面略有區別,下面以Virtex-4系列芯片為例,簡單介紹FPGA全局時鐘網絡結構。

2017-11-22 07:09:36 8891

8891

作為一種高性能、低成本的線卡時鐘解決方案,LMK04800 可以實現傳統的 SDH/SONET 系統時鐘和分組交換網絡中的同步以太網時鐘頻率的靈活轉換,同時提供 150fs 級別的低抖動性能,滿足

2017-11-28 16:57:56 5

5 STM32各類系列時鐘

2018-01-25 16:40:35 3

3 分享到務來管理時鐘節拍,而且采用哈希散列表機制來進一步減少時鐘節拍處理過程所花費的時間。本文討論μC/OS—II在時鐘節拍管理方面的不足,并介紹μC/OS—III中的高效時鐘節拍 管理機制 。

2018-04-09 11:29:00 1270

1270

目前對時鐘頻率還能代表處理器性能的話題在網上議論紛紛,情況有點復雜,自從英特爾在2008年推出睿頻加速技術能動態、自動地對處理器超頻后,這一技術就越來越普及了,在市場上銷售的處理器都能根據能耗

2018-04-28 16:42:56 7158

7158 有些FPGA學習者,看Xilinx的Datasheet會注意到Xilinx的FPGA沒有PLL,其實DCM就是時鐘管理單元。 1、DCM概述 DCM內部是DLL(Delay Lock Loop結構

2018-05-25 15:43:53 7884

7884

ADI研討會:高性能時鐘: 解密抖動

2019-08-20 06:05:00 1656

1656 時鐘信號是任何數字電路設計的基礎,而時鐘源是雷達、通信、測試儀器等電子系統實現高性能指標的關鍵,很多電子設備和系統功能的實現都直接依賴于高性能的時鐘源。文中選擇時鐘合成器MPC92433+FPGA

2019-10-03 11:02:00 981

981

美國馬薩諸塞州諾伍德市 - 全球領先的信號處理應用高性能半導體公司ADI公司今天推出了一系列時鐘IC,可滿足當今高性能電子應用中最嚴格的信號處理要求,如作為無線基礎設施收發器,儀器儀表和寬帶基礎設施

2019-09-15 16:52:00 3289

3289

時鐘設備設計使用I2C可編程小數鎖相環(PLL),可滿足高性能時序需求,這樣可以產生零PPM(百萬分之一)合成誤差的頻率。高性能時鐘IC具有多個時鐘輸出,用于驅動打印機、掃描儀和路由器等應用系統

2020-11-03 10:40:00 0

0 時鐘篇 選用全局時鐘緩沖區(BUFG)作為時鐘輸入信號,BUFG是最穩定的時鐘輸入源,可以避免誤差。 只用一個時鐘沿來寄存數據,使用時鐘的兩個沿是不可靠的,如果時鐘沿“漂移”,就會導致時序錯誤

2020-12-11 10:26:44 1482

1482 Xilinx7系列FPGA包括四個FPGA系列,它們都是為最低功耗而設計的,以使一個通用設計能夠跨系列擴展以獲得最佳的功率、性能和成本。斯巴達-7系列是7系列產品中密度最低、成本最低的入門級產品

2020-12-10 14:20:00 18

18 本章介紹了高云半導體FPGA 產品的時鐘資源,包括專用的時鐘輸入、緩沖區和布線資源。時鐘的基礎設施提供了一系列低電容、低偏移互連線,非常適合承載高頻信號,最大限度地減少時鐘偏差和提高性能,可應用于所有的時鐘信號。

2020-12-10 14:20:13 9

9 全局時鐘資源是一種專用互連網絡,它可以降低時鐘歪斜、占空比失真和功耗,提高抖動容限。Xilinx的全局時鐘資源設計了專用時鐘緩沖與驅動結構,從而使全局時鐘到達CLB、IOB和BRAM的延時最小。

2020-12-29 16:59:35 8

8 源同步接口設計特別有用。7系列器件中的I/O Bank與時鐘區域的大小相同。為了理解區域時鐘是如何工作的,理解區域時鐘信號的信號路徑是很重要的。7系列設備中的區域時鐘資源和網絡由以下路徑和組件組成: 時鐘輸入I/O I/O時鐘緩沖器:BUFIO 區域時

2021-03-22 09:47:30 4631

4631

引言:7系列FPGA具有多個時鐘路由資源,以支持各種時鐘方案和要求,包括高扇出、短傳播延遲和極低的偏移。為了最好地利用時鐘路由資源,必須了解如何從PCB到FPGA獲取用戶時鐘,確定哪些時鐘路由資源

2021-03-22 10:16:18 4353

4353

引言:從本文開始,我們陸續介紹Xilinx 7系列FPGA的時鐘資源架構,熟練掌握時鐘資源對于FPGA硬件設計工程師及軟件設計工程師都非常重要。本章概述7系列FPGA時鐘,比較了7系列FPGA時鐘

2021-03-22 10:25:27 4326

4326 晶振是數字電路設計中非常重要的器件,時鐘的相位噪聲、頻率穩定性等特性對產品性能影響很大。本文基于可編程晶振SI570,就Xilinx FPGA收發器輸入參考時鐘的硬件設計及FPGA軟件設計給出設計案例,供大家參考。

2021-04-07 12:00:44 3914

3914

AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515時鐘分配IC的高性能ADC的低抖動采樣時鐘發生器

2021-04-30 09:48:42 13

13 從NRZ到PAM4,信號傳輸技術的變革推動了通信和數據中心領域數據傳輸速率的重大飛躍,人們對于數據傳輸速率的需求正在以幾何倍數增長著。同時,高性能服務器和網絡基礎設施中對于時鐘產品的要求也日益嚴苛

2021-05-24 10:07:45 1649

1649 時鐘設計方案在復雜的FPGA設計中,設計時鐘方案是一項具有挑戰性的任務。設計者需要很好地掌握目標器件所能提供的時鐘資源及它們的限制,需要了解不同設計技術之間的權衡,并且需要很好地掌握一系列設計實踐

2021-06-17 16:34:51 1528

1528

解析MSP430系統時鐘資源

2021-09-26 11:39:09 1

1 RTX51tiny 復雜應用---時鐘、溫度顯示、按鍵解析

2021-11-21 13:06:03 25

25 STM32為什么要有復雜的時鐘系統首先STM32 本身非常復雜,外設非常的多,但是并不是所有外設都需要系統時鐘這么高的頻率,比如看門狗以及 RTC 只需要幾十 k 的時鐘源即可。同一個電路,時鐘越快

2021-11-23 18:21:38 8

8 MSP432P401R時鐘系統MSP432的時鐘模塊(CS),個人理解msp432最特色的功能應該是超低功耗和高性能的組合。432系列的時鐘系統主要有三個方面:1、硬件時鐘–時鐘

2021-12-16 16:54:39 5

5 第二篇文章——STM32電源、復位、時鐘電源管理電源電壓調節器可編程電壓監測器(PVD: Programmable voltage detector )低功耗模式復位Cortex-M3的復位信號

2022-01-05 14:25:10 10

10 HROW:水平時鐘線,從水平方向貫穿每個時鐘區域的中心區域,將時鐘區域分成上下完全一致的兩部分。全局時鐘線進入每個時鐘區域的邏輯資源時,必須經過水平時鐘線。

2022-06-13 10:07:26 1481

1481 ?xilinx 的 FPGA 時鐘結構,7 系列 FPGA 的時鐘結構和前面幾個系列的時鐘結構有了很大的區別,7系列的時鐘結構如下圖所示。

2022-07-03 17:13:48 2592

2592 什么是時鐘緩沖器(Buffer)?時鐘緩沖器(Buffer)參數解析 什么是時鐘緩沖器(Buffer)?我們先把這個概念搞清楚。 時鐘緩沖器就是常說的Clock Buffer,通常是指基于非PLL

2022-10-18 18:36:54 18409

18409

在5G網絡應用中,對于網絡節點的時鐘要求非常高,網絡設備需要穩定的時鐘

2023-03-15 11:12:46 900

900 HMC7043是一種高性能時鐘緩沖器,用于為具有并行或串行(JESD204B型)接口的高速數據轉換器分配超低相位噪聲參考。

2023-05-31 10:47:57 1637

1637 。高性能時鐘芯片是電子設備不可或缺的重要元器件,在服務器、交換機、基站、醫療設備中廣泛應用。但是,該領域此前一直為國外廠商所壟斷。極景微依托創始團隊在超低抖動鎖相環技術及創新時鐘電路方案領域的深厚積累,成功

2021-11-22 09:47:49 1792

1792

本章針對CW32F030C8T6的時鐘樹進行詳細解析,續第一章啟動文件的相關講解。

2023-08-17 11:42:22 961

961

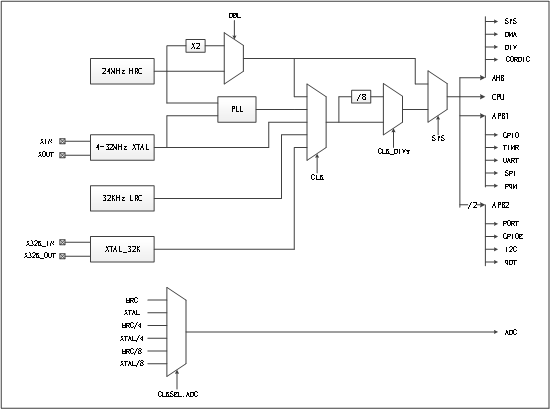

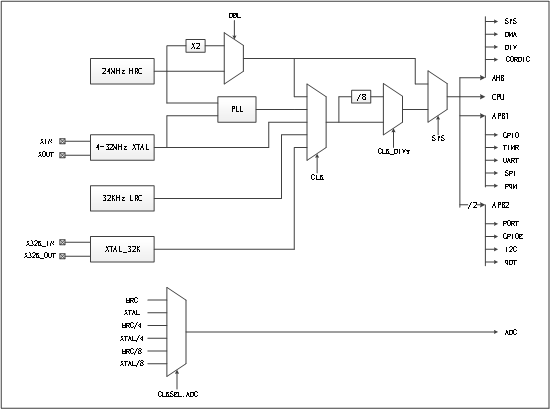

如何配置SWM系列系統時鐘?

2023-09-18 16:35:11 362

362

高性能20路PCIe時鐘緩沖器新品推介SQ82100PCI-Express(PCIe)是一種高速串行計算機擴展總線標準,主要用于擴充計算機系統總線數據吞吐量以及提高設備通信速度。目前服務器

2023-12-20 08:19:38 240

240

電子發燒友網站提供《RX和RA系列主時鐘電路和子時鐘電路設計指南.pdf》資料免費下載

2024-02-19 10:20:19 0

0 國芯思辰SC6301是高性能時鐘調節器,支持JEDEC JESD204B。當使用設備和SYSREF時鐘時,PLL2的14個時鐘輸出可配置去驅動7個JESD204B轉換器或其他邏輯設備。SYSREF

2024-02-19 09:41:40

電子發燒友App

電子發燒友App

評論