開發和驗證 FPGA IP 不僅僅是編寫 HDL,而是需要更多的思考。讓我們來看看如何做吧!

介紹

當我們開發基于 FPGA 的解決方案時,我們會盡可能利用手上的 IP,因為這會加速開發。然而,在某些情況下,我們需要使用自定義 IP 核,以應對新項目。

開發和驗證此 IP 塊會帶來一些挑戰,如果做得不正確,可能會讓項目進度變得緩慢。

當然,在使用 FPGA 時,我們需要考慮的關鍵事情之一是需要首先考慮我們希望實現的功能,以及遵循正確的開發流程。

為了說明這個過程,我們以實際項目為示例,過程如下:

定義需求

創建微架構和接口

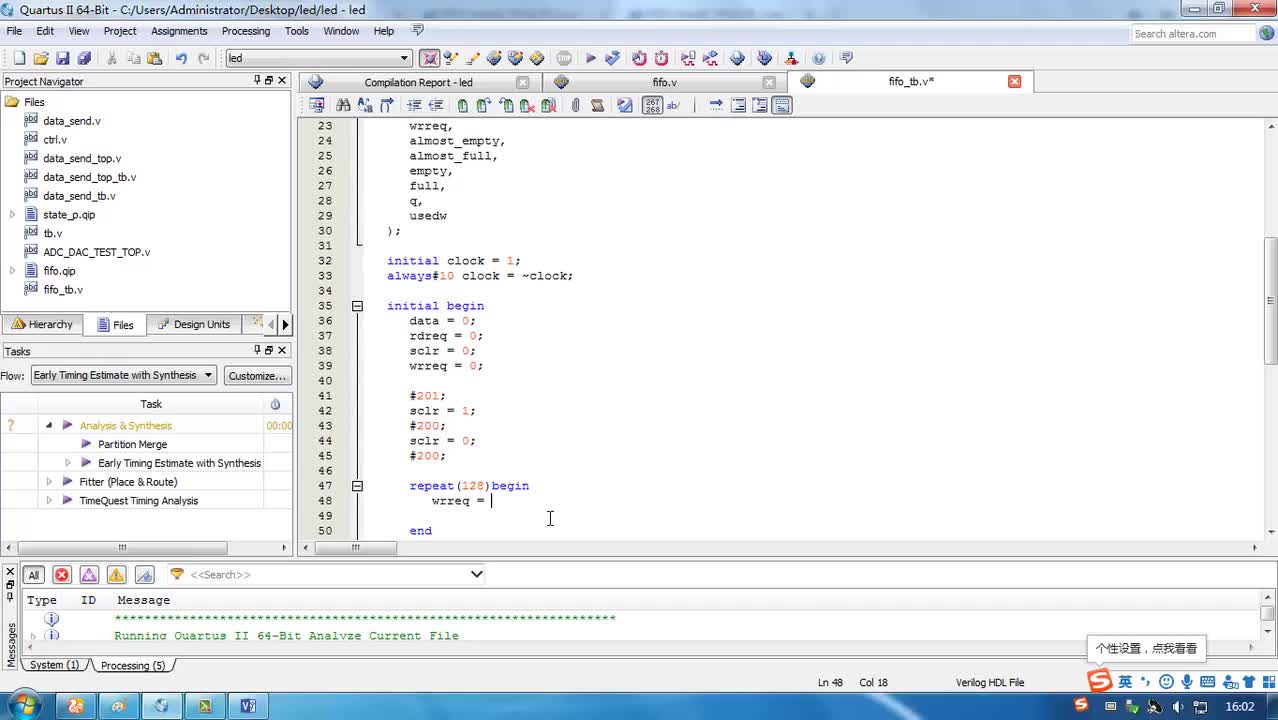

編寫模塊的RTL描述

開發 RTL 接口的總線功能模型

創建仿真平臺進行驗證

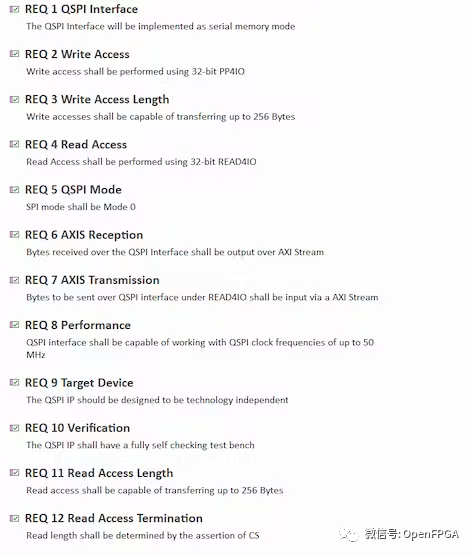

要求

示例項目,我們將創建一個簡單的 AXI Stream QSPI 從接口IP,具有以下要求:

創建IP的這些要求非常簡單。然后,我們可以將該模塊與之前的項目集成,例如:可以通過 QSPI 訪問芯片內的AXI4總線。

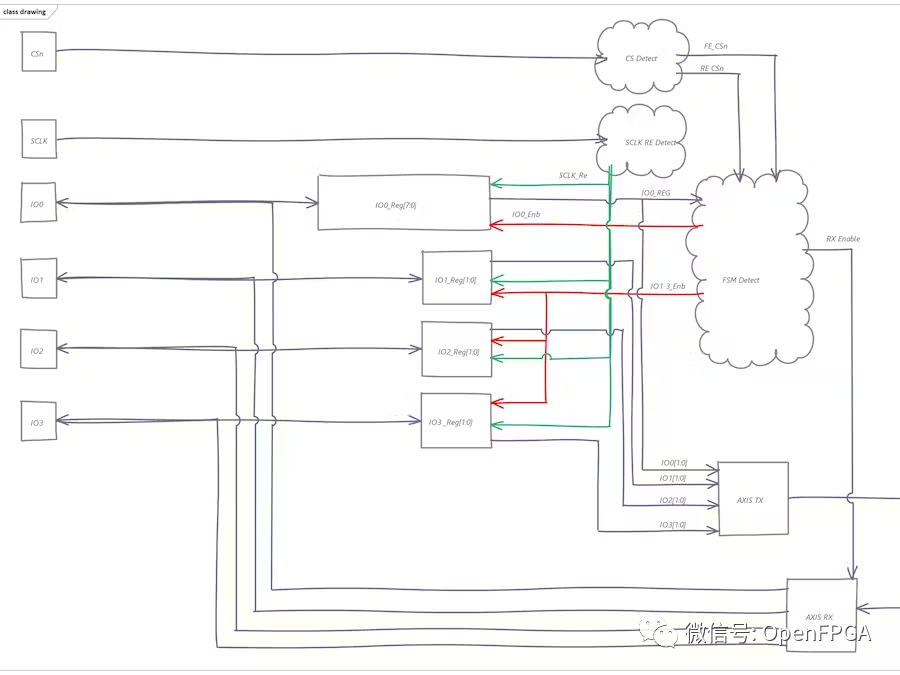

微架構和接口

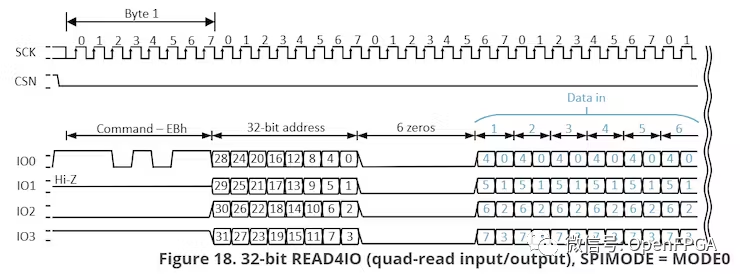

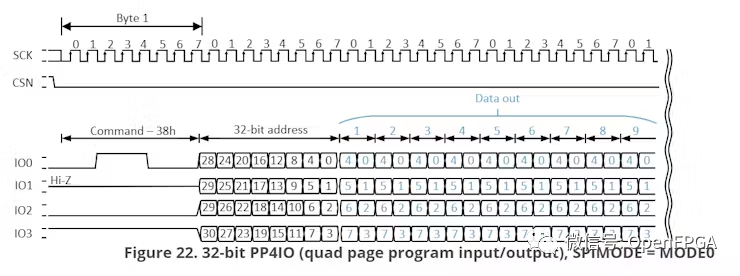

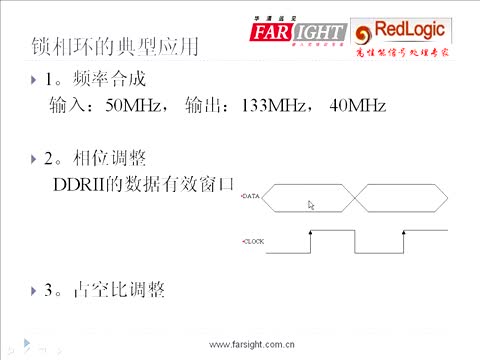

接下來我們需要創建微架構,這意味著我們需要了解串行存儲器模式下的 QSPI 是如何工作的。

READ4IO 和 PP4IO 的波形如下所示

它們首先使用單線到 IO0 來發送命令 0x38(用于寫入操作)或 0xEB(用于讀取操作)。

命令發送后,將使用所有 IO 執行事務的其余部分。

對我們架構的影響是,我們需要一個 8 元素移位寄存器用于 IO0,2 元素移位寄存器用于 IO1-3。收到命令后,我們就可以僅使用 IO0 寄存器的較低兩個元素。

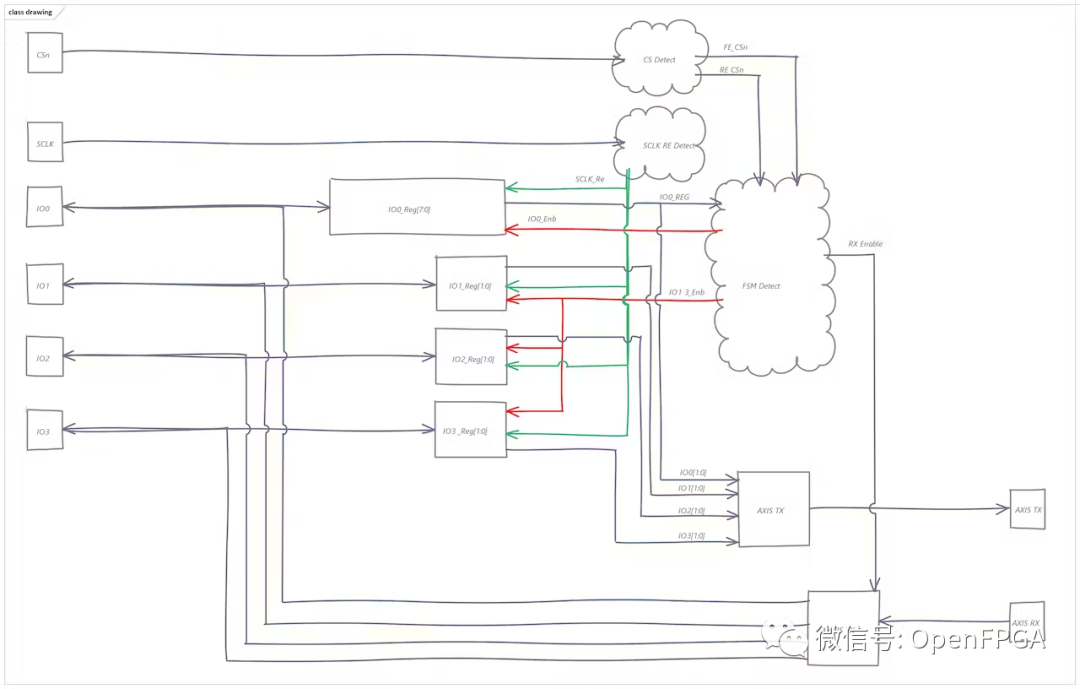

因此,我們的微架構需要能夠執行以下操作

通過識別 CSn 的下降沿來檢測新事務

啟用新事務后檢測 SCK 上的上升沿

使能數據移入 IO0 寄存器

一旦 8 位數據位于 IO0 寄存器中,具體取決于檢查是否有效的讀或寫命令

對于寫使能 IO1-3 以及 IO0 - 每兩個 SCLK 在 AXIS 接口上輸出一個字節的數據。確保 IO 驅動程序在該狀態下處于三態。

對于讀取,在虛擬時鐘周期期間,從 AXIS 接口讀取

對于在虛擬周期結束時讀取,輸出 IO0-IO3 上的數據

CSn 的取消斷言會停止事務并復位狀態機等。

微代碼架構完成后,我們就可以編寫 HDL。

設計微架構時的關鍵要素之一是以合理的方式定義接口,尤其是 FPGA 內部與其他模塊連接的接口。雖然定義自己的接口可能很爽,但是還是要選擇行業標準,例如 AXI 等。這樣不僅能夠輕松定義接口,同時確保其他開發人員在集成時能夠輕松使用它們。使用行業標準還簡化了接口驗證,因為可以使用標準 BFM,隨著時間的推移,它還會建立一個有用的 IP 模塊存儲庫,可以在多個項目中重復使用,從而減少開發時間和同類型項目成本。

因此,該塊使用 AXI Stream 通過 QSPI 接口發送和接收數據。

HDL 設計

該設計的 HDL 可以在文末看到。

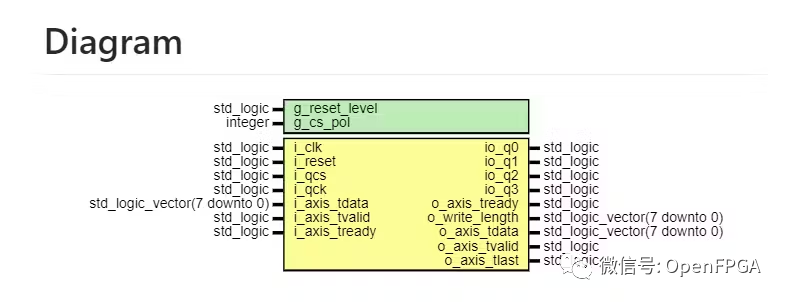

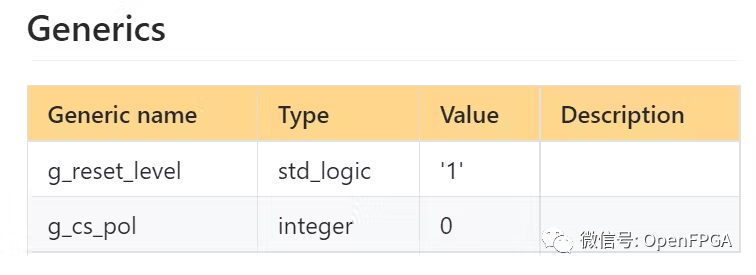

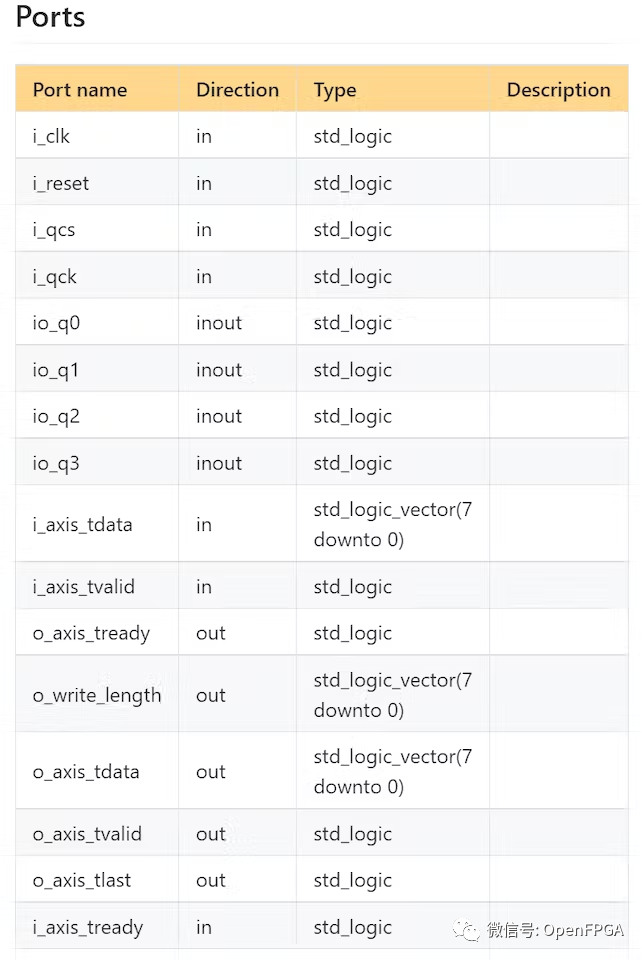

IP 的接口如下是:

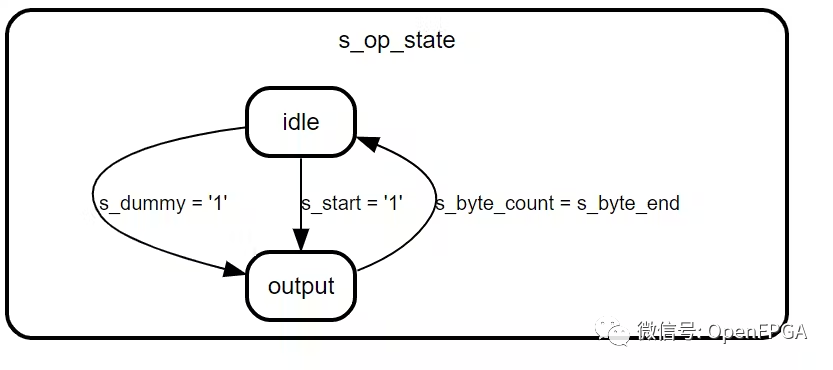

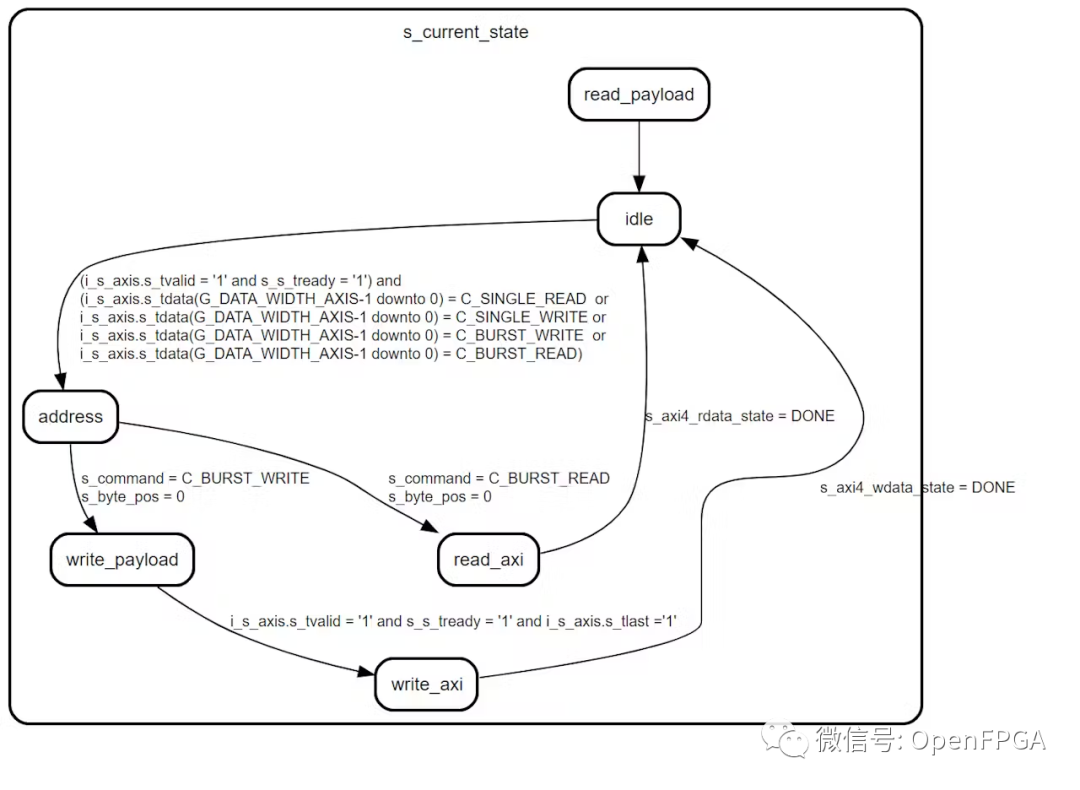

設計中的狀態機:

HDL 完成后,下一步是仿真驗證。

仿真

我們如何通過創建測試平臺來驗證 FPGA 設計是否按預期工作。測試臺對被測單元 (UUT) 施加激勵并觀察 UUT 的輸出,以確保其行為符合預期。

本次我們不想使用波形進行驗證,我們檢查 UUT 的行為并將其記錄到文件中,驗證其是否按照預期運行。

如果我們發現預期結果存在異常,我們再使用波形來調試 UUT。

每個測試用例都是一組獨特的激勵,它將特定測試應用于 UUT 以檢查該激勵的特定結果。

創建這些測試用例可能很復雜,并且是驗證過程中最耗時的部分。根據 UUT 的復雜性,可能有少量測試用例,也可能有數十個甚至數百個。

因此,我們希望將測試平臺與測試用例分開。我們使用幾個不同的抽象層來實現這一目標,包括

測試用例 - 一個或多個測試用例,通過測試框架向 UUT 施加激勵。

測試工具 - 包含 UUT 的映射以及 IP 模型(例如 RAMS、DDR 模型等)的連接

UUT - 我們正在測試的單元。

為了以最簡單的方式實現這一目標,我們將使用大量的總線功能模型 (BFM) 和事務級模型 (TLM)。

當然,我們可以將 UVM、UVVM 和 OSVVM 等框架用于這些應用程序,但是,由于該項目的目的是演示,因此我們將從頭開始。

如果本次設計可以完美完成,將使測試用例成為一系列 BFM / TLM 級別的調用和相關檢查。通過這種方式,測試用例看起來更像腳本而不是傳統的 HDL 文件。

這樣的靈活性非常重要,因為我們需要能夠適應 UUT 功能的變化,這些變化會導致需要創建更多的測試用例。

對于此應用程序,我們有以下內容:

測試用例 - 應用激勵 - 在這種情況下,我們有一個測試用例,其中包含一個簡單的測試。

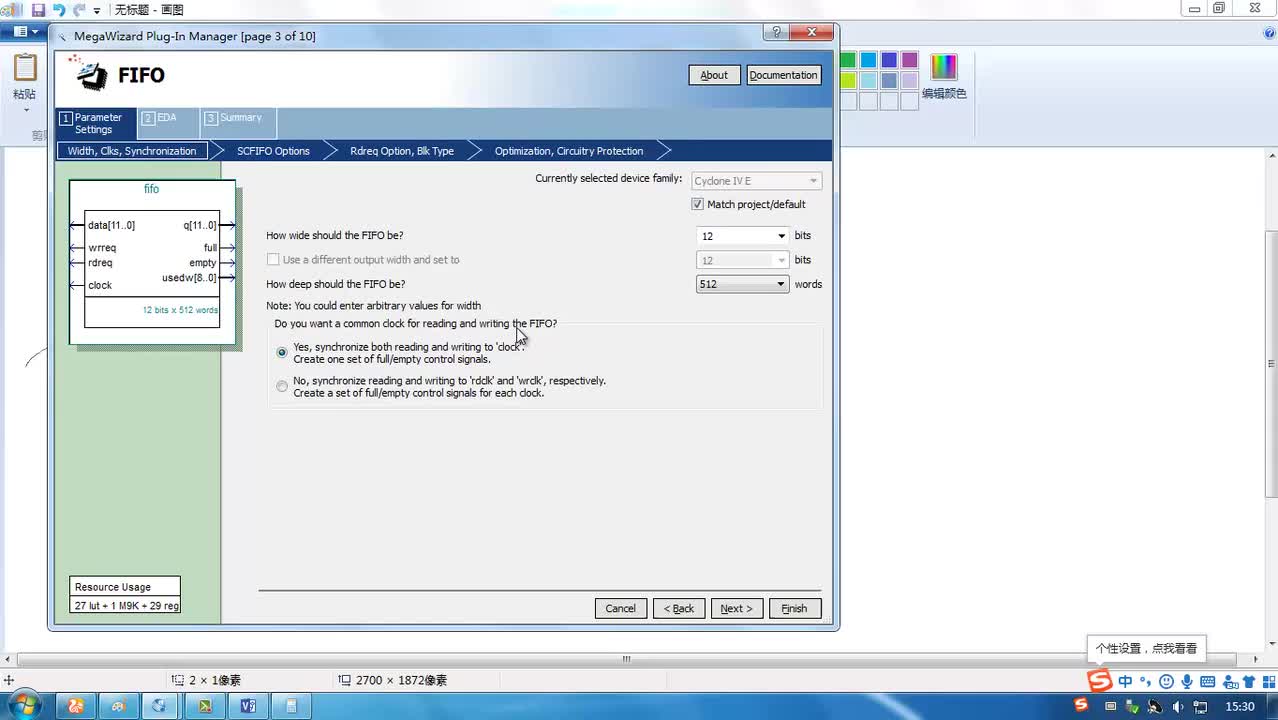

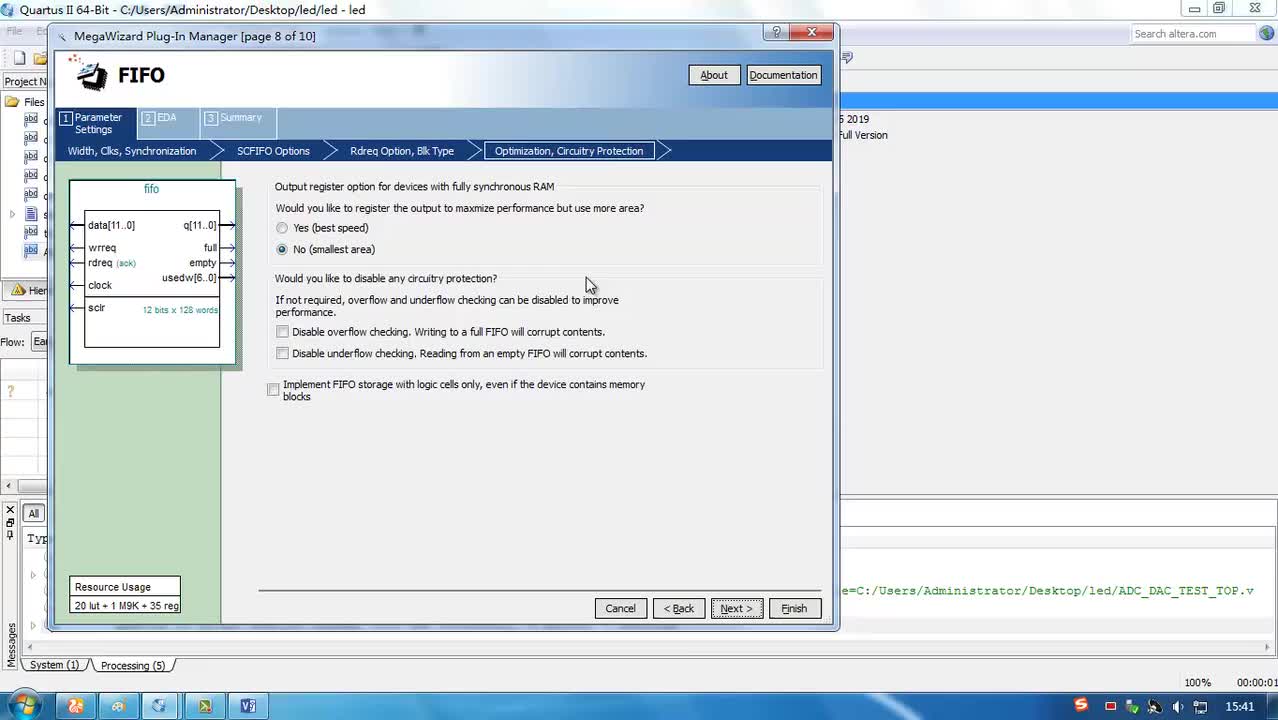

測試臺 - 包含測試臺的測試基礎設施。這包括 UUT、AXIS FIFO 和時鐘/復位電路。

UUT - 我們正在測試的 QSPI IP 核

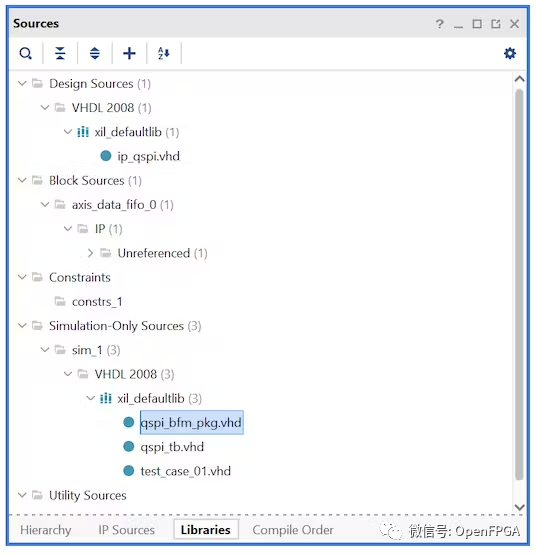

QSPI BFM 庫 - 包含許多 BFM 的庫,作為 QSPI 主設備通過接口執行讀寫操作。

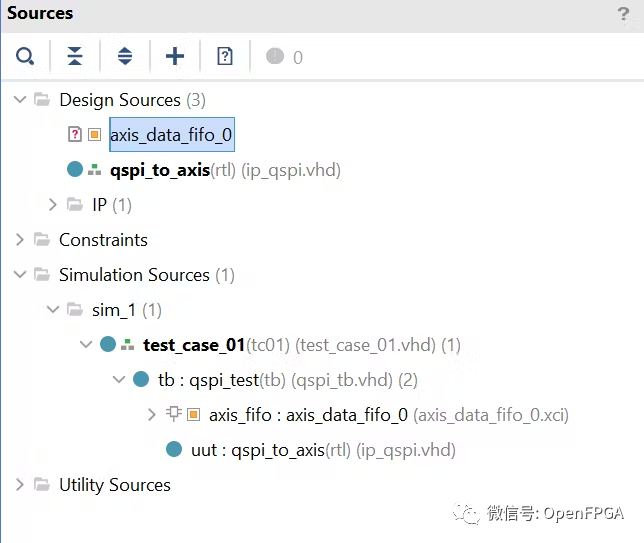

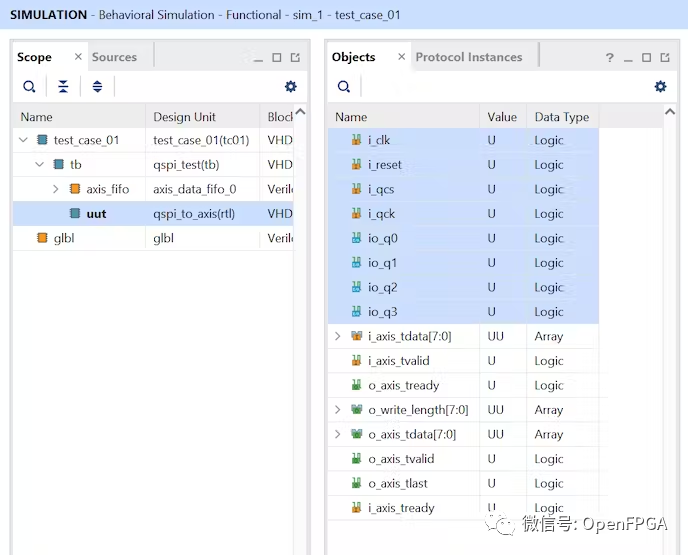

Vivado 項目

為了測試該項目,我們可以創建一個包含 HDL 和測試平臺的 Vivado 項目。我們使用 Vivado 在測試臺中提供 AXIS FIFO,允許循環回寫入的命令,以驗證讀回。

如果我們查看項目層次結構,我們將看到測試用例位于頂層的驗證結構,下面的測試臺包含 AXIS FIFO 和 UUT。

看不到該包,因為它僅在庫視圖下可用

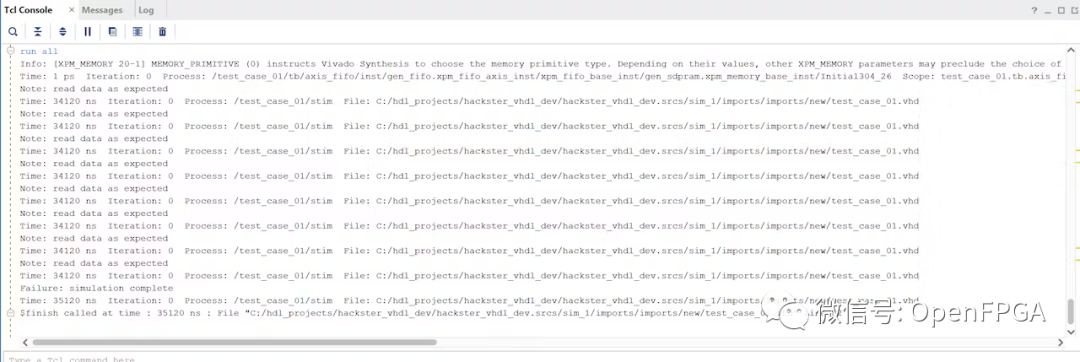

運行 HDL 行為仿真將打開波形視圖。選擇 UUT 并將信號添加到波形中。

單擊“run all”,仿真完成后將看到 IO 信號和內部信號的波形。

在這種情況下,我們期望的是,我們收到的每個寫入值與測試平臺執行此檢查時返回的值相同。

對于關鍵應用,可能不同的工程師來執行驗證并提供驗證結果。

總結

在這個項目中,我們提供了 FPGA IP 核開發的流程概要。有些流程尚未涵蓋,例如編碼規則和靜態分析等,但它為那些希望開始的人提供了很好的開端。

電子發燒友App

電子發燒友App

評論