概述 高速信號采集處理廣泛應用于各個領域,隨著科學技術的飛速發展,對信號采集處理裝置的性能要求也越來越高。在該領域,我國的研究與產業化均起步較晚,大多數國內廠商的設備依賴進口,價格昂貴,功能靈活性不足。 本團隊針對現有信號采集處理裝置采樣通道數少、動態接收范圍小、靈活性針對性差等不足,提出了更加優化、更為全面的包括采集預處理(完成模擬域的放大、濾波、傳入模擬-數字轉換模塊)、處理(基于FPGA的數字域信號處理算法)和傳輸(包括萬兆以太網SFP+和PCIe 2.0 ×8傳輸接口)三大模塊為一體的一整套解決方案。 ?

主要創新點? 1、各項參數指標較現有技術顯著提升 高速信號采集處理廣泛應用于各個領域,隨著科學技術的飛速發展,對信號的采集處理裝置也提出了越來越高的要求。 在用作數字接收機的場景下,在傳統的模擬接收機中,模擬正交混頻器難以做到嚴格的90°相位差,且I/Q兩路放大器濾波器幾乎不可能做到完全相同。 [1]專用DDC芯片,具有增益動態調節范圍小、帶外抑制差、處理精度低的缺點以及在面對不同應用需求,靈活度低針對性差。 [2]現有的一些高速采樣卡應用場景受限,必須配合一整套設備使用,且有采樣通道數少、采樣速率低、靈活性針對性差等不足。

為此,本作品提供了更加優化、更為全面的包括采集、處理和傳輸三大模塊為一體的一整套解決方案。具體技術指標如下: * 最大支持四通道同步采集; *?最大支持-10dB~+53dB,共128檔程控增益控制,0.5dB步進; *?最高支持16bit模擬-數字轉換精度; *?支持20M~125MSPS可調采樣率; *?數據傳輸到PC端最高速率達32Gbps; *?板載8GbDDR3存儲器? *?軟硬件自主研發設計的全套完善系統 本作品以自主設計的數模結合印制電路板為基礎,FPGA程序、C語言程序均為團隊自行開發,不借助任何成品模塊。硬件系統保證了信號完整性、電源完整性及電磁兼容性,工作穩定、性能良好。整個軟件系統完整、成熟、穩定性好,且系統的測試、調試程序、接口也非常完善,方便用戶使用。 ? 3、兼具板卡模式和獨立儀器模式 *?板卡模式下,可將多卡并行復用,實現高效擴展 *?板卡模式下,可將多塊多通道高速信號采集處理卡插入機箱中的PCIe插槽,通過板間同步信號的連接,實現多卡并行工作,從而方便地成倍擴展通道數量。 *?獨立儀器模式下,可遠離接收端PC機,實現超遠距離傳輸 *?與傳統嵌入于機箱的信號處理板卡相比,本平臺在兼具傳統的板卡模式之余,設計了萬兆以太網SFP+接口,可作為獨立儀器,遠離接收端PC機放置,實現超遠距離高速傳輸。此外,由于其獨立性強、體積小,為嵌入信號源端提供了可能。

? 本系統已申請國家發明專利、實用新型專利以及軟件著作權。本系統已申請三項國家發明專利、三項實用新型專利和兩項軟件著作權。 三項已授權實用新型專利如下: *?《一種核磁共振信號采集處理裝置》,201721626471.9 *?《一種多通道寬動態范圍高速信號采集處理裝置》,201822012511.1 *《基于FPGA的可變帶寬的核磁共振信號實時處理系統》,201820448016.2 ? 兩項實審中發明專利如下: *?《一種核磁共振信號采集處理裝置》,201711227275.9 *?《一種基于FPGA的磁共振信號實時處理方法》,201711233672.7 一項初審中發明專利如下: *?《一種多通道寬動態范圍高速信號采集處理裝置》,201811465362.2 兩項軟件著作權如下: *?《多通道磁共振信號數字下變頻軟件系統》,2018SR215409 *?《多通道高速信號采集處理軟件系統》,2019SR0544832 ? 系統架構?

1.?系統設計指標與系統總體架構

1.1 系統設計指標

系統擬實現的總體主要技術指標如下: *?通道數:四通道; *?增益調節范圍:-10dB~+53dB; *?增益調節步進:0.5dB,共128檔程控增益控制; *?采樣率:20M~125MSPS; *?采樣精度:16bit; *?板載數據存儲容量:8Gb; *?數據上傳到PC端速率:32Gbps;

1.2?系統總體方案

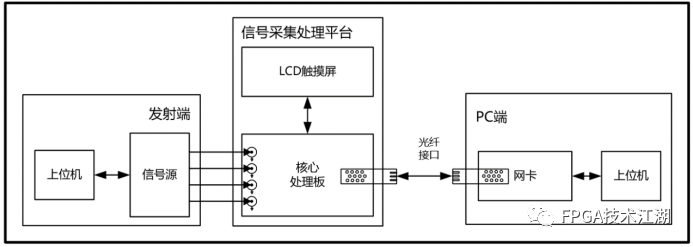

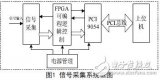

整套系統的架構如圖2-1所示。以核心處理板為核心,由信號源產生的待處理模擬信號通過同軸線纜連接到核心處理板的信號接口,同時,連接同步時鐘等其他相關信號到核心處理板。LCD顯示屏通過FFC/FPC軟排線連接到核心處理板的ARM處理器上。在核心處理板上完成處理后的數據通過光纖連接到PC端。

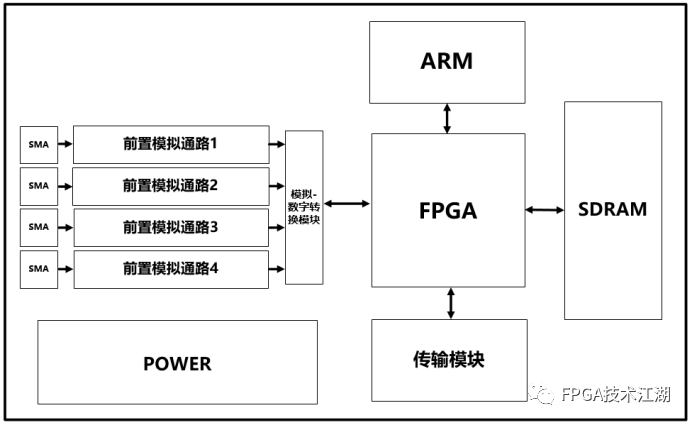

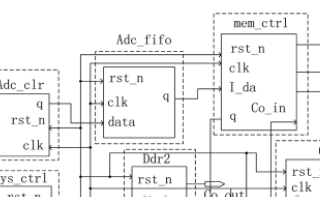

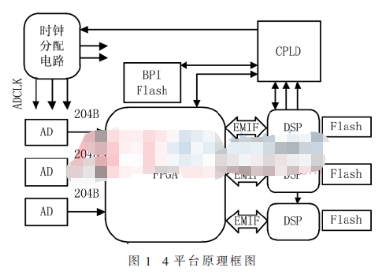

? 圖2-1 系統總體實現架構方案 核心處理板總體架構方案如圖2-2所示,主要包括以下部分:四路模擬信號采集模塊、核心處理模塊、數據片外存儲模塊、與PC機端的數據及控制信號交互模塊以及電源模塊。

圖2-2?核心處理板總體架構方案 ? 2.?指標論證與方案設計

2.1?模擬前端方案論述

為適應不同場景需求,本核心處理板上設計了可選的兩套模擬前端放大方案,包括兩路寬帶(10 MHz~200MHz)放大和兩路特定頻點(63.5MHz)的放大。 以針對63.5MHz特定頻點的放大為例,整條通路上包括兩級壓控增益放大器用于實現0.5dB的調節步進;一級用于抗混疊濾波的帶通濾波器;一級固定增益放大器;一級用于進一步抑制由于放大器的非線性所產生的諧波的低通放大器。其中,VGA的增益可以通過FPGA實時調節。 四路經過放大/縮小的信號被傳入模擬-數字轉換芯片,本系統中所選用ADI公司的串行模數轉換器AD9653。AD9653擁有4個通道,最高16bit精度,采樣速率最高可達125 MSPS。 ?

2.2?核心處理器方案論述

多通道高速信號采集處理平臺需要支持對最多四路最高125Mbps的模擬信號的實時處理,需要支持高速(1Gbps)的 LVDS 接口。此外,由于要完成大量信號處理類算法,因此對DSP資源需求量也很大。而為了將處理完的數據及時發送到PC端,需要支持高速串行SERDES接口。整個處理過程龐雜,對時序要求嚴格,因此,需要核心處理器具備強大的處理能力及豐富的邏輯資源。 為滿足上述要求,本系統采用Xilinx公司的Kintex-7系列FPGA,具體型號為XC7K325T-2FFG900C。該芯片擁有326,080個邏輯單元,16,020Kb的片上RAM存儲資源,840個DSP48資源,最大時鐘輸入速率為933MHz,用戶I/O口為500個,支持外部擴展SDR、DDR、DDR2 SDRAM和DDR3 SDRAM?,支持最高1,400Mbps的LVDS接收,GTX bank支持12.5Gbps的收發。 結合外設接口傳輸需求和FPGA代碼的資源消耗量,綜合評估,該芯片是在能夠滿足本系統的各項需求的前提下,具有較高性價比的選擇。

2.3?數據緩存方案論述

本系統緩存方案的設計分為FPGA片上存儲和板載存儲器兩部分。FPGA片上緩存的優點是訪問迅速并且處理時延短,但是容量非常有限。板載存儲器緩存的優點是容量大,但訪問讀寫速度相對慢,且面臨跨時鐘域亞穩態等問題。 基于上述優缺點,對于存儲資源的使用如下:面向PC機的傳輸利用板載DDR3 SDRAM,其他數據緩存利用FPGA片上存儲資源。 其中,板載存儲器DDR3 SDRAM選用4片鎂光科技的 MT41K128M16JT-93K,為FPGA提供額外的8Gb的存儲空間,使用1,600Mbps傳輸速率的設計方案。

2.4?萬兆以太網接口方案論述

萬兆以太網遵循IEEE802.3ae 標準,保留了與 10/100/1000M 三速以太網相同的數據幀格式,幀長度的界定,但在傳輸速率上具有顯著提升,此外,該標準指明通過光纖介質進行信號的傳播。 在網絡接口的光模塊選擇上,SFP+相比于 XFP 體積小,適配 IEEE802.3ae協議并遵循SFF-8431 協議,其 PHY 和 MAC 層轉換由FPGA處理器實現。因此本系統選擇SFP+光模塊作為網絡硬件接口。

2.5 PCIe接口方案論述

為了能在需要時作為板卡模式使用,本核心處理板同時配備了PCIe2.0 ×8的傳輸方案,單通道帶寬為500MB/s,采用8b/10b 編碼方式,其總共的有效數據帶寬為32Gbps。超出本系統所需基本需要,并留有余裕,便于以后功能擴展。 ? 設計演示?

1.電源測試

在確認電源網絡和地網絡之間不存在短路現象之后,即可上電對各路電源進行測試。在測試過程中主要關注輸出電壓值精度,及其與理論設計值之間的誤差,以及紋波。各個電源電平和紋波測試結果如下表5-1所示。從表中可以看到,各電壓均正確且電源紋波控制得比較好,是各負載芯片可以正常工作的重要前提。 表5-1?電源電平和紋波測試結果

?

| 電源名 | 設計電壓(V) | 實際電壓(V) | 誤差 | 紋波峰峰值(mV) |

| 9V_A | 9 | 8.9433 | 0.63% | 20.50 |

| 5V_A | 5 | 4.9705 | 0.59% | 15.50 |

| 3P3V_D1 | 3.3 | 3.2817 | 0.55% | 13.20 |

| 3P3V_D2 | 3.3 | 3.2944 | 0.17% | 15.80 |

| 3P3V_D3 | 3.3 | 3.2797 | 0.62% | 16.50 |

| 2P5V_D | 2.5 | 2.4978 | 0.09% | 17.80 |

| 2V_D | 2 | 2.0063 | 0.32% | 12.50 |

| 1P8V_A | 1.8 | 1.7927 | 0.41% | 15.40 |

| 1P8V_D | 1.8 | 1.8039 | 0.22% | 13.40 |

| 1P5V_D | 1.5 | 1.4948 | 0.35% | 11.60 |

| 1P2V_D | 1.2 | 1.2015 | 0.13% | 20.80 |

| 1V_D1 | 1 | 1.0158 | 0.16% | 9.80 |

| 1V_D2 | 1 | 0.9960 | 0.40% | 13.6 |

| 0P75V_REF | 0.75 | 0.7443 | 0.76% | 8.0 |

| 0P75V_VTT | 0.75 | 0.7459 | 0.55% | 8.8 |

?

2.復位和時鐘模塊

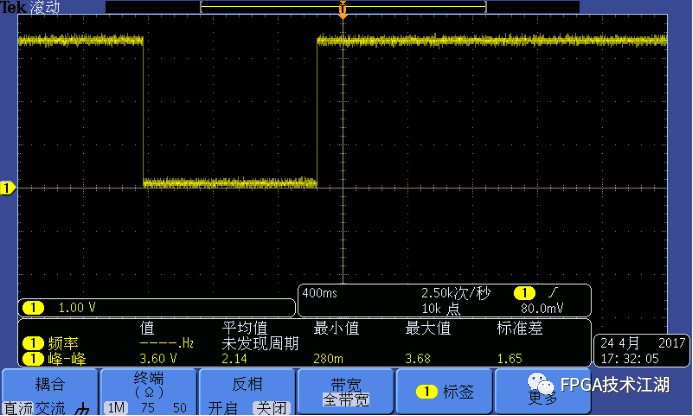

首先,測試復位信號。針對全局復位信號進行測試。可以看到復位信號輸出的電平變化如圖5-1所示,當用手按鍵時,全局復位信號置為低電平;當松開按鍵時,信號恢復成高電平。

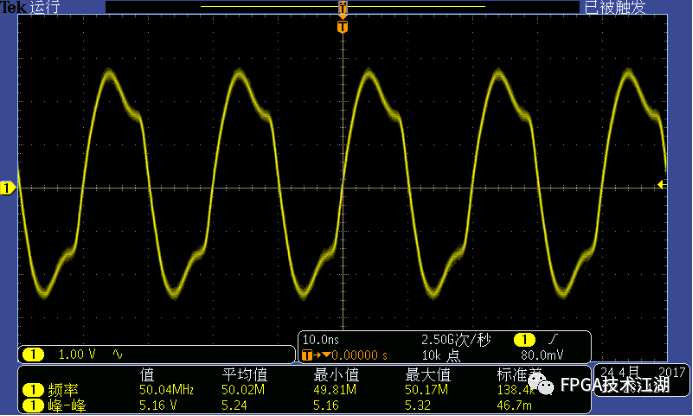

圖5-1?復位信號測試 其次,測試時鐘信號。板上時鐘信號眾多,包括有50MHz單端時鐘,用于操作系統和外設的工作;200MHz差分時鐘,用于邏輯觸發時鐘;156.25MHz差分時鐘,用于萬兆以太網的IP核輸入時鐘。以50MHz單端時鐘的測量為例,如圖5-2所示為測試結果。

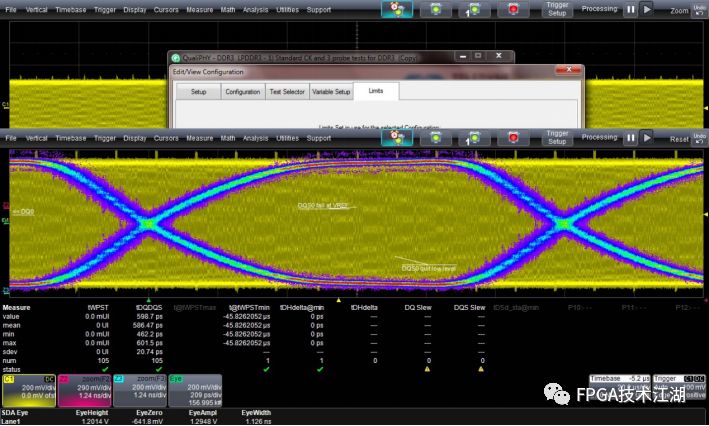

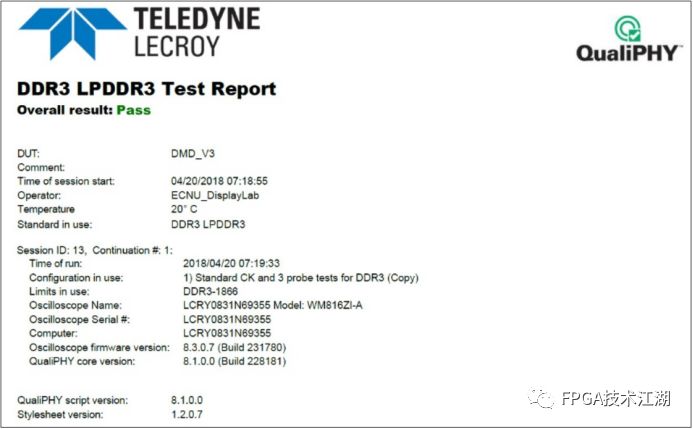

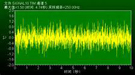

圖5-2?時鐘信號測試 ? 3.?DDR3信號測試 測試FPGA外部緩存DDR3的信號完整性。DDR3的運行速率為1600Mbps,編寫測試程序持續對DDR3進行讀寫。 利用示波器的三個差分探頭分別測試CLKP/CLKN(黃色)、LDQS/LDQSN(粉紅色)、DQ0/GND(藍色),能看到如圖5-3所示測試結果。 800MHz差分時鐘眼圖,如圖5-4所示。可以由示波器讀出該信號眼高為1.1366V,眼寬為578ps,眼交叉比為50.37%,差分時鐘設計指標通過了LeCroy 示波器的QualiPHY對1600Mbps DDR3的標準測試,因此眼圖各指標符合設計要求。生成的測試報告結果,如圖5-5 所示。

圖5-3 DDR3部分信號測試結果圖

圖5-4?DDR3差分時鐘眼圖測試結果圖

圖5-5 DDR3 物理層一致性測試報告

4.?萬兆以太網數據鏈路測試

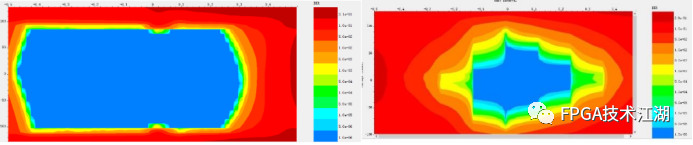

首先針對SFP+數據鏈路,利用Vivado軟件中IBERT IP核對萬兆以太網的速率進行測試。使用光纖將TX和RX端環回互連,測試編碼使用PRBS-31。圖5-6(I)是使用千兆光纖,可見眼圖飽滿,信號完整性好。圖 5-6(II)是使用萬兆光纖,測試協議類型選用10GBase-R,當數據速率是 10.3125Gbps 時測試收發數據鏈路,可見眼圖受制于自身速率和板材的損耗角影響,雖然不如千兆時飽滿,但測試結果誤碼率為0,能夠滿足需求。

? ? ? ? ? ? (I)? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?(II) 圖5-6 SFP+數字眼圖測試

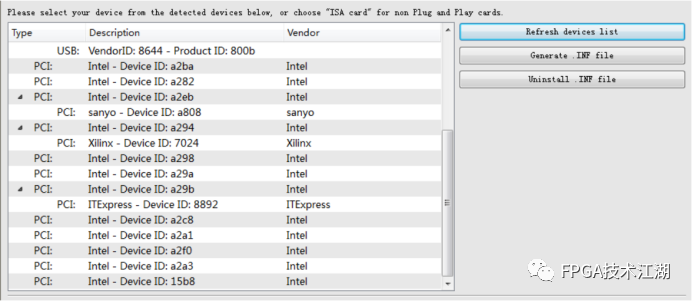

5. PCIe數據鏈路測試

對于PCIe,如圖 5-7所示,在主機中識別到EP設備。

圖5-7?主機識別PCIe 設備 編寫測試程序,由主機與核心處理板環回發送接收數據,然后統計數據的傳輸速率。如表5-2所示,PCIe的寫存儲器平均速率是1467.6MB/s;PCI的讀存儲器平均速率是1665.2MB/s該結果符合設計要求。 表5-2 PCIe性能測試

?

| 項目 | 1 | 2 | 3 | 4 | 5 |

| 寫存儲器 | 1475MB/s | 1472 MB/s | 1451 MB/s | 1434 MB/s | 1506 MB/s |

| 讀存儲器 | 1591MB/s | 1680 MB/s | 1687 MB/s | 1665 MB/s | 1703 MB/s |

?

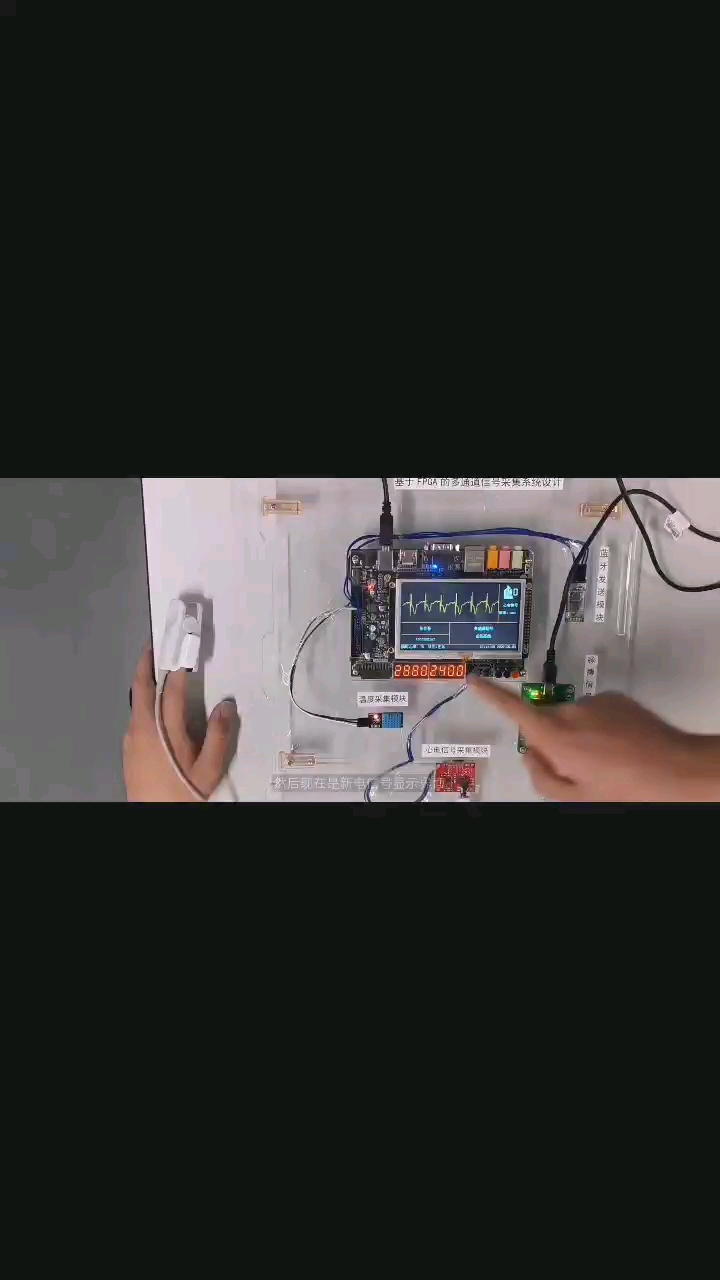

6.系統功能測試

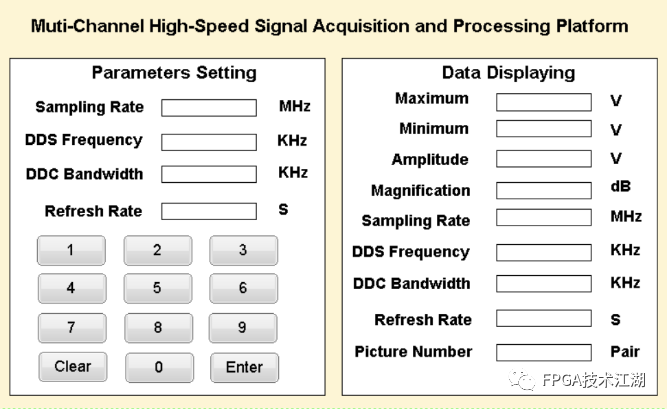

在完成對板上各模塊及功能測試后,對系統進行級聯測試。系統的實物連接如圖5-8所示。 將用于信號產生的PC機的模擬信號輸出接口,用同軸線纜連接到核心處理板的一路信號接口,同時,用同軸線纜連接同步時鐘等其他相關信號到核心處理板。LCD顯示屏通過FFC/FPC軟排線連接到采集處理板上。在核心處理板上完成處理后的數據通過光纖連接到PC端。 ? 連接好系統后,給核心處理板上電,負責收發的兩臺PC機開機。在如圖5-9所示的LCD觸摸液晶屏的界面上設置相關參數。

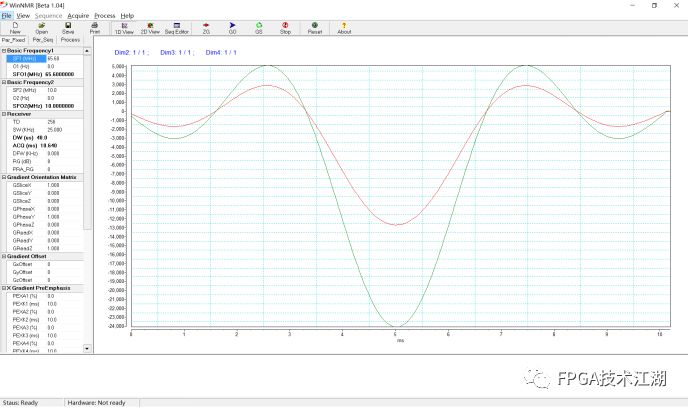

圖5-9 LCD參數設置界面 將發送端的上位機打開,設置各項參數,發送模擬核磁共振信號。如圖5-10所示。

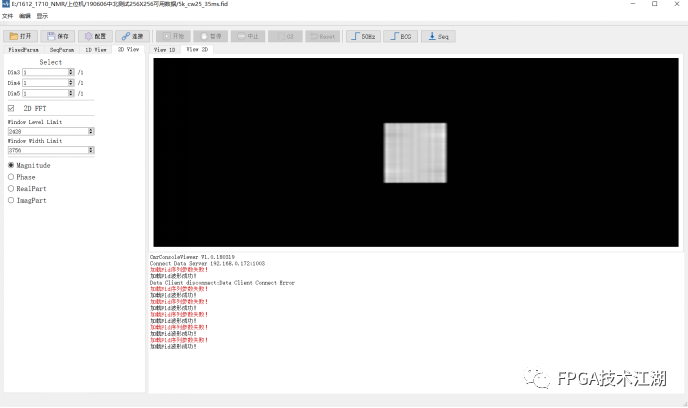

圖5-10 發送端上位機界面 將接收端上位機打開,調入自動保存的文件,可以看到恢復出來的圖像。如圖5-11所示。

圖5-11?接收端上位機界面 ?

審核編輯:黃飛

?

電子發燒友App

電子發燒友App

評論