隨著數字技術的進步,高速、超大規模集成電路廣泛使用, 3G 移動終端 基帶信號 處理系統正朝著靈活、高度集成化、模塊化、通用化的方向發展。基帶信號處理器是數字技術與通信技術相結合的產物,它能靈活處理數字基帶信號,調制無線信號以便實現同通信網絡系統前端基站的無線通信。文章設計了一種基于先進微處理器(ARM)、數字信號處理(DSP)和現場可編程門陣列(FPGA)體系結構的3G移動終端基帶信號處理器。這種體系結構的優點在于當提供更能滿足客戶需求的先進處理器時,整個系統容易集成,而且可以通過軟件方法方便地增加功能,而不必定制只讀存儲器(ROM)編碼的新芯片。同時系統使用軟件實現聯合檢測和信號解碼功能,通過軟件更新輕松實現對系統的任何升級,無需硬件修改。

1 設計思路

隨著實時數字信號處理技術的發展,ARM、DSP和FPGA體系結構成為3G移動終端實現的主要方式。本文的設計通過ARM對目標及環境進行建模、運算,生成網絡協議仿真數據庫,應用DSP進行數據調度、運算和處理,最后形成所需的調幅、調相、調頻等控制字,通過FPGA控制收發器芯片產生射頻模擬信號。利用數字芯片之間的通用性,ARM與DSP間的通信,不僅能實時處理接收和發送的數據,還可以適應不同移動網絡的具體要求,同時方便加載新的程序。FPGA數字頻率合成技術以其在頻率捷變速度、相位連續性、相對帶寬、高分辨率以及集成化等方面的優異性能,為 3G移動終端射頻信號模擬的實現方式提供了選擇。

2 硬件實現

本系統主要部分是ARM主控模塊、DSP實時數據處理模塊和FPGA信號生成模塊。ARM主控模塊實現物理層與協議棧的通信,接收高層的指令,執行相應的任務。如協議棧需要在某些子幀中的某個或幾個上行時隙發送數據到核心網,在某些子幀中的某個或幾個下行時隙接收核心網的數據,這時把所有的指令和數據都存放在同步動態隨機存儲器(SDRAM)中,然后通知DSP去執行。DSP實時數據處理模塊得到數據和命令后,首先處理發送數據,對數據進行信道編碼調制、CRC附著、交織、擴頻調制等,然后處理接收數據,如信道估計、去干擾、CRC校驗、信道解碼、解擴、唯特比解碼等。FPGA為信號生成模塊,管理26 M時鐘,進行分頻的任務,控制模擬基帶(ABB)的自動發送功率控制(APC)、自動接收增益控制(AGC)、自動頻率控制(AFC)等,同時也實時控制射頻(RF)的工作。當DSP中的一些算法非常穩定后,可以用FPGA來實現這些算法,減少DSP的處理負擔。其硬件電路如圖1所示。

2.1 接口

ARM與DSP的數據交換是通過雙口隨機存儲器(RAM)來實現的,即圖1中的SDRAM,起到上下行控制命令、參數和數據等緩存和交換的作用。這里收發雙口RAM數據線的位數大小為16 bit, SDRAM 存儲大小為128 M。硬件中斷信號線8(INT8)與硬件中斷信號線9(INT9)每5 ms相互產生一次,等于TD-SCDMA空口信號的子幀中斷,同時也可以作為ARM與DSP的控制命令、響應來實現ARM與DSP之間的通信。

FPGA的主要的接口有data_out[15:0]接口,與數模轉換器(A/D)接口和與RF接口。

data_out[15:0]接口用來輸出FPGA運算的結果,與DSP的數據總線掛接在一起,在FPGA內部設置一個三態門,開門信號就是 FPGA的片選信號CE。當CE不選通的時候,三態門輸出為高阻狀態,不會影響DSP的數據總線。在每一個樣點間隔的時間內,FPGA運算出相關值的實部和虛部,將它們分別鎖存在4個16 bit的鎖存器中,并將與DSP相連的data_ready信號置高電平,表示數據已經準備好。DSP檢測到data_ready為高后會進行讀操作,用地址總線的高幾位產生出片選信號將FPGA選通,通過地址總線的低兩位A0、A1來選擇4個鎖存器的其中一個,依次讀取實部和虛部兩個32位數的高16位和低16位。FPGA內部會對DSP的讀操作計數,確認數據分4次讀出后,則將data_ready置低,直到下一次運算完畢后再抬高。FPGA的頻率、相位和幅度控制字的設置和控制信號的產生由TMS320C5510完成,FPGA可以看作是異步存儲設備與TMS320C5510的外存儲器接口 (EMIF)相連,EMIF采用32 bit總線。

與數模轉換器(A/D)接口的A/D一端連接ABB,另一端連接FPGA,傳輸要發送的數據和移動網絡接收的數據。在與A/D的接口部分中,有 3個輸入端RIF、PS和CLK。RIF用來串行輸入A/D轉換來的樣點值;PS為幀同步信號,它在輸入到FPGA后用來驅動FPGA內部的總體控制模塊;CLOCk為移位時鐘,它控制A/D與FPGA之間數據串行傳輸的移位。

與RF接口主要是用來控制發送和接收RF芯片工作。

2.2 主控模塊

主控模塊負責控制和協調各種工作,ARM采用TI公司生產的開放式多媒體應用平臺(OMAP)微處理器,通過集成鎖相環倍頻系統主頻可以達到 66 MHz,最大外部存儲空間可達256 MB,片上資源豐富,外圍控制能力強性價比高。由它控制DSP模塊接收網絡發送的命令及參數,實現無線自由的協議通信。

2.3 實時數據處理模塊

實時數據處理模塊[1]通過共享內存與ARM實現發送的命令、傳輸參數和數據,根據設定的 移動終端 工作狀態,如Cell Search、隨機接入過程(RA)、專用控制信道(DCCH),及目標、環境的實時動態計算FPGA的控制字。同時也通過共享內存上報從網絡接收的數據和信息傳輸給ARM;通過鎖存器向處理板提供控衰減控制信號實現睡眠,來達到省電。DSP采用TI公司C5000系列中的TMS320C5510,系統時鐘達600 MHz,數據處理速率可以達到4 800 MIPS。提供32/16 bit主機口,具有兩個獨立的外部存儲器接口,其中EMIF支持64 bit總線寬度。

2.4 FPGA模塊設計

本文的設計采用Stratix系列芯片,內嵌多達10 Mbit的3種RAM塊:512 bit容量的小型RAM、4 KB容量的標準RAM、512 KB的大容量RAM。FPGA模塊具有True_LVDS電路,支持低電壓差分信號(LVDS)、低電壓正射極耦合邏輯(LVPECL)、準電流模式邏輯 (PCML)和超傳輸模式(HyperTranport)差分I/O電氣標準,且有高速通信接口。本設計提供了完整的時鐘管理方案,具有層次化的結構和多達12個鎖相環(PLL)。Stratix系列使用的開發軟件是ALTEra公司提供的新一代開發軟件QUARTus II。

該系列芯片的最大特色是內嵌硬件乘法器和乘加結構的可編程DSP模塊,適用于實現高速信號處理。這種DSP模塊是高性能的嵌入算術單元,它可以配置為硬件乘法器、加減法器、累加器和流水線寄存器。Stratix系列具有多達28個DSP模塊,可配置為224個嵌入乘法器,可以為大數據吞吐量的應用提供靈活、高效和有價值的方案。這些DSP模塊可以實現多種典型的DSP功能,如有相關器、限沖擊響應(FIR)濾波、快速傅立葉變換(FFT)功能和加密/解密功能等,其中相關器算法設計是各種其他算法實現的基礎和基本組成部分。

移動終端系統接收到的射頻信號經過前端預處理后,送到A/D采樣,然后通過串行方式輸出樣點值到FPGA[2]。每個樣點值是用10 bit的二進制補碼表示的,需先通過一個串/并轉換器轉化為寬度為10 bit的并行信號。首先樣點值要進行的是希爾波特變換,希爾波特變換有多種實現方法,這里采用一個129階的濾波器來實現,濾波器的抽頭系數由 MATLAB函數Remez產生,得到與其正交的另一路信號;然后以這兩路信號分別作為實部和虛部,與本地序列進行相關運算,將相關值的實部和虛部送給 DSP做后續處理。這樣,DSP才可以通過先對相關值求模,然后對模值出現的峰值的間隔、幅值和數目等信息進行判斷和進一步處理,來確定是否捕捉到信號。相關器算法FPGA設計的內部結構框圖如圖2所示。

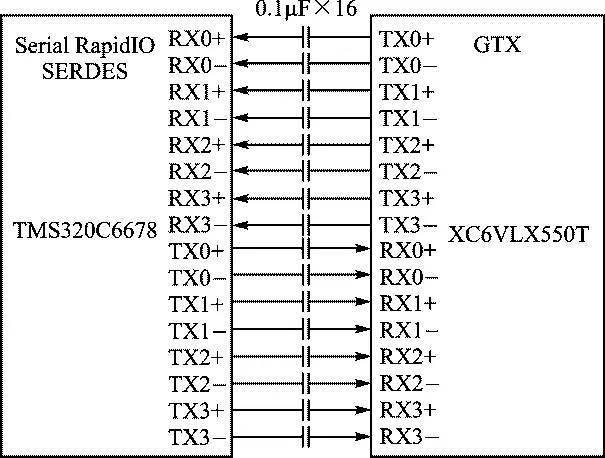

2.5 PFGA與RF的接口、總線及時序控制設計

FPGA與RF的接口、總線及時序控制設計如圖3所示。

為了增加信道容量、改善帶寬效率,TD-SCDMA通過利用上行鏈路(反向鏈路)同步、軟件無線電和智能天線的技術將時分雙工(TDD)與 CDMA結合起來。TD-SCDMA要求手機的射頻部分具有快速的切換時間、高的動態范圍以及發送機和接收機部分的高線性度。MAX2410是一個完整正交發射器,它由一個正交調制器、可變增益IF和RF放大器組成。MAX2309是一種為基于CDMA的單頻單模蜂窩電話系統設計的IF接收機,其輸入頻率范圍經過優化達到70 MHz~300 MHz,在35 dBm增益下達-33 dBm,在-35 dBm增益下達+1.7 dBm。FPGA控制RF主要通過4個RF控制寄存器:A word寄存器、 B word寄存器、 C word寄存器和 D word寄存器。

3 軟件實現

移動終端軟件包括應用層軟件、通信協議軟件和物理層軟件3部分。

應用層軟件LAY 4-7:包含人機界面(MMI)和系統應用層協議(S/W)部分,MMI為移動終端使用者接口,S/W類似移動終端的操作系統。

通信協議軟件LAY 2-3:該部分軟件較大,主要為通信協議,主要保證無線通信系統可以在各種狀況順暢互通。

物理層軟件LAY 1:負責協調DSP、其他硬件和軟件。物理層軟件的設計將能實現節能的特性、多資源、多時隙的處理、數據包和對其他網絡系統的監測。在設計物理層軟件時的還要對相鄰小區的監測,特別是當相鄰小區間彼此還沒有同步的時候。

移動終端 軟件各個模塊主要實現與硬件的對應關系如下:

應用層軟件LAY 4-7和通信協議軟件LAY 2-3軟件的實現主要是在ARM中實現,假如LAY 4-7需要一些特別高要求的應用時,可以再增加相應的硬件模塊,而不影響原有的架構,如增加高要求多媒體的處理和播放;物理層軟件LAY 1主要在DSP和FPGA中實現。

在軟件編程時ARM和DSP可以使用C語言來實現,使用的調試工具為CCS軟件,當DSP中有一些算法非常成熟后,移動通信對這塊的實時性要求比較高時,應該用匯編語言來實現,在FPGA中可以用VHDL語言來實現。在編程是首先盡量定義好各個功能模塊的任務,然后定義好各個功能模塊的接口參數等,在可以不用全局變量的時候盡量不用。

另一個主要挑戰是在TD-SCDMA終端里實現聯合檢測算法,特別是關于算法的時間優化。DSP和FPGA之間的任務分配上要有一個合理協調的分工,這樣能夠最大限度的發揮這兩個處理器的功能。在實際軟件編程中,算法程序計算量大、編碼延時過長,因此

需要在保證質量的前提下對算法進行優化。在滿足精度要求下,進一步將算法簡化,粗化搜索范圍來降低計算量;對于高級語言程序代碼,用混合匯編、去除嵌套循環等方法進行代碼優化,提高代碼效率。

4 結束語

本實驗研究是在南昌大學自然科學基金Z03333的資助下完成的。該系統很好的實現了 3G 移動終端處理功能,但實際環境比仿真環境更復雜,需要給出解決辦法,然后再驗證。目前該方案實現了384 kb/s工作,使用3個時隙(每個時隙128 kb/s);實現了基于高速下行分組接入(HSDPA)技術提高數據速率,它類似于WCDMA和CDMA2000標準所提供的速率。開發的3G芯片組能夠滿足消費者對于改善性能和功能的要求,同時又保持了相同或更低的價格。

電子發燒友App

電子發燒友App

評論