隨著計算機、DSP、超大規模集成電路等技術的發展,畫面分割器開始采用硬件設計。首先,將各路視頻信號轉換成數字視頻信號;然后,在數字領域對各路視頻信號進行處理。使電路的設計、調試得到了很大的改善。但是,設計中所使用的獨立的邏輯電路較多,有的甚至使用專用的DSP芯片去處理視頻畫面的分割。雖然可以滿足對視頻圖像數據處理速度的要求,但是還需要外加CPU去協調系統工作,使得整個系統仍顯得體積較大,而且系統成本較高。隨著半導體加工工藝的不斷發展,FPGA在結構、速度、工藝、集成度和性能方面都取得了很大的進步和提高。本文將詳細介紹基于FPGA開發技術的視頻圖像畫面分割器的軟硬件設計與實現。

1 系統總體設計

本系統選用ALTEra公司的CycloneIII系列中的EP3C40F780C7型號FPGA作為核心處理芯片,提出和設計了一個多路視頻圖像數據的采集、處理、顯示,實現視頻圖像畫面分割器。

Cyclone III系列FPGA是Altera公司的低功耗、高性能和低成本的可編程邏輯器件,具有獨特的低功耗體系結構,以非常低的成本提供豐富的存儲器和專用乘法器資源。在視頻和圖像處理等高強度算法應用中,這些特性使該FPGA成為ASSP、ASIC以及分立數字信號處理器的理想替代方案。

1.1 硬件結構設計

整個系統主要由DVI接口電路、DVI信號解碼電路、FPGA及其配置電路、DDR2 SDRAM數據存儲電路及DVI信號編碼電路組成,系統結構框圖如圖1所示。

從圖1中可以看出,從DVI接口接收到DVI信號后通過解碼芯片SiI1161進行解碼,轉換成并行的數字信號,然后進入FPGA對四路視頻信號進行提取、存儲、合成等功能,進行處理后的數據通過編碼芯片SiI164再轉換為DVI視頻信號,就可以接到顯示器上顯示了。

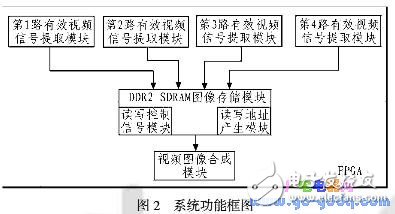

1.2 軟件結構設計

系統的軟件設計是系統功能實現的關鍵。在系統的硬件平臺的基礎上,通過對FPGA編程實現對視頻解碼芯片輸出的實時數字視頻數據接收,并根據畫面合成需要,對有效視頻圖像數據進行提取和存儲,然后將各路視頻數據合成一路輸出到顯示器。系統實現功能的系統框圖如圖2所示。

以下重點介紹一下視頻信號的提取和合成。

1.2.1 提取模塊設計

1)圖像提取原理

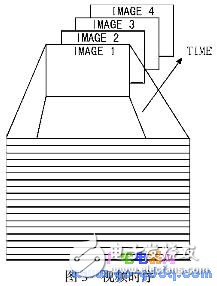

視頻畫面盡管看起來好像是連續運動的,其實那是一系列靜止的圖像,這些圖像切換得足夠快,使得畫面看起來像是連續運動的,如圖3所示。一種稱為場同步(vertical sync)的特定時序信息被用于指定新圖像從什么時候開始顯示;每張靜止圖像是由掃描線(sCAN?line)組成的,即沿著顯示器從上到下、一行接著一行進行顯示的數據線,另一種稱為行同步(horizontal sync)的時序信息用于指定新掃描線什么時候開始顯示。

行同步和場同步信息通常通過以下3種方式之一進行傳輸:

①單獨的行同步和場同步信號;

②單獨的復合同步信號;

③嵌入視頻信號的復合同步信號。

本系統采用的是數字視頻,采用的是技術①。

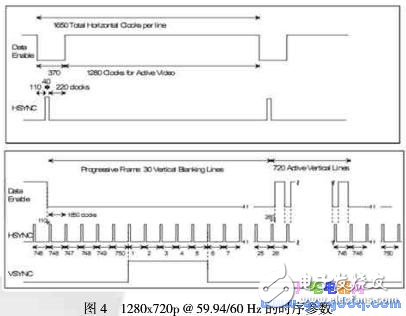

DV支持超過1 600×1 200的PC圖形分辨率和包括720p、1 080 i和1 080 p的HDTV分辨率,本設計采用的輸入分辨率為1 280×720/60?Hz,像素時鐘為74.25 MHz。DVI信號經SiI1161解碼后得到帶像素時鐘的24位并行R、G、B數字信號及H、V、DE信號,它們之間的相互關系如圖4所示。

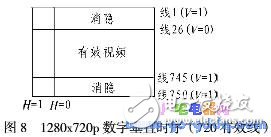

其中,當DE為1時,處理有效視頻,當DE為0時,處理HSYNC和VSYNC信號。SiI1161輸出的數字視頻信號一幀由750行視頻數據組成,每一場有效視頻行為720行,每一行又有1 650個像素,其中有效像素有1 280個,這些是在視頻圖像合成過程中要用到的數據,每一個像素都包含R、G、B 3種信號。

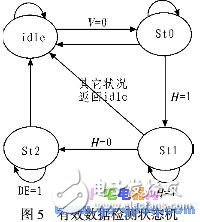

本設計根據H、V、DE信號對有效視頻數據進行定位,并根據圖像合成的需要把所需的有效視頻數據提取出來。在實現的過程中利用狀態機來判斷有效視頻數據,如圖5所示。

狀態機缺省狀態為idle狀態。先在idle狀態檢測場信號由高變低,進入有效數據行,再判斷H與DE的高低狀態,進而檢測到有效視頻數據,當H由高變低,DE為高的這段視頻數據則為有效視頻數據。這樣則可以根據視頻圖像合成的需要對視頻數據進行選擇提取。

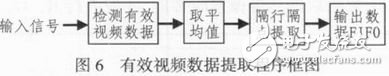

2)圖像提取模塊設計

基于上述有效視頻數據的提取原理可以提取任何一個數據行或任何一個象素,由于不同的圖像合成需要提取的有效視頻數是不同的。本設計為四畫面分割,需要對每一路輸入信號進行1/4壓縮,即需要對有效數據進行隔行隔點提取。有效視頻數據提取程序框圖如圖6所示。

由圖可知:接收到輸入信號后,根據視頻數據提取原理,檢測有效的視頻數據,每來一個時鐘,接收一個視頻數據存儲到RAM模塊中;然后對RAM模塊中存放的數據取平均值;接著對這些平均值隔行隔點提取,把提取出的數據送入異步FIFO中,方便讀寫入DDR2 SDRAM中。

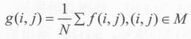

隔行隔點提取有效數據就是要將一些像素丟棄,本設計采用鄰域平均法來改善縮放后的視頻圖像質量。鄰域平均法的原理是將原圖中一個像素值和它周圍鄰近8個像素值相加,然后將求得的平均值(除以9)作為新圖中該像素的值。它采用模板計算的思想,模板操作實現了一種鄰域運算,即某個像素點的結果不僅與本像素有關,而且與其鄰域點的像素值有關。鄰域平均法的數學公式表達為:

其中f(i,j)為給定的圖像,經過鄰域平均處理后的圖像為g(i,j),M是所取鄰域中各鄰近像素的坐標N是鄰域中包含的鄰近像素的個數。

1.2.2 圖像合成和編碼模塊設計

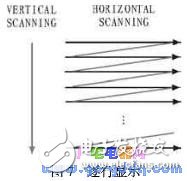

1)圖像合成原理

在像素域的多畫面合成中,首先,對原圖像按像素進行抽取,分別將多路圖像按照一定的比例縮小。然后,按照一定的規則將多路圖像進行排列,排列后的圖像即為多路合成的圖像。最后,將合成的圖像編碼輸出,即可在同一個屏幕顯示多個畫面,完成對多路圖像的合成。

合成后的視頻圖像是逐行顯示的,而對于將圖像以逐行方式“繪制”到屏幕上的設備,每張圖像都是從顯示器的左上角開始,一直向右移動,直到到達顯示器的右邊緣為止,然后向下掃描一行,重復地從左到右進行掃描,這個過程一直持續到整個屏幕全部被刷新一次為止,如圖7所示。

SiI1161輸出的完整的一幀圖像數據結構如圖8所示。

以四路為例,首先,要分別對原圖像進行1/4比例縮小。一幀視頻圖像有效顯示的圖像數據為26~745行,則在垂直方向上隔行抽取有效視頻行,使垂直方向縮小為原來的1/2。

在水平方向上,每行有效視頻由1 280個像素組成,每隔一個像素抽取一個有效視頻,使水平方向縮小為原來的1/2。這樣經過垂直和水平方向的抽取所得到的圖像縮小為原圖像的1/4。

然后,按照一幀圖像數據的排列格式對抽取的各路圖像的像素進行排列。抽取的第一路圖像的行與第二路圖像的行組成一整行,第三路圖像的行與第四路圖像的行組成一整行,四路圖像的行組成新的一幀圖像的圖像數據。

最后,將四路合成圖像數據經過SiI164編碼輸出,通過逐行掃描在一個顯示器上顯示四路圖像,即完成了四路視頻圖像合成。

2)圖像合成模塊設計

視頻圖像畫面合成的實現方法主要分為兩大類:像素域合成和壓縮域合成。基于系統的圖像數據為24位R、G、B數字視頻格式,所以在視頻圖像畫面合成中采用像素域內多畫面合成的方法。四路視頻圖像合成的實現過程如下:

首先,分別在垂直方向和水平方向上抽取有效的視頻數據,將四路圖像各縮小為原圖像的1/4。這部分功能由有效視頻數據提取模塊實現,該模塊在前面已經做過詳細介紹。然后將提取的各路圖像數據按找一定順序排列,即按照一定的規律存儲到DDR2 SDRAM中。各路圖像數據的地址按照上一節介紹的地址產生方法實現,都有各自固定的存儲空間。

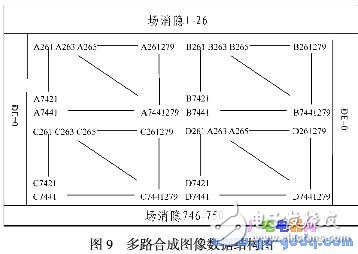

在完成各路視頻圖像的抽取,存儲后,就要對抽取的各路視頻圖像的進行四畫面合成。根據720P系統數字信號的數據格式,把有效視頻數據從存儲器中采用順序讀取出來,在相應的H、V、DE信號的位置,送視頻編碼輸出,完成四路視頻圖像的合成。在合成的過程中,H、V、DE信號及時鐘信號都由第一路輸入的視頻信號產生。四路視頻合成圖像的排列方式如圖9所示。

2 調試結果

經過軟硬件的綜合調試,整個視頻圖像畫面分割系統便可以正常工作了。

采集的多路視頻圖像經過FPGA圖像合成處理后,可以在一個顯示器顯示多路視頻圖像。

3 結束語

文中采用FPGA開發技術實現了視頻圖像畫面分割器的畫面分割的功能。研究的主要特色在于構建了以FPGA為核心器件的視頻畫面分割的硬件平臺,通過硬件形式來實現視頻四畫面分割,圖像的提取、存儲等都在一片FPGA內實現,提高了系統的集成度,所有的模塊設計都是利用Verilog HDL編程實現,和軟件實現方法相比,系統在處理速度方面有了顯著的提高。輸入/輸出的信號都為DVI信號,實現了高清視頻畫面分割。

電子發燒友App

電子發燒友App

評論