DCM主要功能

1. 分頻倍頻:DCM可以將輸入時(shí)鐘進(jìn)行Multiply或者Divide,從而得到新的輸出時(shí)鐘。

2. 去Skew:DCM還可以消除Clock的Skew,所謂Skew就是由于傳輸引起的同一時(shí)鐘到達(dá)不同地點(diǎn)的延遲差。

3. 相移:DCM還可以實(shí)現(xiàn)對輸入時(shí)鐘的相移輸出,這個(gè)相移一般是時(shí)鐘周期的一個(gè)分?jǐn)?shù)。

4. 全局時(shí)鐘:DCM和FPGA內(nèi)部的全局時(shí)鐘分配網(wǎng)絡(luò)緊密結(jié)合,因此性能優(yōu)異。

5. 電平轉(zhuǎn)換:通過DCM,可以輸出不同電平標(biāo)準(zhǔn)的時(shí)鐘。

DCM的特點(diǎn)與能力(Spartan-3系列為例)

數(shù)量:4 DCM / FPGA(也有例外)

-- 應(yīng)該夠用了

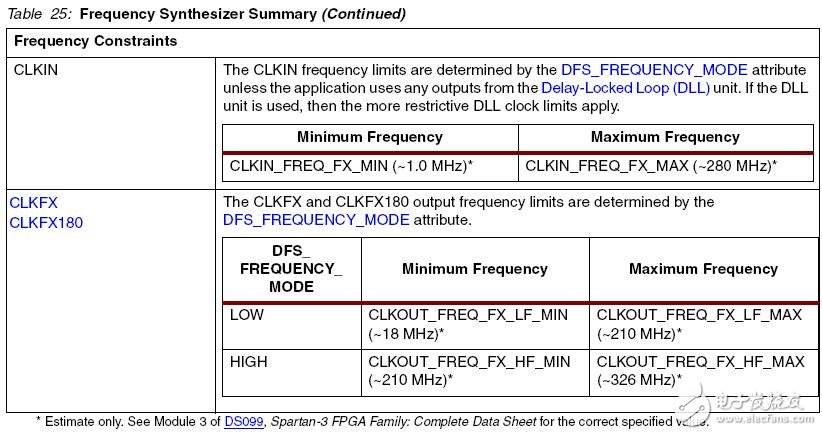

數(shù)字頻率綜合器輸入(CLKIN):1-280MHz

延遲鎖相環(huán)輸入(CLKIN):18-280MHz

時(shí)鐘輸入源(CLKIN):

Global Buffer Input Pad

Global Buffer Output

General-Purpose I/O (No Deskew)

Internal Logic (No Deskew)

-- 上面最后兩個(gè)分別是外部的普通IO口和內(nèi)部的邏輯,沒有Deskew,所以時(shí)鐘質(zhì)量不會(huì)很好。

頻率綜合器輸出(CLKFX、CLKFX180):是CLKIN的M/D倍,其中

M=2..32

D=1..32

-- 這樣看來最大能倍頻32倍,最小能16分頻。

時(shí)鐘Dividor輸出(CLKDV):是CLKIN的下列分頻

1.5, 2, 2.5, 3, 3.5, 4, 4.5, 5, 5.5, 6, 6.5, 7, 7.5, 8, 9, 10, 11, 12, 13, 14, 15, Or 16

-- 發(fā)現(xiàn)沒有,最大的分頻也是16。不過能支持半分頻,比用頻率綜合器方便。

倍頻輸出(CLK2X、CLK2X180):CLKIN的2倍頻

時(shí)鐘Conditioning、占空比調(diào)整:這個(gè)對所有時(shí)鐘輸出都施加,占空比為50%。

1/4周期相移輸出(CLK0/90/180/270):是CLKIN的1/4周期相移輸出。

半周期相移輸出(CLK0/180、CLK2X/180、CLKFX/180):相差為180度的成對時(shí)鐘輸出。

相移精度:最高精度為時(shí)鐘周期的1/256。

時(shí)鐘輸出:9個(gè)

到全局時(shí)鐘網(wǎng)的時(shí)鐘輸出:最多9個(gè)中的4個(gè)

到General Purpose互聯(lián):最多9個(gè)

到輸出腳:最多9個(gè)

-- 可見9個(gè)時(shí)鐘輸出可以隨意鏈接內(nèi)部信號(hào)或者外部輸出,但是進(jìn)入全局時(shí)鐘網(wǎng)的路徑最多只有4個(gè)。

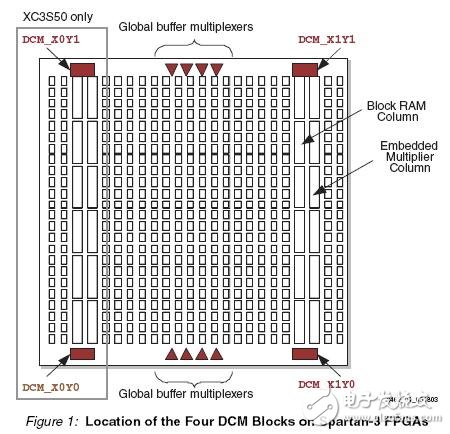

DCM的位置在哪?

我們以Spartan3系列為例。

FPGA看上去就是一個(gè)四方形。最邊緣是IO Pad了。除去IO Pad,內(nèi)部還是一個(gè)四方形。四個(gè)角上各趴著一個(gè)DCM。上邊緣和下邊緣中間則各趴著一個(gè)全局Buffer的MUX。這樣的好處是四個(gè)DCM的輸出可以直接連接到全局Buffer的入口。

下面是手繪簡圖,很丑是吧,呵呵。

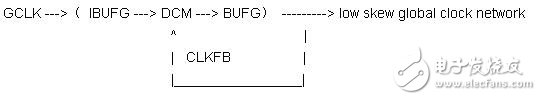

DCM是全局時(shí)鐘網(wǎng)絡(luò)可選的一部分

一般,時(shí)鐘通過一個(gè)“全局輸入Buffer”和“全局時(shí)鐘Buffer” 進(jìn)入全局時(shí)鐘網(wǎng)絡(luò)。如下所示

GCLK ---》( IBUFG ---》 BUFG) ---》 Low Skew Global Clock Network

在需要的時(shí)候,DCM也成為全局時(shí)鐘網(wǎng)絡(luò)的一環(huán)。

DCM 內(nèi)部構(gòu)成一覽

1. DLL 延遲鎖定環(huán)

說是延遲鎖定環(huán),但是我覺得叫做延遲補(bǔ)償環(huán)更加貼切。因?yàn)镈LL的主要功能是消除輸入時(shí)鐘和輸出時(shí)鐘之間的延遲,使得輸入輸出在外部看來是透明連接。

實(shí)現(xiàn)這種功能的原理是:DLL通過輸出時(shí)鐘CLK0或者CLK2X觀察實(shí)際的線路延遲,然后在內(nèi)部進(jìn)行補(bǔ)償。

一句話,DLL的核心功能是無延遲。

DLL的輸出是CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, 和 CLKDV。

2. DFS 數(shù)字頻率綜合

DFS的主要功能是利用CLKIN合成新的頻率。

合成的參數(shù)是:M(Multiplier)和 D(Divisor)。通過MD的組合實(shí)現(xiàn)各種倍頻和分頻。

如果不使用DLL,則DFS的合成頻率和CLKIN就不具有相位關(guān)系,因?yàn)闆]有延遲補(bǔ)償,相位就不再同步。

3. PS 相位偏移

注意這個(gè)相位偏移不是DLL中輸出CLK90/180/270用的。這個(gè)PS可以令DCM的所有9個(gè)輸出信號(hào)都進(jìn)行相位的偏移。偏移的單位是CLKIN的一個(gè)分?jǐn)?shù)。

也可以在運(yùn)行中進(jìn)行動(dòng)態(tài)偏移調(diào)整,調(diào)整的單位是時(shí)鐘的1/256。

這個(gè)功能我們平時(shí)不常用。

4. 狀態(tài)邏輯

這個(gè)部分由 LOCKED 信號(hào)和 STATUS[2:0] 構(gòu)成。LOCKED信號(hào)指示輸出是否和CLKIN同步(同相)。STATUS則指示DLL和PS的狀態(tài)。

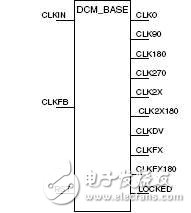

DCM_BASE

DCM_BASE是基本數(shù)字時(shí)鐘管理模塊的縮寫,是相位和頻率可配置的數(shù)字鎖相環(huán)電路,常用于FPGA系統(tǒng)中復(fù)雜的時(shí)鐘管理。如果需要頻率和相位動(dòng)態(tài)重配置,則可以選用DCM_ADV原語;如果需要相位動(dòng)態(tài)偏移,可使用DCM_PS原語。DCM系列原語的RTL結(jié)構(gòu)如圖3-8所示。

模塊接口信號(hào)的說明如表3-8所列。

DCM_BASE組件可以通過Xilinx的IP Wizard向?qū)Мa(chǎn)生,也可以直接通過下面的例化代碼直接使用。其Verilog的例化代碼模板為:

// DCM_BASE: 基本數(shù)字時(shí)鐘管理電路(Base Digital Clock Manager Circuit)

// 適用芯片:Virtex-4/5

// Xilinx HDL庫向?qū)О姹荆琁SE 9.1

DCM_BASE #(

.CLKDV_DIVIDE(2.0),

// CLKDV分頻比可以設(shè)置為: 1.5,2.0,2.5,3.0,3.5,4.0,4.5,5.0,5.5,6.0,6.5

// 7.0,7.5,8.0,9.0,10.0,11.0,12.0,13.0,14.0,15.0 Or 16.0

.CLKFX_DIVIDE(1), // Can Be Any Integer From 1 To 32

// CLKFX信號(hào)的分頻比,可為1到32之間的任意整數(shù)

.CLKFX_MULTIPLY(4),

// CLKFX信號(hào)的倍頻比,可為2到32之間的任意整數(shù)

.CLKIN_DIVIDE_BY_2(“FALSE”),

// 輸入信號(hào)2分頻的使能信號(hào),可設(shè)置為TRUE/FALSE

.CLKIN_PERIOD(10.0),

// 指定輸入時(shí)鐘的周期,單位為Ns,數(shù)值范圍為1.25~1000.00。

.CLKOUT_PHASE_SHIFT(“NONE”),

// 指定移相模式,可設(shè)置為NONE或FIXED

.CLK_FEEDBACK(“1X”),

// 指定反饋時(shí)鐘的頻率,可設(shè)置為NONE、1X或2X。相應(yīng)的頻率關(guān)系都是針對CLK0而言的。

.DCM_PERFORMANCE_MODE(“MAX_SPEED”),

// DCM模塊性能模式,可設(shè)置為 MAX_SPEED 或 MAX_RANGE

.DESKEW_ADJUST(“SYSTEM_SYNCHRONOUS”),

// 抖動(dòng)調(diào)整,可設(shè)置為源同步、系統(tǒng)同步或0~15之間的任意整數(shù)

.DFS_FREQUENCY_MODE(“LOW”),

// 數(shù)字頻率合成模式,可設(shè)置為LOW或HIGH 兩種頻率模式

.DLL_FREQUENCY_MODE(“LOW”),

// DLL的頻率模式,可設(shè)置為LOW、HIGH或HIGH_SER

.DUTY_CYCLE_CORRECTION(“TRUE”),

// 設(shè)置是否采用雙周期校正,可設(shè)為TRUE或FALSE

.FACTORY_JF(16‘’Hf0f0),

// 16比特的JF因子參數(shù)

.PHASE_SHIFT(0),

// 固定相移的數(shù)值,可設(shè)置為 -255 ~ 1023之間的任意整數(shù)

.STARTUP_WAIT(“FALSE”)

// 等DCM鎖相后再延遲配置DONE管腳,可設(shè)置為TRUE/FALSE

) DCM_BASE_inst (

.CLK0(CLK0), // 0度移相的DCM時(shí)鐘輸出

.CLK180(CLK180), // 180度移相的DCM時(shí)鐘輸出

.CLK270(CLK270), // 270度移相的DCM時(shí)鐘輸出

.CLK2X(CLK2X), // DCM模塊的2倍頻輸出

.CLK2X180(CLK2X180), // 經(jīng)過180度相移的DCM模塊2倍頻輸出

.CLK90(CLK90), // 90度移相的DCM時(shí)鐘輸出

.CLKDV(CLKDV), // DCM模塊的分頻輸出,分頻比為CLKDV_DIVIDE

.CLKFX(CLKFX), // DCM合成時(shí)鐘輸出,分頻比為(M/D)

.CLKFX180(CLKFX180), // 180度移相的DCM合成時(shí)鐘輸出

.LOCKED(LOCKED), // DCM鎖相狀態(tài)輸出信號(hào)

.CLKFB(CLKFB), // DCM模塊的反饋時(shí)鐘信號(hào)

.CLKIN(CLKIN), // DCM模塊的時(shí)鐘輸入信號(hào)

.RST(RST) // DCM 模塊的異步復(fù)位信號(hào)

);

// 結(jié)束DCM_BASE模塊的例化過程

在綜合結(jié)果分析時(shí),DCM系列原語的RTL結(jié)構(gòu)如圖3-36所示。

圖3-36 DCM模塊的RTL級結(jié)構(gòu)示意圖

Spartan-3 DCM的兼容性

S3 的DCM和 Virtex-II 以及Pro的DCM 功能基本相同。但是S3 DCM的技術(shù)屬于3代技術(shù),因此在抗噪性能、相移能力方面有進(jìn)一步提高。(客觀的說,對我們的普通應(yīng)用,不是特別重要。)

但是和Spartan-2系列相比,有很大改進(jìn)。S2系列不叫DCM叫DLL,可見DFS和PS等功能完全是新加入的,所以S2系列其實(shí)除了二倍頻幾乎沒有倍頻和分頻能力。從這點(diǎn)來講,S3真的是用起來很爽了。

DCM 輸入時(shí)鐘的限制

和所有物理器件一樣,DCM的工作范圍也是受限的。由于DLL和DFS的要求各不相同,因此DCM的輸入頻率的限制也視乎是否同時(shí)使用DLL和DFS還是單獨(dú)使用其中之一。如果同時(shí)使用,則取限制較嚴(yán)格者作為整個(gè)DCM系統(tǒng)的限制。我們來看兩者的獨(dú)立限制。

呵呵,這部分內(nèi)容不用記哦,需要的時(shí)候查一下軟件或者手冊就可以了。只要明白“CLKIN輸入頻率有限制,而且DLL、DFS同時(shí)使用時(shí)取其嚴(yán)格者” 這些道理就可以了。

除了時(shí)鐘限制之外,對于時(shí)鐘的質(zhì)量也有一定限制,主要有3個(gè):

1. CLKIN Cycle-To-Cycle Jitter:約束了前后兩個(gè)CLKIN周期的差異;

2. CLKIN Period Jitter:約束了100萬個(gè)Cycle中最大周期和最小周期之間的差異;

3. CLKFB Path Delay Variation:約束了從外部進(jìn)來的反饋回路的延遲波動(dòng),這種延遲波動(dòng)在概念上其實(shí)和Jitter如出一轍。

具體數(shù)值請查手冊,知道有這么回事就可以了。

LOCKED信號(hào)的行為方式

LOCKED信號(hào)用于指示整個(gè)DCM系統(tǒng)已經(jīng)和CLKIN同步,從LOCKED信號(hào)有效開始,輸出時(shí)鐘才可以使用,在此之前,輸出時(shí)鐘可能會(huì)處于各種復(fù)雜的不穩(wěn)定狀態(tài)。我們來看一下LOCKED信號(hào)的行為狀態(tài)機(jī)。

FPGA配置:

If (CLKIN已經(jīng)穩(wěn)定) Next_state = 判斷同步;

Else Next_state = RST_DCM;

判斷同步:

If (已經(jīng)同步) Next_state = 判斷同步;

Else Next_state = 同步失敗;

同步失敗: Next_state = RST_DCM;

RST_DCM: Next_state = FPGA配置;

現(xiàn)在來看看各個(gè)狀態(tài)下的輸出。

Case (State)

FPGA配置: LOCKED = 0;

判斷同步: LOCKED = 1;

同步失敗: LOCKED = 0;

RST_DCM:LOCKED = 0;

Endcase

RST 信號(hào)——重啟鎖定

RST信號(hào)用于在時(shí)鐘不穩(wěn)定或者失去鎖定時(shí),將DCM的相關(guān)功能重置,從而重新啟動(dòng)鎖定追蹤。

作為一個(gè)輸入信號(hào),RST無法被DCM自身置位,因此需要我們的應(yīng)用設(shè)計(jì)來控制這個(gè)RST信號(hào),否則需將其接地。

置位RST會(huì)將延遲Tap的位置置0,因此可能會(huì)產(chǎn)生Glitch或者是Duty Cycle 發(fā)生變化,另外相位偏移也會(huì)重置回到默認(rèn)值。

DCM 生成向?qū)?/h2>

安裝了ISE就能得到一系列Accessories。利用其中的Architecture Wizard 我們可以生成DCM模塊。生成的DCM將產(chǎn)生3種輸出:

1. 一個(gè)例化了DCM的邏輯綜合文件(采用生產(chǎn)商特定格式的VHDL / Verilog)

2. 一個(gè)UCF文件控制特定實(shí)現(xiàn)

3. 所有其他用戶設(shè)置都保存到XAW(Xilinx Architecture Wizard)文件中。

接下來描述一下向?qū)褂貌襟E。

1. 從ISE或者Arch Wizard中啟動(dòng)界面;

2. 第一個(gè)頁面做基本配置:路徑、XAW文件名、VHDL / Verilog選擇、綜合工具、FPGA型號(hào);

3. 進(jìn)行General Setup,一看就明白,不細(xì)說,注意一下幾點(diǎn):

- CLKIN Source 如果選 External 則 DCM 的 CLKIN 會(huì)自動(dòng)連接到 IBUFG。

- Feedback如果選 Internal 則反饋來自 BUFG。

4. 高級設(shè)置

- 選擇FPGA的配置過程是否包含DCM的鎖定,如果是,則配置完成信號(hào)DONE將在LOCKED信號(hào)有效后方能有效。

- 選擇CLKIN是否要除2。由于DCM的輸入頻率有限,對于過高的輸入時(shí)鐘通過除2使之可用。

- Deskew調(diào)整,這個(gè)選項(xiàng)建議在咨詢Xilinx工程師后再使用。

5. 時(shí)鐘輸出口 Buffer 設(shè)置

- 默認(rèn)情況下所有輸出口都鏈接 BUFG 全局時(shí)鐘網(wǎng)絡(luò)入口

- 由于全局時(shí)鐘網(wǎng)絡(luò)的入口有限,用戶可以定制時(shí)鐘輸出口連接到其他類型的Buffer

- Global Buffer:進(jìn)入全局時(shí)鐘網(wǎng)絡(luò)的入口Buffer,共有4個(gè),簡稱BUFG

- Enabled Buffer:還是上面的4個(gè)全局時(shí)鐘Buffer,但是配置為有使能信號(hào)控制,簡稱BUFGCE

- Clock MUX:還是上面的4個(gè)全局時(shí)鐘Buffer,但是配置為 2-To-1 MUX類型,由S信號(hào)控制選出,簡稱BUFGMUX

- Low Skew Line:沒有Buffer了,只能使用 Skew 比較小的連線

- Local Routing:連到本地,Skew的要求不是很嚴(yán)格

- None:禁止輸出

- 對于Enabled Buffer類型和Clock Mux類型,需要指定En口的名字

- 需要為輸出時(shí)鐘信號(hào)指定名字或者使用默認(rèn)

6. 設(shè)置DFS

- 設(shè)置目標(biāo)輸出頻率,然后按Calculate,自動(dòng)生成 M/D 值和 Jitter 值

- 或者手動(dòng)設(shè)置 M/D 值,然后按Calculate,自動(dòng)生成頻率和 Jitter 值

7. 最后輸出所需的3種文件。

電子發(fā)燒友App

電子發(fā)燒友App

評論