隨著現代通信技術的發展,各種多址技術在日常生活中的應用正變得越來越廣泛。所謂多址技術,是指許多用戶同時使用同一頻譜,采用不同的處理技術,使不同用戶信號之間互不干擾地被分別接收和解調。多址技術分為頻分多址(FDMA)、碼分多址(CDMA)、時分多址(TDM-A)。頻分多址是以不同的頻率信道實現通信,碼分多址是以不同的代碼序列實現通信,而時分多址是以不同的時隙實現通信,它是一種實現共享傳輸介質或網絡的通行技術。

時分多址技術把時間分割成周期性的幀,每一幀再分割成若干個時隙,通過介質或者網絡發送信號。在滿足定時和同步的條件下,接收方可以分別在各個時隙中接收到對應的信號而不混擾。時分多址技術具有保密性較高,傳輸容量較大等特點。

目前,利用FPGA實現多路信號的時分多址幀格式來進行傳輸的方法眾多,但大多數方法都是通過使用FPGA芯片大量的門電路構成寄存器來實現時分多址。該類方法將占用大量的FIGA資源,導致單片FPGA可實現的功能大大減少,提高了工程成本,甚至對于一些資源較少的FPGA芯片,該類方法無法實現時分多址傳輸。本文提出了一種基于IP核的方法來實現時分多址,利用芯片內部的Block SelectRAMResource(BRAM)存儲數據,節約了大量的邏輯門資源,使單片FPGA芯片能完成更多的邏輯功能。

1 理論分析

1.1 IP核

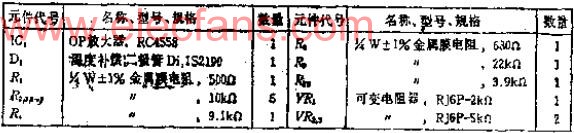

IP核(Intellectual Property core)是一段具有特定電路功能的硬件描述語言程序,該程序與集成電路的工藝無關,可以移植到不同的半導體工藝中去生產基礎電路芯片。利用IP核設計電子系統,引用方便,修改基本元件的功能容易。IP核模塊有行為(Behavior)、結構(Str-ucture)和物理(Physical)3級不同程度的設計,對應描述功能行為的不同分為3類,即軟核、完成結構描述的固核和基于描述并經過工藝驗證的硬核。

1.2 BRAM(Block SeleetRAM Resource)

FPGA內部的資源種類比較復雜,主要包括了以下幾個部分:輸入/輸出模塊(Input/Output Blocks,IOB)、可配置邏輯單元(Configur-able Logic Blocks,CLB)、Block SelectRAM、乘法器、數字時鐘管理單元(DCM)、布線資源(Routing Resources)等。本文提出的算法正是利用芯片內部集成的Block SelectRAM實現時分多址方式的傳輸,從而節約出大量的CLB.以便單片FPGA能完成更多的功能。

FPGA芯片內部集成的每一塊BRAM都是物理上的雙口隨機訪問存儲器(雙口RAM),它有兩套完全獨立的數據線,地址線和讀寫控制線,并允許兩個獨立的系統同時對該存儲器進行隨機性的訪問,即共享式多端口存儲器。

雙口RAM最大的特點是存儲數據共享。一個存儲器配備兩套獨立的地址,數據和控制線,允許兩個獨立控制器同時異步的訪問存儲單元。因為數據共享,就必須存在訪問仲裁控制。內部仲裁邏輯控制提供以下功能:對同一地址單元訪問的時序控制;存儲單元數據塊的訪問權限分配;信令交換邏輯等。

BRAM的工作類似于寄存器的工作方式,控制信號、地址信號以及輸入輸出數據信號必須要在時鐘沿的建立時間內保持有效,BRAM會在這個時鐘周期進行讀寫操作來輸出結果或寫入數據。其讀寫方式分為3種,分別是對地址進行讀和寫、只讀、只寫。

1.3 算法實現

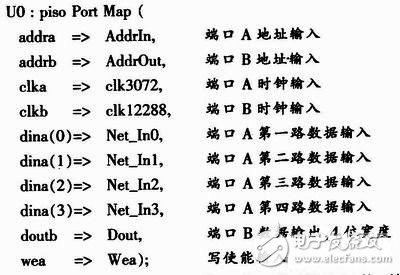

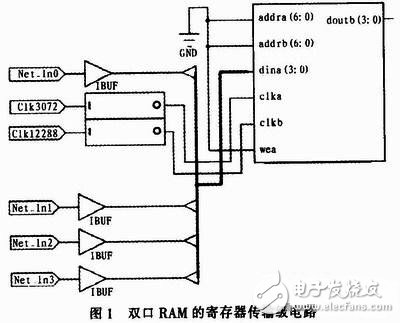

第1步,例化雙口RAM的IP核,將程序的輸入輸出與雙口RAM的輸入輸出進行映射。

第2步,通過雙口RAM的第一套端口將輸入信號存儲到RAM中,通過雙口RAM的第二套端口將存儲到RAM中的數據讀出。

以4路信號為例,假設每路輸入信號的采樣率是48 kHz,采樣位數是64 bit,則每路輸入信號的位時鐘是3.072 MHz,在第一個48 kHz的采樣周期內,當采到3.072 MHz位時鐘的下降沿時,將輸入地址遞增1。則在接下來的位時鐘的上升沿,根據所例化的雙口RAM的IP核,4路輸入數據將存儲到雙口RAM當前輸入地址所對應的存儲器地址中,等待讀取。由于共有4路信號,即輸入信號寬度為4位,則存儲到雙口RAM中的數據寬度也應為4位,其中,每個地址中的所存儲數據的第一位對應第一路輸入信號,第二位對應第二路輸入信號,以此類推。此時需要的雙口RAM的大小位64x4 bit。

在下一個48 kHz的周期內,與前面類似,將4位寬度的輸入數據繼續存儲到雙口RAM新的64個4位的存儲空間,同時,應將上個48 kHz周期所存儲的前64個4位數據讀出,并且準備以時分多址的格式傳輸出去。

第3步,將從第二套端口讀出的數據以時分多址的幀格式傳輸出去。

要想4路輸入信號以時分多址的格式傳輸,應該將48 kHz時間周期劃分為4個時間周期,在劃分的每一個時間周期內,讀取一遍雙口RAM中存儲的數據。首先,應在劃分的第一個時間周期內把讀出的64個4位數據的第一位送給時分多址的輸出,然后回到起始地址,在劃分的第二個時間周期內再重新讀出一次64個4位數據,把數據的第二位送給時分多址的輸出,以此類推,直到4路數據全部輸出。由于在一個48 kHz周期內要重復讀取雙口RAM中的數據4次,所以此時位時鐘的頻率要提高到原來的4倍,因此,讀取數據的位時鐘頻率應該為12.288 MHz。

在接下來的一個48 kHz周期內,將雙口RAM中后64個4位存儲空間內的數據以與上面相同的方式發送出去,同時,由于前64個4位的存儲空間的數據已經發送完成,不再需要保存,則新輸入的數據可被存儲到前64個4位的存儲空間,以此類推,前64個4位存儲空間與后64個存儲空間交替存儲輸入數據,并交替將存儲的數據發送出去。

由此可以看到,所需要雙口RAM的大小應為2x64×4bit,在A端口對數據寫入,在B端口對數據進行讀出。

2 FPGA的實現

實驗所采用的FPGA是XILINX公司的SPARTAN 3E系列中的XC3SS00E芯片,該芯片的封裝是PQ208,芯片速度為-5,采用的程序開發語言是VHDL,綜合工具為XILINX公司的ISE 10.1,仿真工具采用的是ModelSim se 6.2。

與理論算法對應,硬件實現的VHDL程序包括了以下幾個模塊。

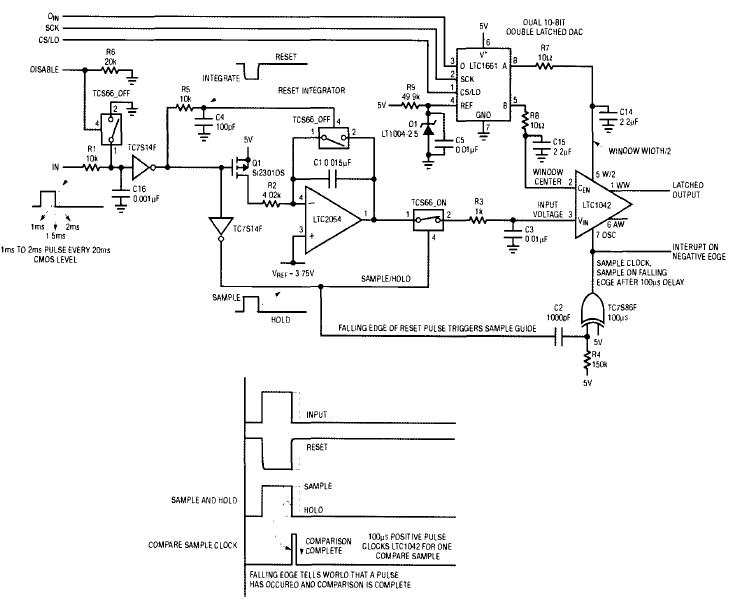

使用芯片內部的雙口RAM的IP核,通過例化IP核,利用一個雙口RAM有兩套讀寫地址,將程序的輸入輸出與雙口RAM的輸入輸出進行映射,則內部電路將程序的輸入輸出連接到了雙口RAM的輸入輸出上。對程序的輸入輸出腳的操作相當于對雙口RAM進行操作。圖1是雙口RAM的VHDL代碼在Xilinx ISE中綜合后的寄存器傳輸級電路圖。

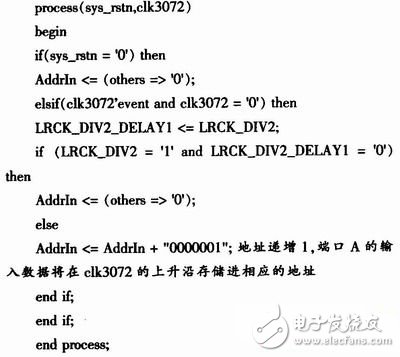

在端口A輸入時鐘clk3072的每個下降沿,端口A輸入地址AddrIn都遞增1,則在elk3072的上升沿,根據例化的雙口RAM的IP核,端口A的四路輸入數據將存儲進相應的地址空間中。

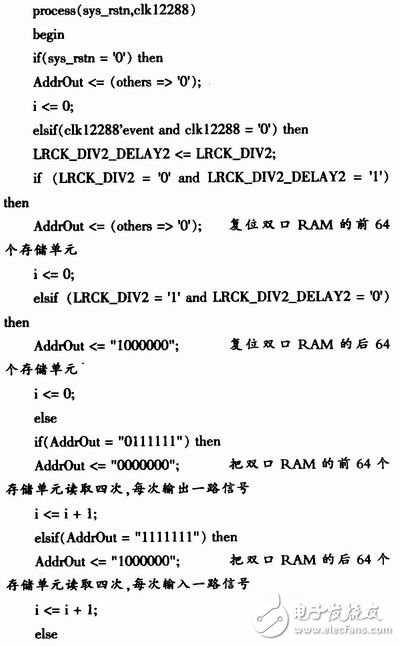

在端口B輸入時鐘elk12288的每個下降沿,端口B輸入地址AddrOut都遞增1,則在elk12288的上升沿,根據例化的雙口RAM的IP核,相應的地址空間中的數據將通過Dout被讀出來。

依次將輸出數據以時分多址的幀格式傳輸出去。

3 仿真結果

用ModelSim se 6.2b對程序進行仿真,在48 kHz的時鐘周期內,給第1路輸入源的64位輸入信號為0x1111111111111111,第2路輸入源的64位輸入信號為0x2222222222222222,第3路輸入源的64位輸入信號為0x3333333333333333,第4路輸入源的64位輸入信號為0x4444444444 444444。仿真結果如圖2所示。

由仿真圖可以看出,在一個48 kHz的時鐘周期內,TDMA_OUT,即時分多址幀格式的輸出為0x11111111111111112222222222222222333333 33333333334444444444444444,即每一幀被分成了4個時隙,4路輸入信號在每一幀中占用各自的時隙進行傳輸,通過該仿真結果,可以驗證該方法的可用性。

將VHDL語言程序通過ISE10.1綜合,布局布線后,通過JTAG線纜下載到XC3S500E中進行電路板上的測試,再次驗證了該方法的正確。

通過ISE綜合后,可以看到程序所占用的芯片資源如下表所示。

從表中的數據可以看出,通過使用一個BRAM從而節約了大量的資源,FPGA芯片資源的重要指標Slices僅僅占用了15個,LUTs僅僅用了29個,可見,該方法所占用的FPGA資源極少,達到了設計目標。

4 結論

本文研究了FPGA實現時分多址的一種改進型的方法,通過使用FPGA芯片內部的雙口RAM,利用IP核,實現了多路信號轉換成時分多址幀格式信號進行傳輸,根據所占資源的統計數據,可以看到在完成相同功能的前提下,該方法相比于已有的方法,確實能大量節省FPGA芯片的邏輯資源,從而使單片FPGA能完成更多的邏輯功能。但是,此方法會占用一部分雙口RAM,在雙口RAM資源緊張的時候不是太適用。

用ModelSim SE 6.2b對FPGA程序進行了仿真,并且將程序下載到電路板上進行了驗證,證實了該方法的可用性。

電子發燒友App

電子發燒友App

評論