完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > hdl

文章:184個 瀏覽:47469次 帖子:125個

使用Verilog/SystemVerilog硬件描述語言 (HDL) 練習數(shù)字硬件設計

給出了一個可以做16bit加法的模塊add16,實例化兩個add16以達到32bit加法的。

Verilog HDL提供了兩種類型的顯式時序控制:一種是延遲控制,即定義執(zhí)行語句的延遲時間;另一種是事件控制,只有當某一事件發(fā)生時才允許該語句繼續(xù)向下...

在我國使用Verilog HDL的公司比使用VHDL的公司多。從EDA技術的發(fā)展上看,已出現(xiàn)用于CPLD/FPGA設計的硬件C語言編譯軟件,雖然還不成熟...

HDL攜帶新一代燈光控制產(chǎn)品如期參展GETShow

一年一度的廣州(國際)演藝設備、智能聲光產(chǎn)品技術展覽會(以下簡稱GET Show)5月8日在廣州保利世貿(mào)博覽館正式開幕。作為GET Show的“老朋友”...

此類問題是FPGA設計實現(xiàn)中比較棘手的問題,Xilinx針對7系列及以后的UltraScale/UltraScale+等,提出了UltraFast設計方...

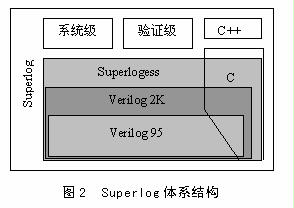

摘要:從數(shù)字系統(tǒng)設計的性質(zhì)出發(fā),結(jié)合目前迅速發(fā)展的芯片系統(tǒng),比較、研究各種硬件描述語言;詳細闡述各種語言的發(fā)展歷史、體系結(jié)構和設計方法;探討未來

2009-06-20 標簽:HDL 1638 0

基于Zynq RFSoC的數(shù)字基帶驗證毫米波 RF 電子器件

作者:Matthew Weiner,RF Pixels 新興的 5G 網(wǎng)絡依托毫米波頻譜運行,這意味著 5G 網(wǎng)絡的性能優(yōu)于 4G 網(wǎng)絡,能夠以更高的速...

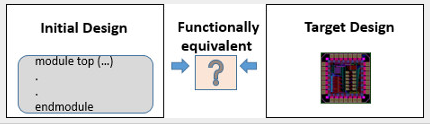

16nm技術的形式驗證流程、優(yōu)勢和調(diào)試

必須優(yōu)化正式驗證流程中的初始網(wǎng)表,因此測試設計需要額外的邏輯。在這里,我們提供16 nm節(jié)點的形式驗證流程和調(diào)試技術。

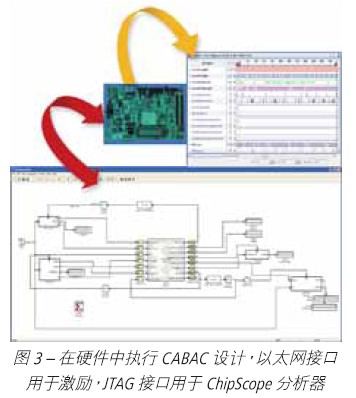

HDL設計和驗證與System Generator相結(jié)合

HDL設計和驗證與System Generator相結(jié)合 Xilinx®SystemGeneratoRForDSP是用來協(xié)助系統(tǒng)設計的MATL...

基于Verilog HDL設計的自動數(shù)據(jù)采集系統(tǒng)

摘要: 介紹了一種采用硬件控制的自動數(shù)據(jù)采集系統(tǒng)的設計方法,包括數(shù)字系統(tǒng)自頂向下的設計思路、Verilog HDL對系統(tǒng)硬件的描述和狀態(tài)機的設計以及MA...

鑫偉萬豪酒店采用HDL智能解決方案實現(xiàn)了酒店公共區(qū)域智慧照明

南寧鑫偉萬豪酒店坐落于廣西南寧市東部城區(qū)繁華市中心,這是萬豪集團在中國大陸開設的第34家酒店,也是南寧市目前唯一的五星級國際管理品牌酒店。

從圖1 FPGA開發(fā)流程中的主干線上分離出第一步設計輸入橫向環(huán)節(jié),并做了進一步的細節(jié)的處理,如圖2,從圖上看到,設計輸入方式有三種形式,有IP核、原理圖...

反之,如果一個設計的時序要求很高,普通方法達不到設計頻率,那么可以通過數(shù)據(jù)流串并轉(zhuǎn)換,并行復制多個操作模塊,對整個設計采用“乒乓操作”和“串并轉(zhuǎn)換”的思...

換一批

換一批

編輯推薦廠商產(chǎn)品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術 | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |