本內(nèi)容詳細(xì)介紹了SPI,UART,I2C區(qū)別與特點(diǎn),SPI:高速同步串行口。3~4線接口,收發(fā)獨(dú)立、可同步進(jìn)行,UART:通用異步串行口。按照標(biāo)準(zhǔn)波特率完成雙向通訊,速度慢

2012-02-02 16:15:27 6395

6395 本文旨在研究基于FPGA技術(shù)對嵌入式SoC系統(tǒng)進(jìn)行在線監(jiān)控的方法。設(shè)計了一個FPGA片上通信系統(tǒng),該系統(tǒng)內(nèi)部固化基于UART接口的Modbus通訊協(xié)議棧,可通過串口與PC上位機(jī)進(jìn)行通信。##Modbus協(xié)議棧模塊的設(shè)計與實(shí)現(xiàn)

2014-07-22 12:56:45 2360

2360 (如FIF0),在實(shí)際應(yīng)用中,往往只需要用到UART的幾個基本功能,使用專用芯片會造成資源浪費(fèi)和成本提高,我們可以將所需要的UART功能集成到FPGA內(nèi)部,從而簡化了整個系統(tǒng)電路,提高了可靠性、穩(wěn)定性和靈活性。

2020-08-04 17:25:00 743

743

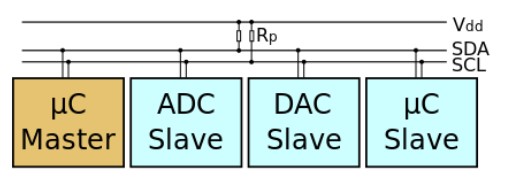

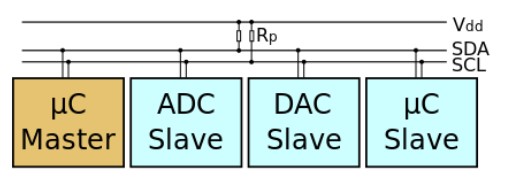

組件之間的通訊。由于其簡單性,它被廣泛用于微控制器與傳感器陣列,顯示器,IoT設(shè)備,EEPROM等之間的通信。 結(jié)合了SPI和UART的最佳功能。使用 ,您可以將多個從機(jī)連接到單個主機(jī)(類似 SPI

2023-05-22 09:43:48 559

559

。SPI協(xié)議比UART顯著更快。UART是一種提供全雙工串行通信的通用協(xié)議如果您使用嵌入式系統(tǒng),那么了解所使用的各種技術(shù)和通信協(xié)議是很重要的。通信協(xié)議使系統(tǒng)中所連接的

2023-08-26 08:14:40 1902

1902

串口作為常用的三大低速總線(UART、SPI、IIC)之一,在設(shè)計眾多通信接口和調(diào)試時占有重要地位。

2024-01-03 11:43:52 762

762

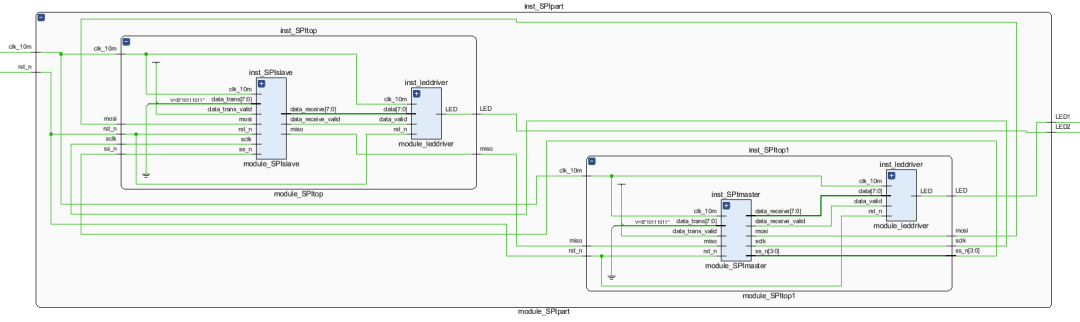

寫在前面SPI協(xié)議系列文章:FPGA實(shí)現(xiàn)的SPI協(xié)議(一)----SPI驅(qū)動 在上篇文章,簡要介紹了SPI協(xié)議,編寫了SPI協(xié)議的FPGA驅(qū)動,但是在驗證環(huán)節(jié),僅僅驗證了發(fā)送時序,而沒有與從機(jī)進(jìn)行

2022-02-17 06:03:44

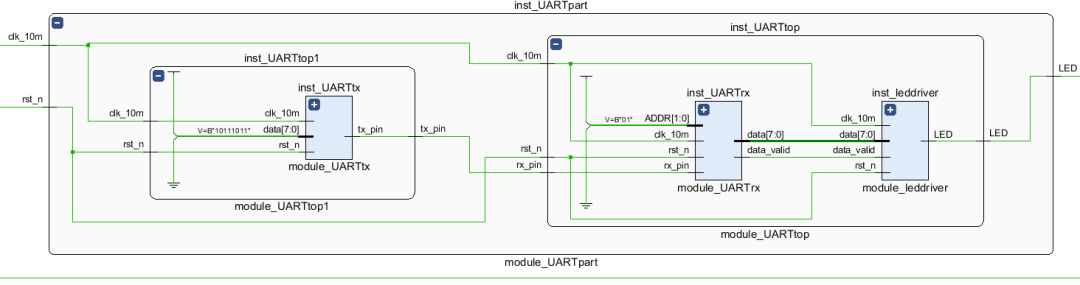

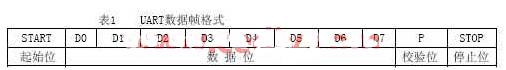

`UART 主要由 UART 內(nèi)核、信號監(jiān)測器、移位寄存器、波特率發(fā)生器、計數(shù)器、總線選擇器和奇偶校驗器總共 7 個模塊組成,如圖 5-5 所示。圖 5-5 UART 實(shí)現(xiàn)原理圖UART 各個模塊

2018-10-18 09:51:47

fpga通過spi通信協(xié)議在與外圍設(shè)備實(shí)現(xiàn)通信的過程中程序代碼該怎么寫?新手勿噴

2014-04-09 12:44:34

spi接口和uart接口區(qū)別,一、SPII2C UART通信速率比較:SPI > I2C > UART1、同步通信>異步通信;2、同步通信時必須有一根時鐘線連接傳輸?shù)膬啥?3、都是

2021-07-21 06:24:58

spi,uart,iic協(xié)議之間的對比:spi和uart的區(qū)別,spi結(jié)構(gòu)上可以實(shí)現(xiàn)一主多從進(jìn)行通信,依靠時鐘進(jìn)行傳輸數(shù)據(jù)的同步傳輸模式。SPI和iic都是一主多從進(jìn)行通信的,同樣需要依靠時鐘完成

2021-08-19 08:41:13

)是比較常用的一種通信模式。當(dāng)應(yīng)用系統(tǒng)要求多路UART,或者基于性能、成本綜合考慮選用了不帶UART的 DSP時,可以考慮利用原有的同步串行口,用軟件模擬UART,在硬件上只需簡單的連接便可構(gòu)建UART,以實(shí)現(xiàn)系統(tǒng)的數(shù)據(jù)通信要求。

2019-07-12 06:14:30

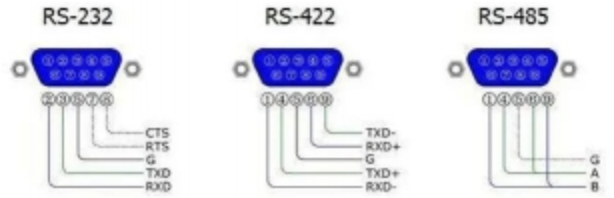

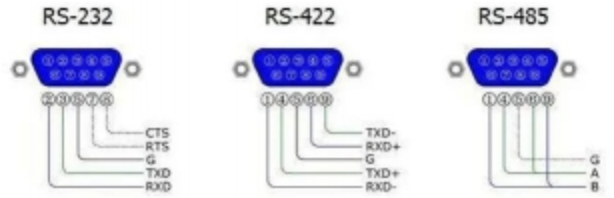

,這里的接口主要指板間通信,像422、485之類的就不展開描述(協(xié)議層都是uart)。低速接口低速接口時單片機(jī)常用的接口,在和FPGA對接時候主要進(jìn)行小數(shù)據(jù)量的通信。低速接口的優(yōu)點(diǎn)就是簡單,易于實(shí)現(xiàn)

2022-08-19 16:32:22

用的貴公司的TL138F-EVM A2開發(fā)板。想利用SPI協(xié)議實(shí)現(xiàn)FPGA和DSP通信。看了核心板引腳說明 沒有看到FPGA這邊SPI協(xié)議要用的接口,是不是這塊板子不能實(shí)現(xiàn)DSP和FPGA的SPI通信。麻煩床龍工程師指導(dǎo)下。還有其他方法嗎?

2020-04-24 06:46:47

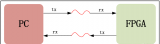

我想用stm32和fpga進(jìn)行uart通信,在硬件連接的時候,它們是直接相連嗎?比如stm32的tx與fpga設(shè)計的rx相連,然后32的rx與fpga串口模塊的tx相連,它們直接需補(bǔ)需要像stm32與pc機(jī)進(jìn)行串口通信時的電平轉(zhuǎn)換。。。

2016-10-12 21:39:39

stm32與FPGA通信用SPI通信如何?

2019-08-03 14:41:57

的UART的實(shí)現(xiàn)方法,具體描述了發(fā)送、接收等模塊的設(shè)計,恰當(dāng)使用了有限狀態(tài)機(jī),實(shí)現(xiàn)了FPGA片上UART的設(shè)計,給出了仿真結(jié)果。關(guān)鍵詞:通用異步收發(fā)器;串口通信;現(xiàn)場可編程邏輯器件;有限狀態(tài)機(jī)

2019-06-21 07:17:24

在利用單片機(jī)開發(fā)各種嵌入式應(yīng)用系統(tǒng)時,異步串行通信是常用的一種通信模式,有的應(yīng)用中還要求實(shí)現(xiàn)多路異步串行通信。人們平時所應(yīng)用的各種廠商的單片機(jī),絕大部分片上只提供一個UART(通用異步收發(fā)器)硬件

2019-10-15 06:25:35

實(shí)現(xiàn)多路信號的復(fù)用;在接收機(jī)中再對其解擴(kuò),恢復(fù)原傳輸信號。利用擴(kuò)頻通信的擴(kuò)頻增益,可大大提高通信系統(tǒng)的信噪比,增加傳輸信號的可靠性改善通信質(zhì)量、提高通信效率。 同時 DSP具有可滿足算法控制復(fù)雜結(jié)構(gòu)

2019-07-08 08:28:48

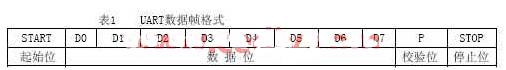

1、在FPGA中實(shí)現(xiàn)串口協(xié)議的設(shè)計在FPGA中實(shí)現(xiàn)串口協(xié)議,通過Anlogic_FPGA開發(fā)板上的“UART2USB”口接收從計算機(jī)發(fā)來的數(shù)據(jù)。實(shí)驗設(shè)計思路UART串口是一種類似于USB、VGA

2022-07-19 11:09:48

時間。針對上述研究現(xiàn)狀和分布式采集場景分析,本文介紹了一種基于FPGA和TOE架構(gòu),實(shí)現(xiàn)TCP/IP協(xié)議數(shù)據(jù)傳輸?shù)?b class="flag-6" style="color: red">多路采集與切換系統(tǒng)。該系統(tǒng)涉及并行數(shù)據(jù)采集、多路通道切換、TCP/IP協(xié)議通信等模塊

2021-07-12 08:30:00

不懂的有疑惑的也可以加微信咨詢,歡迎大家前來投稿,謝謝!引言介紹在電子通信領(lǐng)域里采用的通信協(xié)議有IIC,SPI,UART,F(xiàn)SMC等協(xié)議。本文將基于FPGA來介紹并設(shè)計標(biāo)準(zhǔn)的SPI總線協(xié)議,實(shí)現(xiàn)

2021-11-10 09:37:25

字信號處理、硬件數(shù)字濾波器、各種算法等,或者利用FPGA來擴(kuò)展I/O接口,如實(shí)現(xiàn)多路PWM(脈寬調(diào)制)輸出、實(shí)現(xiàn)PCI接口擴(kuò)展等。通過合理的系統(tǒng)軟硬件功能劃分,結(jié)合優(yōu)秀高效的FPGA設(shè)計,整個嵌入式

2019-05-06 09:18:16

基于FPGA的多路回聲消除算法的實(shí)現(xiàn)中文期刊文章作 者:尹邦政 朱靜 毛茅作者機(jī)構(gòu):[1]廣州廣哈通信股份有限公司,廣東廣州510663;[2]廣州大學(xué)實(shí)驗中心,廣東廣州510006出 版 物

2018-05-08 10:23:36

基于FPGA的光纖通信系統(tǒng)的設(shè)計與實(shí)現(xiàn){:soso_e129:}文章下載鏈接:http://www.zgszdi.cn/soft/5/2012/20120518272336.html

2012-05-22 22:33:59

我需要使用SPI接口配置一些其他的設(shè)備,所以我可以用二UART(這不是多路SPI)連接到PC通過串口?如果這樣做我必須做任何額外的configurationsin固件以及硬件以外的其他例子一般UART調(diào)試congis。

2019-11-06 11:13:57

如何利用FPGA實(shí)現(xiàn)UART的設(shè)計?UART的結(jié)構(gòu)和幀格式

2021-04-08 06:32:05

大家好,這是我第一次使用這種圖形(24EP),所以在閱讀數(shù)據(jù)表后,我不能找到負(fù)責(zé)UART通信的引腳,也是SPI?謝謝你幫助我

2020-04-28 13:46:29

怎么實(shí)現(xiàn)基于AD6623的多路中頻數(shù)字化直擴(kuò)通信系統(tǒng)的設(shè)計?

2021-05-28 06:58:58

受到限制。因此,我們采用ALTERA公司的FPGA器件設(shè)計SPI總線的通信接口,該總線接口具有高速、配置靈活等優(yōu)點(diǎn),大大地縮短了系統(tǒng)的開發(fā)周期。

2019-08-09 08:14:34

求arm和fpga之間SPI通信的源碼

2014-12-09 16:46:23

),有時我們不需要使用完整的UART的功能和這些輔助功能。或者設(shè)計上用到了FPGA/CPLD器件,那么我們就可以將所需要的UART功能集成到FPGA內(nèi)部。使用VHDL將UART的核心功能集成,從而使整個設(shè)計更加緊湊、穩(wěn)定且可靠。本文應(yīng)用EDA技術(shù),基于FPGA/CPLD器件設(shè)計與實(shí)現(xiàn)UART。

2012-05-23 19:37:24

你好!我想在3.0版本協(xié)議棧ZNP工程下實(shí)現(xiàn)串口UART 通信,ZNP默認(rèn)情況下是spi通信,請問我怎樣設(shè)置實(shí)現(xiàn)串口UART通信?需要修改/添加宏定義嘛?謝謝!

2020-08-10 10:57:32

功能可以根據(jù)需要配置,對電路的修改和維護(hù)很方便。目前,FPGA的容量已經(jīng)跨過了百萬門級,使得FPGA成為解決系統(tǒng)級設(shè)計的重要選擇方案之一。在這種架構(gòu)下,應(yīng)用FPGA來構(gòu)建SPI通信接口是切實(shí)可行

2019-05-05 09:29:34

去偏移和包重組是在FPGA中實(shí)現(xiàn)SPI-4.2接口的核心難點(diǎn),在分析偏移和包重組原理的基礎(chǔ)上,給出基于FPGA的SPI-4.2接口的設(shè)計與實(shí)現(xiàn)方案,并對關(guān)鍵部分給出了硬件原理圖,在線測試結(jié)

2009-04-10 09:43:35 32

32 文章介紹了一種在現(xiàn)場可編程門陣列(FPGA)上實(shí)現(xiàn)UART 的方法。UART 的波特率可設(shè)置調(diào)整,工作狀態(tài)可讀取。系統(tǒng)結(jié)構(gòu)進(jìn)行了模塊化分解,使之適應(yīng)自頂向下(Top-Down)的設(shè)計

2009-08-21 11:35:03 52

52 用VHDL 語言在FPGA 內(nèi)部編程實(shí)現(xiàn)組播復(fù)制。本文介紹其實(shí)現(xiàn)方法,并給出了時序仿真波形。通過擴(kuò)展,該設(shè)計可以支持多位寬、多路復(fù)制,因而具有較好的應(yīng)用前景。關(guān)鍵詞:FP

2009-08-26 08:48:25 10

10 UART 是廣泛使用的串行數(shù)據(jù)通訊電路。本設(shè)計包含UART 發(fā)送器、接收器和波特率發(fā)生器。設(shè)計應(yīng)用EDA 技術(shù),基于FPGA/CPLD 器件設(shè)計與實(shí)現(xiàn)UART。關(guān)鍵詞 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 23

23 以太網(wǎng)到多路E1適配電路設(shè)計及FPGA實(shí)現(xiàn)

摘要:介紹了一種基于現(xiàn)場可編程門陣列(FPGA)的以太網(wǎng)數(shù)據(jù)-多路E1反向復(fù)用器同步電路設(shè)計,分析了FPGA具體實(shí)現(xiàn)過程中的一些常

2009-11-13 20:59:00 22

22 本文設(shè)計了一種基于 FPGA 的UART 核,該核符合串行通信協(xié)議,具有模塊化、兼容性和可配置性,適合于SoC 應(yīng)用。設(shè)計中使用Verilog HDL 硬件描述語言在Xilinx ISE 環(huán)境下進(jìn)行設(shè)計、仿真,

2009-11-27 15:48:51 17

17 本文介紹了一種基于FPGA 的高速多路數(shù)據(jù)采集系統(tǒng)的設(shè)計方案,描述了系統(tǒng)的主要組成及FPGA 的實(shí)現(xiàn)方法。在硬件上FPGA 采用ACEX1K100 器件,用于實(shí)現(xiàn)A/D 轉(zhuǎn)換器的控制電路、多路

2009-12-19 16:02:33 50

50 利用 FPGA 實(shí)現(xiàn)UART 的設(shè)計引 言隨著計算機(jī)技術(shù)的發(fā)展和廣泛應(yīng)用,尤其是在工業(yè)控制領(lǐng)域的應(yīng)用越來越廣泛,計算機(jī)通信顯的尤為重要。串行通信雖然使設(shè)備之間的連線大為減

2010-03-24 09:23:40 49

49 ?1.產(chǎn)品概述WK2124是SPITM接口的4通道UART器件,WK2124實(shí)現(xiàn)SPI橋接/擴(kuò)展4個增強(qiáng)功能串口(UART)的功能。擴(kuò)展的子通道的UART具備如下功能特點(diǎn):每個子通道UART的波特率

2023-11-24 00:17:37

文章介紹了一種在現(xiàn)場可編程門陣列(FPGA)上實(shí)現(xiàn)UART 的方法。首先闡述了UART 異步串行通信原理,然后介紹了實(shí)現(xiàn)UART異步串行通信的硬件接口電路及各部分硬件模塊,以及用硬件

2010-08-06 16:24:13 55

55 為了滿足某測控平臺的設(shè)計要求,設(shè)計并實(shí)現(xiàn)了基于FPGA的六通道HDLC并行通信系統(tǒng)。該系統(tǒng)以FPGA為核心,包括FPGA、DSP、485轉(zhuǎn)換接口等部分。給出了系統(tǒng)的電路設(shè)計、關(guān)鍵模塊及軟件

2010-09-30 16:49:30 43

43 FPGA的多路可控脈沖延遲系統(tǒng)設(shè)計

采用數(shù)字方法和模擬方法設(shè)計了一種最大分辨率為0.15 ns級的多路脈沖延遲系統(tǒng),可以實(shí)現(xiàn)對連續(xù)脈沖信號的高分辨

2009-03-29 15:09:48 2234

2234

摘 要 :UART是廣泛使用的串行數(shù)據(jù)通訊電路。本設(shè)計包含UART發(fā)送器、接收器和波特率發(fā)生器。設(shè)計應(yīng)用EDA技術(shù),基于FPGA/CPLD器件設(shè)計與實(shí)現(xiàn)UART。

2009-06-20 13:14:52 982

982

盛群半導(dǎo)體推出SPI to UART Bridge IC-HT45B0F。HT45B0F是一款可實(shí)現(xiàn)SPI與UART數(shù)據(jù)轉(zhuǎn)換應(yīng)用于微控制器周邊設(shè)備

2011-07-05 09:41:13 1424

1424 SPI 串行總線是一種常用的標(biāo)準(zhǔn)接口,其使用簡單方便而且占用系統(tǒng)資源少,應(yīng)用相當(dāng)廣泛。本文將介紹一種新的通用的SPI 總線的FPGA 實(shí)現(xiàn)方法。

2011-09-09 11:58:27 67

67 隨著FPGA的廣泛應(yīng)用,經(jīng)常需要FPGA與其他數(shù)字系統(tǒng)進(jìn)行串行通信,專用的UART集成電路如8250,8251等是比較復(fù)雜的,因為專用的UART集成電路既要考慮異步的收發(fā)功能,又要兼容RS232接口設(shè)計

2011-09-16 11:57:43 4392

4392

UART 是廣泛使用的串行數(shù)據(jù)通訊電路。本設(shè)計包含UART 發(fā)送器、接收器和波特率發(fā)生器。設(shè)計應(yīng)用EDA 技術(shù),基于FPGA/CPLD 器件設(shè)計與實(shí)現(xiàn)UART。

2011-12-17 00:15:00 57

57 多路交換開關(guān)是高性能交換部件的核心,本文描述了基于Xilinx公司Virtex-11系列FPGA的特點(diǎn)設(shè)計和實(shí)現(xiàn)的一種高速多路交換開關(guān),它由輸入信道組織、內(nèi)部無阻塞crossbar交換和仲裁調(diào)度器三

2011-12-27 16:45:04 46

46 對SPI、IIC、IIS、UART、SDIO、GPIO 簡介

2015-10-29 17:00:01 0

0 串口通訊通信協(xié)議UART,以及常用外設(shè)通信協(xié)議 SPI、I2C的介紹與他們之間的區(qū)別

2015-11-30 11:28:36 91

91 詳細(xì)介紹了SPI、SCI、I2C、UART幾種通信方式的異同便于讀者整體了解通信的意義.

2015-12-15 14:32:19 0

0 為了實(shí)現(xiàn)對多路視頻和數(shù)據(jù)信號的同步傳輸,提出了一種基于FPGA的視頻數(shù)據(jù)綜合傳輸系統(tǒng)設(shè)計方案,并完成系統(tǒng)的軟硬件設(shè)計。該系統(tǒng)的硬件部分主要由FPGA、CPLD芯片及光模塊等設(shè)備組成,軟件部分采用

2015-12-31 09:26:25 11

11 華清遠(yuǎn)見FPGA代碼-RS-232C(UART)接口的設(shè)計與實(shí)現(xiàn)

2016-10-27 18:07:54 10

10 FPGA和Si4463的跳頻語音通信系統(tǒng)設(shè)計與實(shí)現(xiàn)

2017-08-31 11:05:53 15

15 MSP430G2553的UART與SPI應(yīng)用

2017-10-12 14:09:18 40

40 SPI總線的多路數(shù)據(jù)采集系統(tǒng)的設(shè)計

2017-10-16 09:27:26 22

22 FPGA和UART的MCU總線數(shù)據(jù)采集系統(tǒng)設(shè)計

2017-10-31 15:20:51 8

8 系統(tǒng)總線速率的四分之一,遠(yuǎn)遠(yuǎn)高于UART、GPIO等接口,在高速通信中得到廣泛應(yīng)用。針對各類應(yīng)用中的高速通信需求,SKYLAB推出了多款支持SPI接口的WiFi模塊。本篇SKYLAB君將為大家介紹幾款支持

2018-04-16 10:26:34 22717

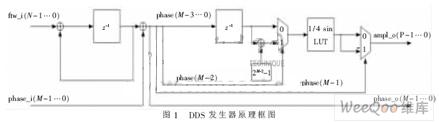

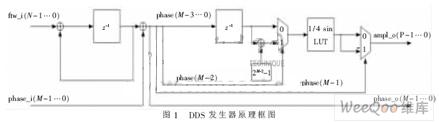

22717 控制器接收專用芯片外部異步串口傳送的數(shù)據(jù),將這些數(shù)據(jù)進(jìn)行處理后傳送到DDS模塊相應(yīng)寄存器,從而產(chǎn)生特定頻率相位的正弦波信號;最后將程序固化到片內(nèi)RAM中,在FPGA上實(shí)現(xiàn)多路正弦波信號發(fā)生器專用芯片的設(shè)計。

2018-12-30 09:03:00 8312

8312

實(shí)現(xiàn)RS-232電平和TTL/CMOS電平轉(zhuǎn)換可以用接口芯片來實(shí)現(xiàn),實(shí)現(xiàn)數(shù)據(jù)的串行到并行轉(zhuǎn)換用的是UART,它們是實(shí)現(xiàn)串行通信必不可少的兩個部分。雖然目前大部分處理器芯片中都集成了UART,但是一般

2019-10-18 07:54:00 2317

2317

本節(jié)繼續(xù)講嵌入式硬件通信接口協(xié)議中的另外一個串行通信接口-SPI。相比于UART串口協(xié)議,SPI又有著其獨(dú)特之處。

2019-02-05 11:35:00 1438

1438

提出了一種基于FPGA+ARM的多路視頻采集系統(tǒng)的設(shè)計與實(shí)現(xiàn)方法。該視頻采集系統(tǒng)不僅能對多路快速變化的視頻信號進(jìn)行采集和處理,而且能應(yīng)用為系統(tǒng)信號發(fā)生設(shè)備.系統(tǒng)采用FPGA為核心高速時序邏輯控制

2019-11-19 15:51:42 21

21 工程師,在研發(fā)設(shè)計電路項目,可能會使用不同標(biāo)準(zhǔn)協(xié)議的通信方式;常見的通信方式類型包含USB通信,如U盤的接口是采用USB通信;

UART通信,如數(shù)字溫濕度傳感器的接口是采用UART通信

2020-02-07 10:32:57 23881

23881 UART作為RS232協(xié)議的控制接口得到了廣泛的應(yīng)用,將UART的功能集成到FPGA芯片中,可使整個系統(tǒng)更為靈活、緊湊,減小整個電路的體積,提高系統(tǒng)的可靠性和穩(wěn)定性。提出了一種基于FPGA

2020-07-07 15:51:05 7

7 UART作為RS232協(xié)議的控制接口得到了廣泛的應(yīng)用,將UART的功能集成到FPGA芯片中,可使整個系統(tǒng)更為靈活、緊湊,減小整個電路的體積,提高系統(tǒng)的可靠性和穩(wěn)定性。提出了一種基于FPGA的UART

2020-07-07 17:28:03 10

10 偏移和包重組是在FPGA中實(shí)現(xiàn)SPI一4.2接口的核心難點(diǎn),在分析偏移和包重組原理的基礎(chǔ)E,給出基于FPGA的SPI一4.2接口的設(shè)計與實(shí)現(xiàn)方案,并對關(guān)鍵部分給出r硬件原理圖,在線測試結(jié)果證明該方案可以實(shí)現(xiàn)SPI一4.2接口的功能。

2021-01-25 14:51:21 13

13 主要介紹基于FPGA實(shí)現(xiàn)多路模擬信號自適應(yīng)采集系統(tǒng)的設(shè)計。該系統(tǒng)主要包括軟件和硬件兩部分:硬件主要采用FPGA芯片,AD7982—1,ADG406和運(yùn)放AD824來搭建硬件平臺;軟件包括FPGA程序

2021-02-02 15:52:34 5

5 的。本設(shè)計使用Xilinx的FPGA器件,只將UART的核心功能嵌入到FPGA內(nèi)部,不但實(shí)現(xiàn)了電路的異步通訊的主要功能,而且使電路更加緊湊、穩(wěn)定、可靠。

2021-04-27 14:07:25 8

8 基于FPGA的光纖通信系統(tǒng)的設(shè)計與實(shí)現(xiàn)的講解。

2021-05-25 16:26:19 26

26 基于FPGA的UART模塊設(shè)計與實(shí)現(xiàn)介紹說明。

2021-06-01 09:43:30 19

19 基于FPGA的無線通信系統(tǒng)設(shè)計與實(shí)現(xiàn)

2021-06-16 09:59:29 44

44 電子設(shè)備之間的通信就像人類之間的交流,雙方都需要說相同的語言。在電子產(chǎn)品中,這些語言稱為通信協(xié)議。 之前有單獨(dú)地分享了SPI、UART、I2C通信的文章,這篇對它們做一些對比。 串行 VS 并行

2021-09-30 15:30:16 4020

4020 typora-copy-images-to: typora_picture基于FPGA與MCU通信的SPI協(xié)議設(shè)計1. SPI總線協(xié)議介紹及硬件設(shè)計1.1 SPI總線協(xié)議介紹及硬件設(shè)計SPI總線

2021-11-05 15:35:59 13

13 基于FPGA的SPI協(xié)議及設(shè)計實(shí)現(xiàn)博主微信:flm13724054952,不懂的有疑惑的也可以加微信咨詢,歡迎大家前來投稿,謝謝!引言介紹在電子通信領(lǐng)域里采用的通信協(xié)議有IIC,SPI,UART

2021-11-05 19:05:59 22

22 STM32模擬SPI通信協(xié)議SPI的簡介:SPI是串行外設(shè)接口的縮寫,是一種高速的,全雙工、同步的串行通信總線;SPI也可以實(shí)現(xiàn)一主多從,而實(shí)現(xiàn)一主多從是通過CS片選來實(shí)現(xiàn),于IIC有些不同;SPI

2021-12-22 19:20:00 21

21 寫在前面SPI協(xié)議系列文章:FPGA實(shí)現(xiàn)的SPI協(xié)議(一)----SPI驅(qū)動 在上篇文章,簡要介紹了SPI協(xié)議,編寫了SPI協(xié)議的FPGA驅(qū)動,但是在驗證環(huán)節(jié),僅僅驗證了發(fā)送時序,而沒有

2021-12-22 19:25:39 19

19 stm32作為從機(jī),fpga作為主機(jī)。進(jìn)行spi通信。stm32使用dma進(jìn)行數(shù)據(jù)接收。在dma中斷中進(jìn)行接收數(shù)據(jù)和處理。通過調(diào)節(jié)fpga里面spi數(shù)據(jù)的發(fā)送頻率。來保證stm32實(shí)時處理數(shù)據(jù),做出控制相應(yīng)。下面是fpga抓取到的spi信號。...

2021-12-22 19:29:34 90

90 向大家詳細(xì)的全面的介紹單片機(jī)畢設(shè)項目,從單片機(jī)的基礎(chǔ)知識,到完整的單片機(jī)系統(tǒng)設(shè)計~單片機(jī) SPI 通信接口UART、I2C 和 SPI 是單片機(jī)系統(tǒng)中最常用的三種通信協(xié)議。前邊我們已經(jīng)學(xué)了 UART 和 I2C 通信協(xié)議,這節(jié)課我們來學(xué)習(xí)剩下的 SPI 通信協(xié)議。SPI 是英語 Seria

2021-12-22 19:34:40 13

13 目前WK系列能實(shí)現(xiàn)SPI擴(kuò)展uart的芯片包括 WK2124、WK2204、WK2168、WK2132。目前 WK2124、WK2204、WK2168 能實(shí)現(xiàn) SPI 擴(kuò)展 4 路 UART

2022-04-18 09:10:08 12

12 UART和后面兩者最大的區(qū)別在于后面兩者是同步的,要有統(tǒng)一的時鐘線,而UART不需要,接線方便,但收發(fā)雙方都需要配置相同的波特率,即設(shè)備要有自己的時鐘源;I2C協(xié)議中是有地址規(guī)則的,因此在一對多通信

2022-07-27 17:16:24 2101

2101

)。SPI總線可以實(shí)現(xiàn)多個SPI設(shè)備互相連接。提供SPI串行時鐘的SPI設(shè)備為SPI主機(jī)或主設(shè)備(Master),其他設(shè)備為SPI從機(jī)或從設(shè)備(Slave)。主從設(shè)備間可以實(shí)現(xiàn)全雙工通信,當(dāng)有多個從設(shè)備時,還可以增

2022-10-30 13:28:03 4193

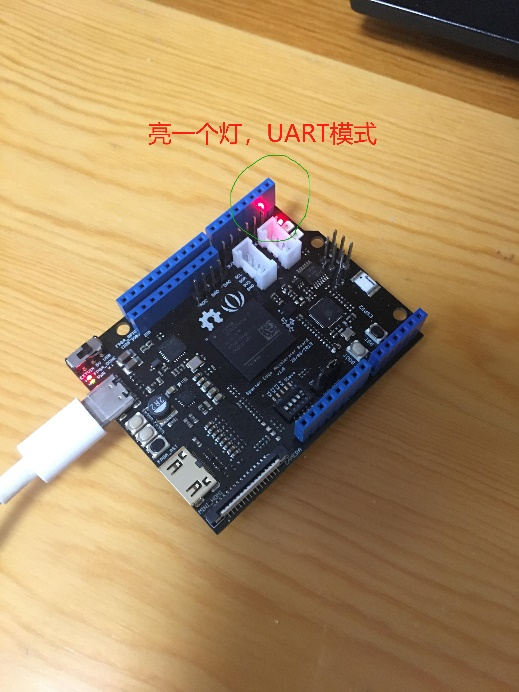

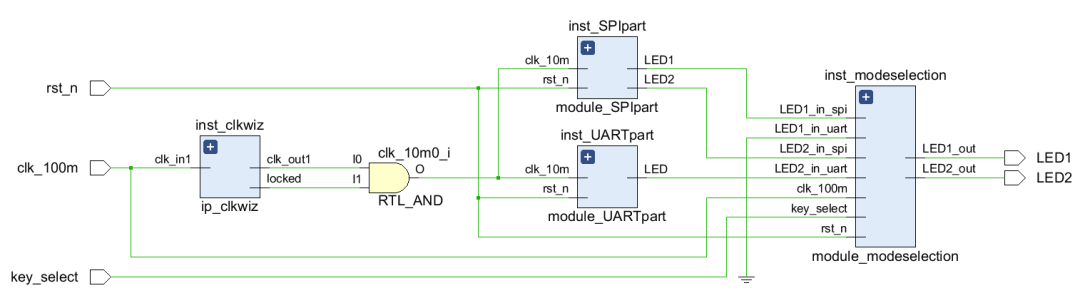

4193 本次的設(shè)計為多路UART/SPI通信系統(tǒng),可以實(shí)現(xiàn)一對多的通信。系統(tǒng)可以運(yùn)行在UART模式,也可以運(yùn)行在SPI模式。我選擇這一課題的原因主要是目前我所在的實(shí)驗室需要寫基于UART的快速通信。這一

2023-02-20 11:10:31 1160

1160 FPGA實(shí)現(xiàn)SPI協(xié)議

2023-03-20 10:35:02 0

0 UART、I2C、SPI都是常見的低速板級通信協(xié)議,目前主流的SoC都內(nèi)置了這些通訊協(xié)議的控制器,同樣,各種傳感器、Touch控制器、指紋模塊、藍(lán)牙模塊、WIFI模塊也都兼容這三種通信方式的一種或幾種。

2023-03-26 09:29:35 1277

1277 目的:實(shí)現(xiàn)上位機(jī)與FPGAuart交互

開發(fā)環(huán)境:quatus prime 18.1,芯片 altera :EP4CE15F23C8。

實(shí)驗現(xiàn)象: 1.使用uart:bps=9600(參數(shù)可調(diào)整

2023-05-08 10:28:33 2

2 電子發(fā)燒友網(wǎng)站提供《如何通過SPI使用Raspberry PI零與FPGA通信.zip》資料免費(fèi)下載

2023-06-13 15:52:10 0

0 電子發(fā)燒友網(wǎng)站提供《基于FPGA的光纖通信系統(tǒng)的設(shè)計與實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-10-24 10:59:21 2

2 ,較少用于遠(yuǎn)距離通信。 SPI實(shí)現(xiàn)要簡單一些,UART需要固定的波特率,就是說兩位數(shù)據(jù)的間隔要相等,而SPI則無所謂,因為它是有時鐘的協(xié)議。 I2C的速度比SPI慢一點(diǎn),協(xié)議比SPI復(fù)雜一點(diǎn),但是連線也比標(biāo)準(zhǔn)的SPI要少。 UART一幀可以傳5/6/7/8位,I2C必須是8位。I2C和SPI都從最高位開

2023-11-09 18:06:42 613

613

使用SPI接口時,需要根據(jù)具體的外設(shè)和系統(tǒng)需求來配置SPI的參數(shù),如通信速度、數(shù)據(jù)位寬、主從模式等。主設(shè)備通過操作SPI相關(guān)的寄存器或調(diào)用相應(yīng)的庫函數(shù)來控制數(shù)據(jù)傳輸和通信。從設(shè)備則根據(jù)SPI協(xié)議

2023-11-10 16:47:28 2887

2887

電子發(fā)燒友App

電子發(fā)燒友App

評論