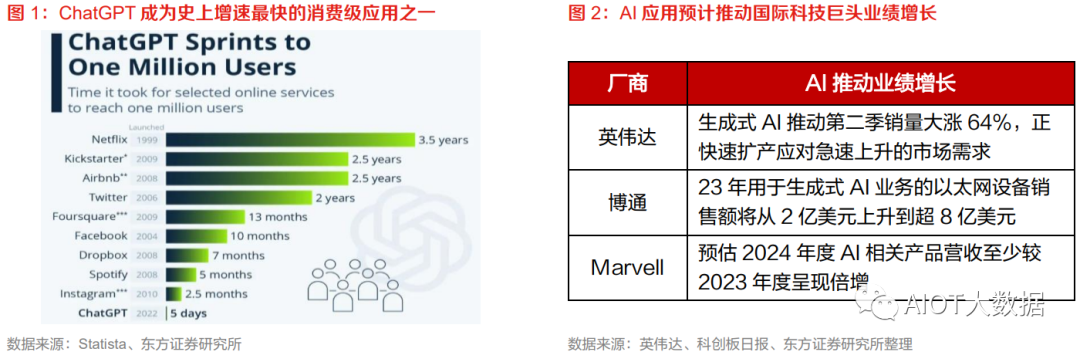

AI未來已來,算力、網絡設備和光模塊等領域率先受益。2022年11月底,OpenAI發布聊天機器人ChatGPT,僅用5天用戶破百萬,2個月活躍用戶破億,成為史上增速最快的消費級應用之一。2023年3月,英偉達召開的GTC開發者大會猶如“深水炸彈”,創始人兼CEO黃仁勛提出的全新概念:我們正處于AI的“iPhone時刻”。目前AI正在迎來爆發式增長,將成為數十年來最有前途的技術領域之一,并將驅動算力、網絡設備和光模塊等領域的極大發展。受益于此,博通和Marvell等網絡與通信芯片巨頭的股價均迎來大幅上漲。博通表示23年用于生成式AI業務的以太網設備銷售額將從2億美元上升到超8億美元;Marvell也于近期表示AI已成為關鍵成長動能,預估2024財年AI相關產品營收至少較2023年度呈現倍增,并在未來幾年持續迅速成長。

高速率光技術持續演進。

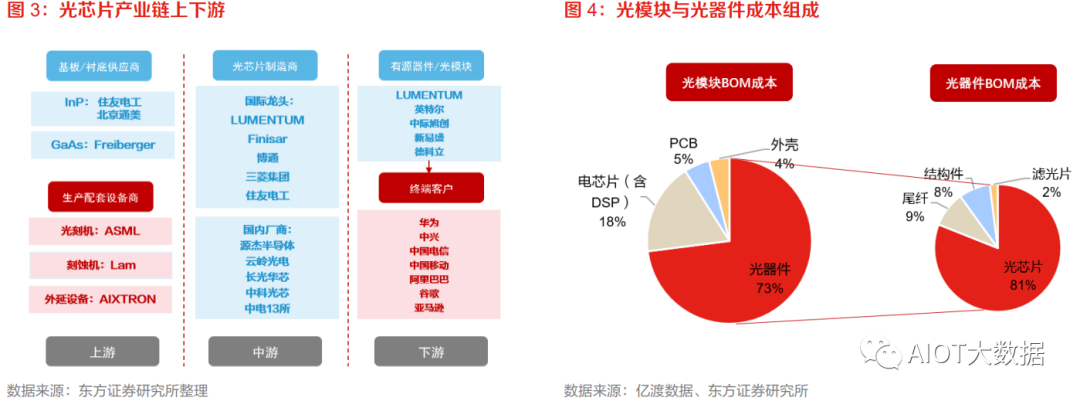

作為AI算力的核心器件,光模塊及其配套芯片持續迭代:1)CPO、LPO等先進封裝技術在降低光模塊成本及功耗上作用顯著,中際旭創、新易盛等光模塊廠商率先布局;2)EML、硅光和薄膜鈮酸鋰等光芯片不斷升級來適配高速率場景應用,源杰科技、長光華芯和光庫科技等廠商不斷突破芯片技術瓶頸。光芯片作為光模塊中最核心的部件(光器件占光模塊成本的73%,光芯片占光器件成本的81%),擁有更大的附加價值量彈性和國產替代預期,在產業鏈中地位尤其重要,光芯片廠商亦有望在AI浪潮中持續受益。

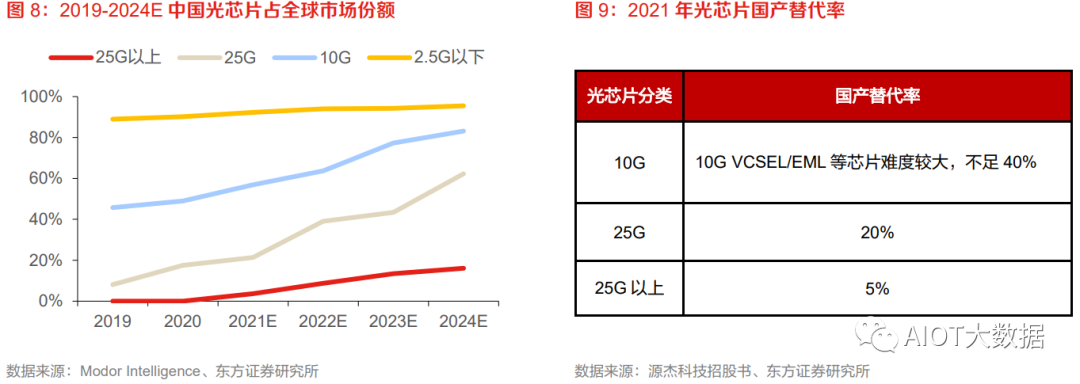

光芯片三重邏輯共振:1)AI算力高彈性;2)國產替代預期;3)下游模塊廠商出海加持。在AI算力需求拉動下光模塊向更高速率演進,光芯片作為光模塊核心器件有望深度受益;中國光芯片市場規模持續增加,國產化進程有望持續邁進;國內下游模塊廠商海外業務不斷拓展,光芯片可以跟隨光模塊出海,有望應用到谷歌、微軟等海外互聯網大廠。在前沿光通信技術發展和高算力需求的共同催化下,將有力推動光芯片的技術升級和更新換代,硅光芯片、薄膜鈮酸鋰調制器芯片等有望成為更優解決方案。

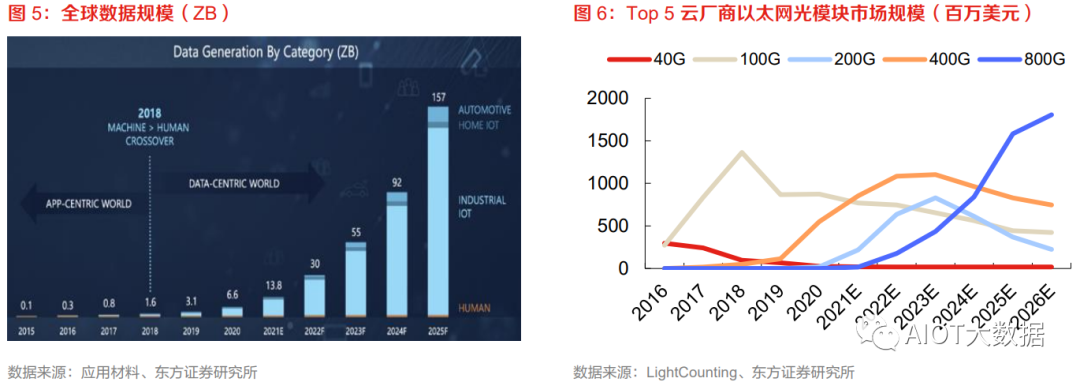

1)算力需求帶動高速率光模塊市場量價齊升。全球數據規模隨著AIGC的發展預計增速會持續提升,數據中心高速率光模塊市場相應將獲得較大增量市場。根據中國計算機互連技術聯盟(CCITA)CPO標準及草根調研數據,云計算通用服務器所屬葉脊架構的交叉互聯網絡中上行、下行端口收斂比約為3:1,1臺服務器約需要4-6個光模塊,整體平均單價在1美金/GB左右;而AI服務器所用的A100、H100等GPU,需用200G以上的高速率光模塊8-10個/片。

根據LightCounting的統計,全球Top5云廠商以太網光模塊市場體現出對高速率光模塊的偏好。2023年800G光模塊需求預計將進一步替代較低速率光模塊的份額,整體高速率光模塊用量和規格不斷提升,呈量價齊升之勢。

光芯片是光模塊的核心器件,附加價值量彈性更大。

根據LightCounting數據測算,光芯片占光模塊市場比重從2018年約15%的水平到2025以后超過25%的水平,光芯片有望深度受益。相對于光模塊和器件,光芯片具有更大的附加價值量彈性,其成本占比分布在低端器件、中端器件、高端器件上的數據逐級提升,大約分別為20%、50%、70%。隨著通訊、AI等產業對高性能光模塊的需求快速增長,光芯片將呈現量價齊升的增長趨勢。

2)中國光芯片市場規模持續增加,光芯片國產替代正當時。

根據ICC預測,2019-2024年,中國光芯片廠商銷售規模占全球光芯片市場的比例將不斷提升。目前,我國光芯片企業已基本掌握2.5G及以下速率光芯片的核心技術;部分10G光芯片產品性能要求較高、難度較大,如10GVCSEL/EML激光器芯片等,國產化率不到40%;25G及以上光芯片方面,隨著5G建設推進,我國光芯片廠商在應用于5G基站前傳光模塊的25GDFB激光器芯片有所突破,數據中心市場光模塊企業開始逐步使用國產廠商的25GDFB激光器芯片,2021年25G光芯片的國產化率約20%,但25G以上光芯片的國產化率仍較低,約為5%,目前仍以海外光芯片廠商為主。

3)光芯片可以跟隨光模塊出海,有望應用到海外大廠的AI服務器及數據中心當中。

海外光芯片企業已形成產業閉環和高行業壁壘,可自主完成芯片設計、晶圓外延等關鍵工序,可量產25G及以上速率的光芯片。部分中國光芯片企業已具備領先水平,隨著技術能力提升和市場認可度提高,競爭力將進一步增強。目前全球光模塊市場主要由美中日三國占據主導地位,2021年光模塊全球前十的生產商中有一半來自中國。隨著國內下游模塊廠商海外業務的不斷拓展,光芯片可以跟隨光模塊出海,有望應用到海外大廠,國產光芯片發展前景廣闊。

CPO、LPO、硅光、相干以及薄膜鈮酸鋰等技術值得關注,將有力推動光芯片技術升級和更新換代。數據中心的商業模式下,云廠商在成本端有充分的動力為低功耗服務器買單;同時,在低功耗的基礎上,AI服務器對低時延有著更高的要求。因此,除了以CPO與硅光技術為主線的光模塊發展路徑外,LPO方案應運而生。同時,在相干光通訊和非相干數據中心的信號傳輸中,薄膜鈮酸鋰所制備的超高速率電光調制器有望受益于光器件集成新趨勢,從而打開更加廣闊的市場空間。在前沿光通信技術發展與高算力需求拉動的共同催化下,高速率光芯片前景廣闊,更高速率的DFB、EML芯片、硅光芯片、薄膜鈮酸鋰調制器芯片等將成為更優解決方案。此外,立訊精密、長電科技等消費電子/半導體公司也逐步進入光模塊/芯片賽道,有望將成熟技術應用到光芯片產業鏈,進一步降本增效促進行業發展。

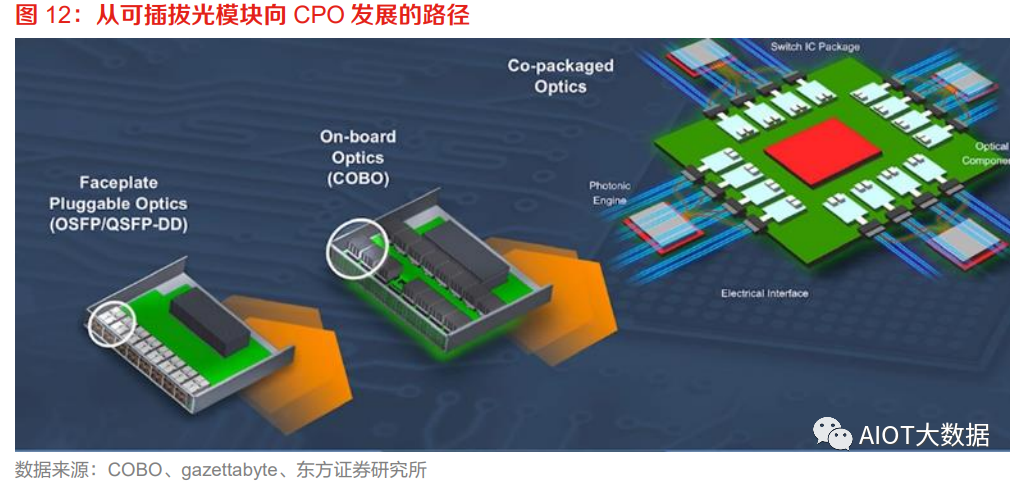

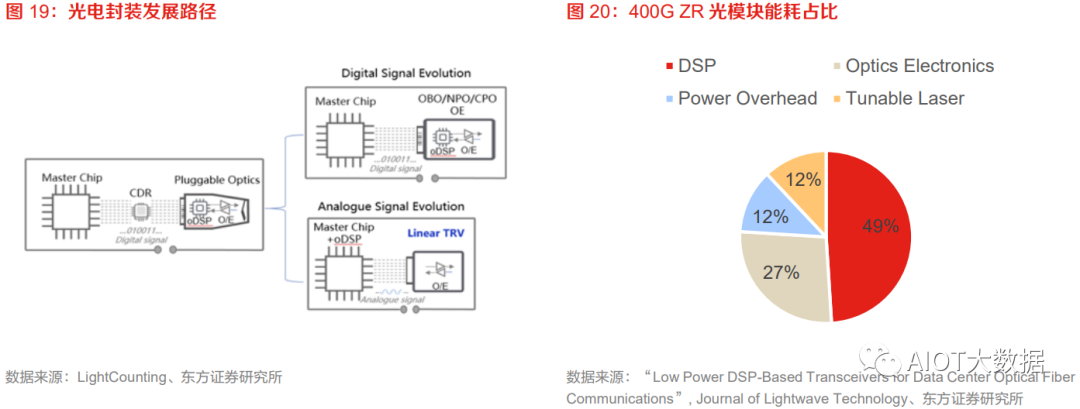

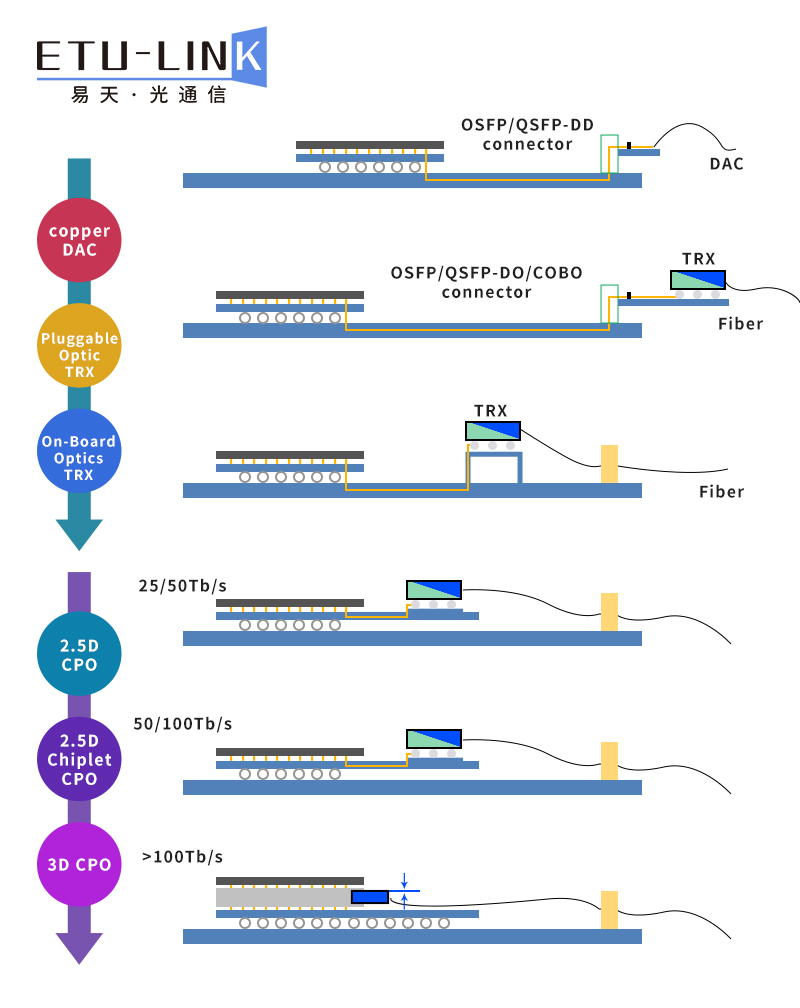

CPO是光通訊實現光電轉換的長期路徑

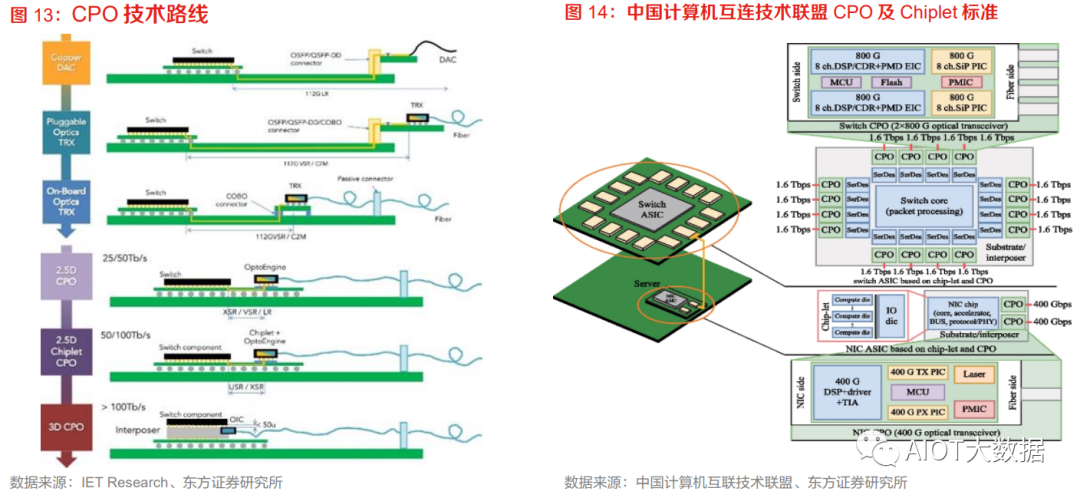

CPO是長期路徑;LPO易落地,是短中期極具性價比的過渡方案。CPO方案是通過在交換機光電共封裝起到降低成本、降低功耗的目的。長期來看,CPO是實現高集成度、低功耗、低成本以及未來超高速率模塊應用方面最優的封裝方案。由于目前的技術與產業鏈尚不成熟等原因,短期內難以大規模應用。相比之下,LPO主要的技術壁壘在于更復雜的RF模塊,仍然采用可插拔模塊的形式,可靠性高且便于維護,可以直接應用于目前成熟的光模塊供應鏈。

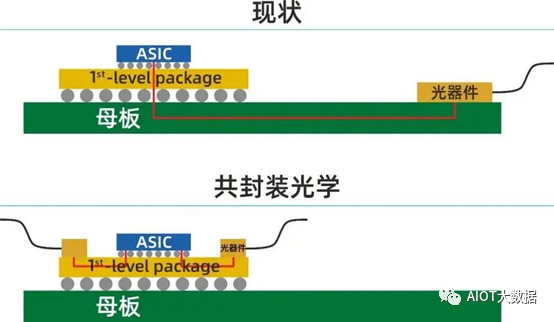

CPO是在成本、功耗、集成度各個維度上優化數據中心的光電封裝方案。CPO(CopackagedOptics)將光模塊不斷向交換芯片靠近,縮短芯片和模塊之間的走線距離,最終將光引擎和電交換芯片封裝成一個芯片。理想情況下,CPO可以逐步取代傳統的可插拔光模塊,將硅光子模塊和超大規模CMOS芯片以更緊密的形式封裝在一起,從而在成本、功耗和尺寸上都進一步提升數據中心應用中的光互連技術。

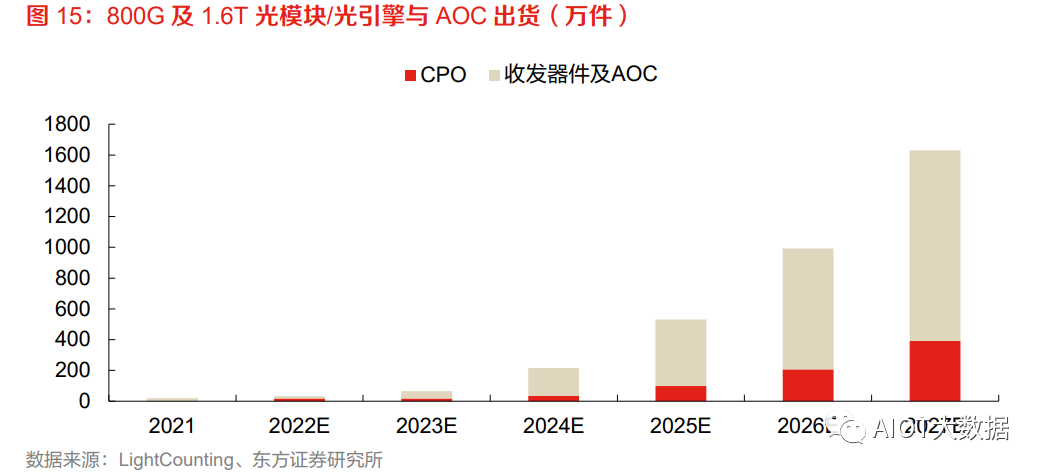

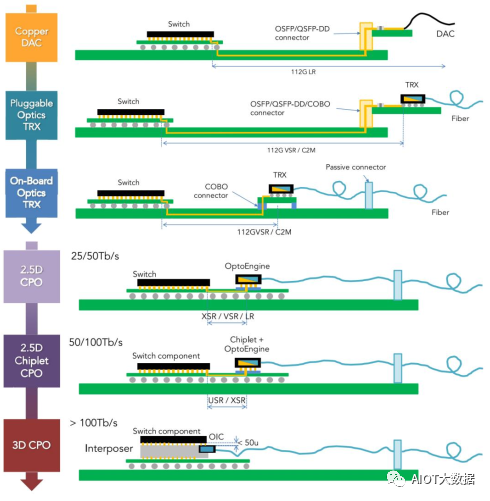

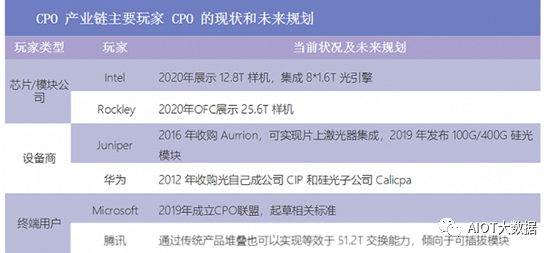

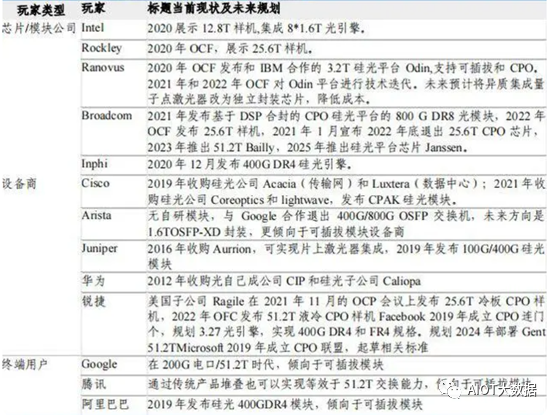

高速率CPO滲透率預計從24年開始顯著提升,高速率光模塊需求海外先行。根據LightCounting數據預測,800G/1.6T光模塊與AOC加上CPO出貨將從2022年不到百萬件增長至2027年超過1500萬件,其中CPO滲透率將從24年開始快速提升。2023年4月5日全球光互連論壇OIF發布業界首個3.2T共封裝模塊實施協議,可見目前海外市場,尤其是高速率板塊對CPO需求更為迫切,國內上量節奏緊隨其后。

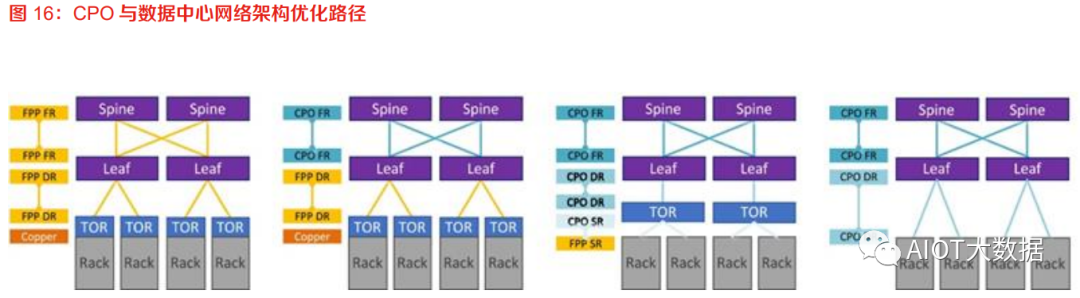

CPO的發展需要產業鏈協同推進,考驗光模塊/光引擎廠商的長期綜合實力。CPO的技術路線在逐步推進的過程中本質上也是對整個網絡架構的優化,需要數據中心整體產業鏈的協同推進。其中涉及到的環節在現有光模塊產業鏈的基礎上預計還需要得到交換芯片及設備廠商,以及各元器件廠商的合作。因此CPO的進度本質上是對光模塊/光引擎廠商綜合實力的長期考驗,包括在光模塊零部件、封裝等方面的技術積累與研發實力,以及下游客戶的關系。

MicroTEC是高速率光通信領域實現精準控溫的優質方案。TEC(ThermoElectricCooler)半導體制冷器是指利用熱電材料的帕爾貼效應制取冷量的器件,又稱熱電制冷器,具有無噪聲、無振動、不需制冷劑、體積小、重量輕等特點,易于進行冷量調節。TEC的重要性對于光模塊而言,不僅在于降溫散熱,核心在于保持工作波長的穩定,激光器波長會根據自身溫度來進行漂移,如果不控制波長溫度,就會引起通道間串擾,TEC則可以通過該電流精準實現優于0.1℃的溫度控制。在光模塊領域,對于目前的200G/400G/800G高速光模塊,必須使用MicroTEC來實現工作波長的穩定。隨著數據中心400G/800G模塊、長距離相干模塊的發展,對微型化的局部精準控溫提出了更高要求,TEC未來市場前景廣闊。

光模塊龍頭及光芯片技術領先的供應商直接受益于市場增量,對于產業發展趨勢更具話語權。

目前,華工科技、源杰科技等多家廠商布局CPO領域。其中,華工科技“光聯接+無線聯接”的解決方案市占率行業領先,100G/200G/400G全系列光模塊批量交付,CPO技術的各種類型800G系列產品已經給北美頭部廠家送樣測試。源杰科技是國內高速率光芯片龍頭,公司CW大功率光源可以用于CPO領域,已向多家客戶送樣測試。銘普光磁的光模塊產品廣泛應用于數通領域,400G系列產品已生產交付,800G光模塊預研中,其中CPO相關技術是公司未來研發的重要方向之一。中際旭創、仕佳光子、聯特科技等廠商在CPO領域亦有所布局。富信科技是目前國內少數能夠批量生產光通信應用高性能超微型熱電制冷器件的企業,22年公司已經具備了年產200萬片MicroTEC的批量化生產能力。

LPO是短中期極具性價比的過渡方案

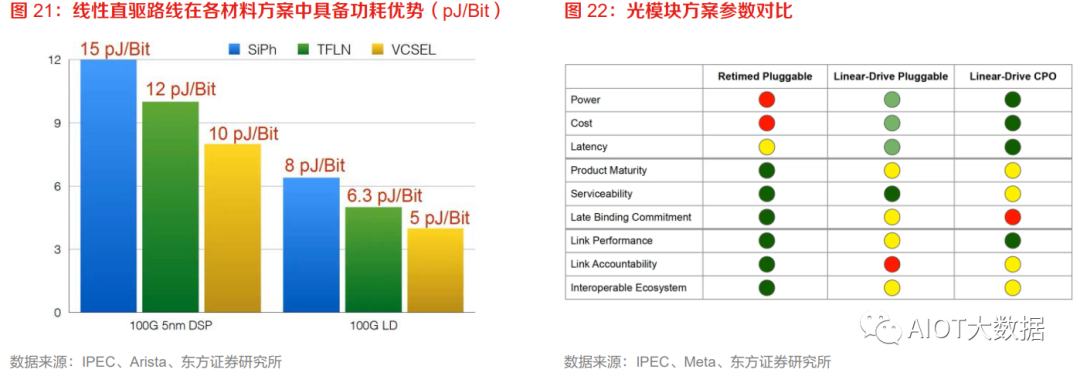

LPO光模塊在功耗、時延方面更優,設計核心在于去DSP化。LPO(Linear-drivePluggableOptics)線性驅動可插拔光模塊是基于LinearDriver芯片技術實現的可插拔光模塊,線性驅動的方案的直接表征在于去DSP化,在數據鏈路中只使用線性模擬元件,無CDR或DSP的設計方案。DSP是數字信號處理器,隨著高性能DSP不斷迭代,目前整體來看高速率光模塊中DSP芯片功耗占比約在50%的水平。因此LPO去DSP在可插拔光模塊上具備顯著的低功耗優勢。

短距離、低功耗、低時延、低成本特性使得LPO方案適配AI計算中心。LPO方案的特點是適用于短距離、低成本、低功耗、低時延。根據草根調研,LPO方案較之傳統可插拔光模塊方案成本保守估計可降低15%,功耗降低50%,時延可從微妙級降至納秒級。這些都是取締DSP而產生的優勢,但也在信號恢復方面有所犧牲。目前的LPO方案其信號恢復性能主要由Host交換芯片所含的收發DSP/Serdes,以及線性直驅driver中的CTLE和TIA中的Pre-emphasize來補償。

加速落地,高線性度TIA/Driver廠商大力推進LPO方案。

Macom、Semtech、美信等電芯片實力強勁的廠商,在DSP領域不及博通、Inphi,從而希望通過LPO方案繞開DSP短板。因此這些廠商有很強的驅動力與光模塊封裝設計廠商合作,比如目前Macom與劍橋科技的戰略合作等。加上LPO方案在性能、成本等方面確有不小的優勢,契合服務器廠商需求,整體推進速度較快。

華工科技、新易盛、中際旭創等LPO進度較快的廠商有望率先發力。

其中,華工科技積極布局LPO方案,結合LPO技術800G系列產品都已經給北美頭部廠家送樣測試。新易盛作為高速率光模塊供應商,在LPO技術領域已深入布局,OFC2023期間推出多款相關產品,與主流廠商和用戶建立起了良好合作關系,并積極推動LPO相關測試項目的進展,力爭在LPO相關產品的市場競爭中占得先機。

硅光集成趨勢下光引擎地位凸顯

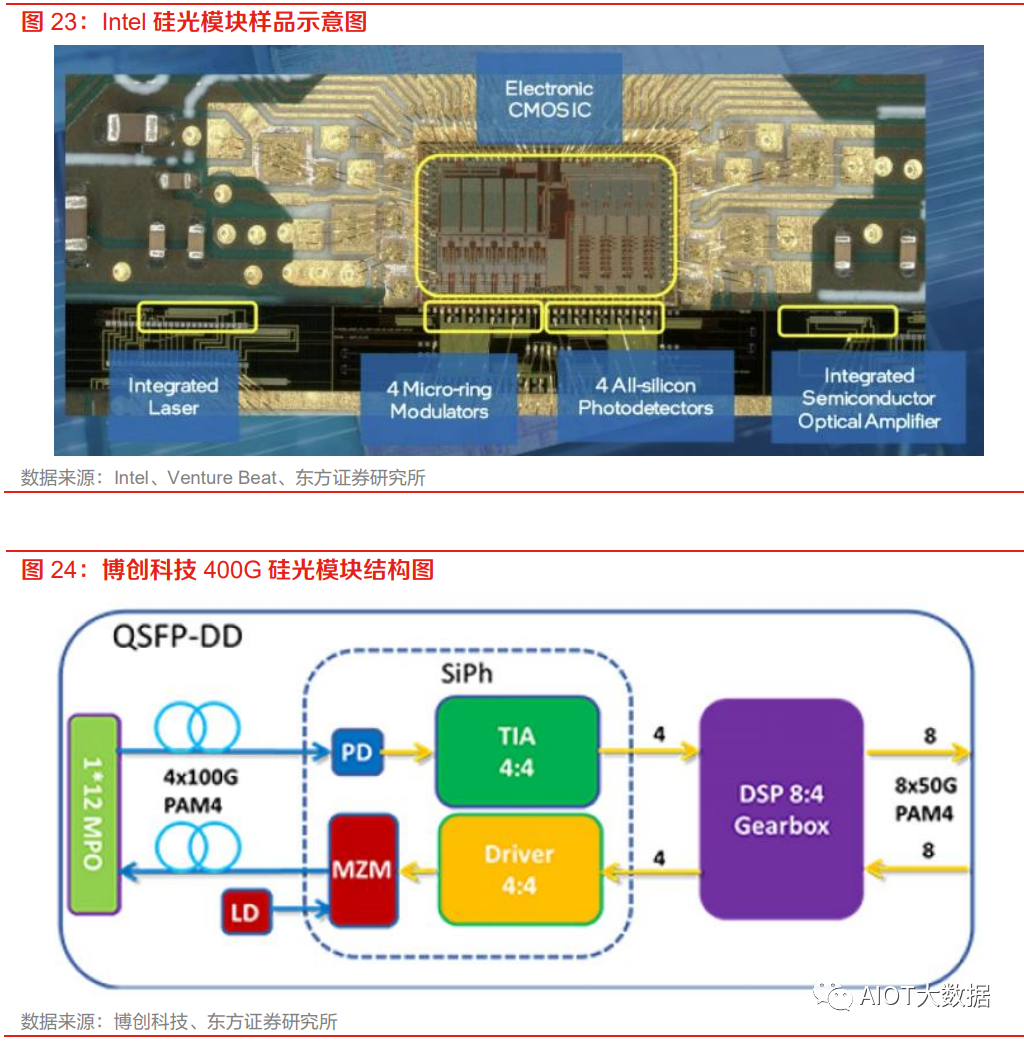

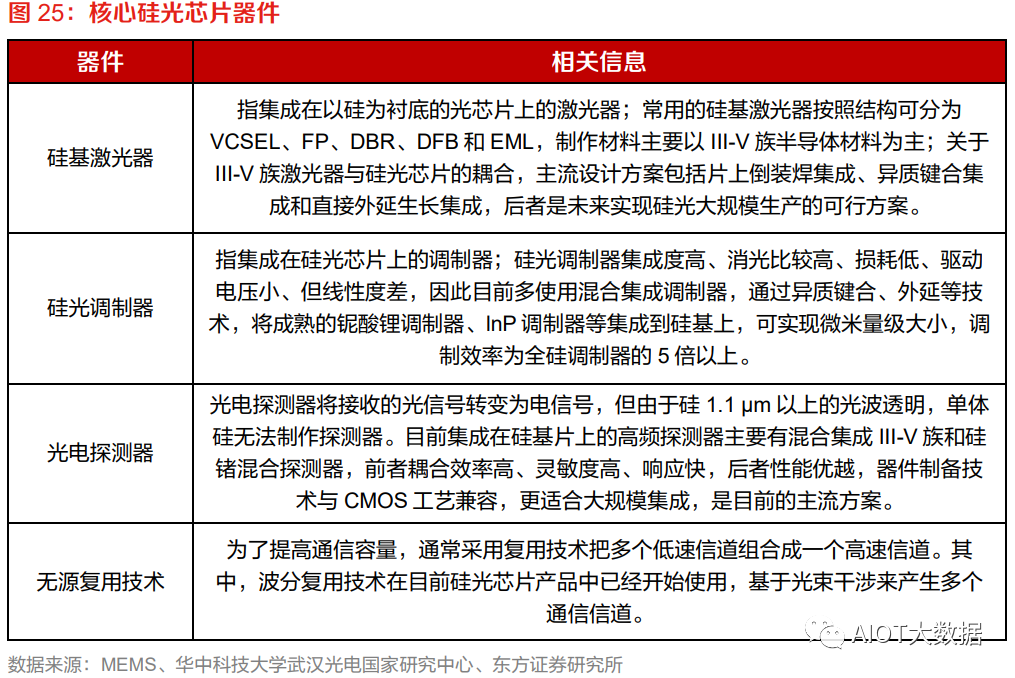

“以光代電”,硅光模塊對比傳統光模塊在高速率領域具有高集成度、低成本、低功耗的顯著優勢。硅是用量最大的半導體晶圓材料,具有低成本和加工工藝成熟的優勢。硅光基于硅和硅基襯底材料,通過CMOS工藝進行光器件開發和集成的新一代技術。硅光模塊產生的核心理念是“以光代電”,即利用激光束代替電子信號進行數據傳輸。普通光模塊采用分立式結構,光器件部件多,封裝工序較為復雜,從而需要投入較多人工成本,而硅光模塊由于芯片的高度集成,組件與人工成本也相對減少。在400G及以上的高速率的場景中,傳統DML和EML成本較高,硅光模塊成本優勢更為顯著。

硅光芯片中的光器件分為有源器件和無源器件。硅光芯片中的有源器件包括激光器、調制器和光電探測器;無源器件包括平面波導、光柵或邊緣耦合器等。基于這些元器件,可以構成光發射/接收芯片,并開展列陣化的應用,最終通過光子集成技術(PIC)來實現硅光芯片。其中,核心硅光芯片器件主要包括硅基激光器、硅光調制器、光電探測器、無源復用技術等。

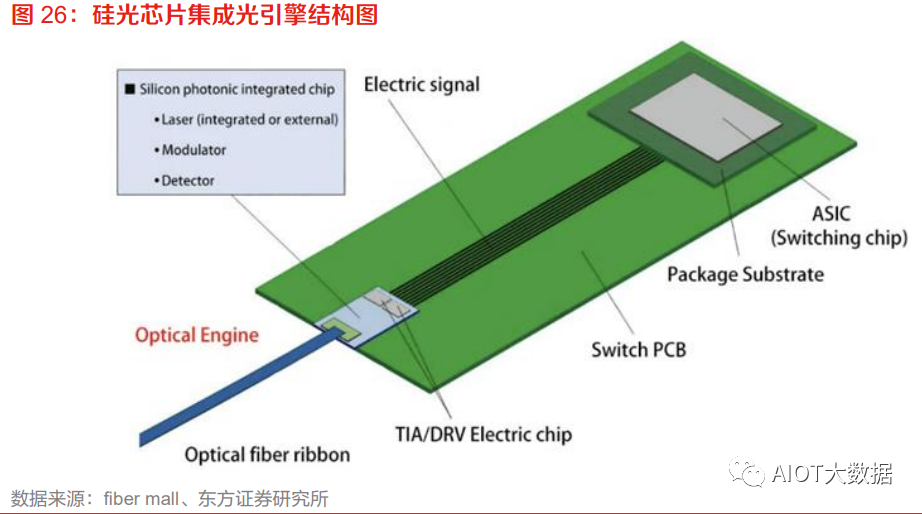

光引擎產品形態順應集成化發展規律。光引擎指的是光收發模塊中負責處理光信號的部分。而高速光引擎是高速光收發模塊的核心器件,在高速發射芯片和接收芯片封裝基礎上集成了精密微光學組件、精密機械組件、隔離器、光波導器件等,實現單路或者多路并行的光信號傳輸與接收功能。

硅光芯片集成高速光引擎趨勢確定性強。硅光技術將硅光模塊中的光學器件、電子元件整合到一個獨立的微芯片中,使光信號處理與電信號的處理深度融合,實現真正意義上的“光互聯”。硅光集成大規模應用之后,電芯片和硅光集成芯片與光纖連接,形成光引擎。相比分立器件光模塊,硅光器件不需要OSA封裝,具有低成本、高性能的優勢。向硅光芯片集成高速光引擎的發展趨勢是目前行業共識。

硅光及光引擎順應光模塊集成大趨勢,華工科技、源杰科技、立訊精密等廠商有所布局。

華工科技積極推進硅光技術應用,現已具備從硅光芯片到硅光模塊的全自研設計能力,800G硅光模塊已正式面市。源杰科技50G、100G高速率激光器芯片產品以及硅光直流光源大功率激光器芯片產品向商用推進,目標在高端激光器芯片產品的特性及可靠性方面對美、日壟斷企業的全面對標。立訊精密800G硅光模塊已在多家客戶完成測試,小批量交付正在準備中。

“相干下沉”+相干光鏈路空間可期

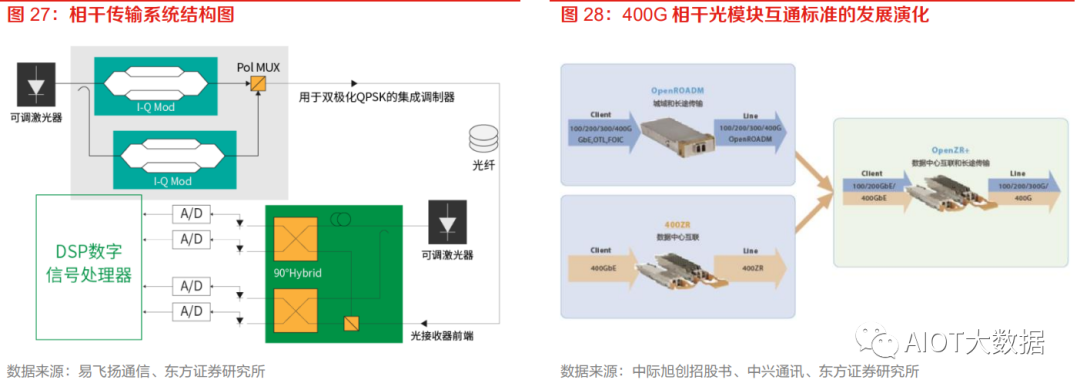

數據中心光互聯方案可根據其傳輸距離來選擇兩種支撐技術,直接探測技術與相干探測技術。隨著光模塊速率的不斷提升,直接探測方案的傳輸距離將受到限制,相干探測憑借著高容量、高信噪比等優勢得到廣泛應用。相干探測調制方式靈活、靈敏度強,適用于長距離傳輸。相較于傳統光接收機只響應光功率的變化,相干探測可探測出光的振幅、頻率、位相、偏振態攜帶的所有信息,并且取代傳統光復用技術的大頻率間隔,具有以頻分復用實現更高傳輸速率的潛在優勢。相干檢測能改善接收機的靈敏度,在相同的條件下,相干接收機比普通接收機提高靈敏度約20dB,可以達到接近散粒噪聲極限的高性能,因此也增加了光信號的無中繼傳輸距離。“相干下沉”+相干光鏈路需求提升驅動相干光通信市場增長。目前全球通信市場主要采用“相干下沉”的解決方案,相干技術從過去的適用于大于1000km的骨干網,逐步下沉到傳輸距離為100km到1000km的城域網,甚至小于100km的距離的邊緣接入網,以及80km至120km的數據中心互聯領域。在數通領域,相干技術也已經成為數據中心間互聯的主流方案。預計未來幾年相干光鏈路的用量將迎來井噴式增長。

相干光隨應用距離下沉,市場增量可期,華工科技、中際旭創等廠商有望受益。華工科技的相干光模塊產品在北美市場表現亮眼,推出了全球第一個400GZR+PRO產品,在發射光功率、接收靈敏度、光的性噪比方面優于業界水平。中際旭創擁有長距離傳輸功能的相干光模塊產品,助力“東數西算”工程和算力樞紐建設。

薄膜鈮酸鋰調制器有望借勢破局

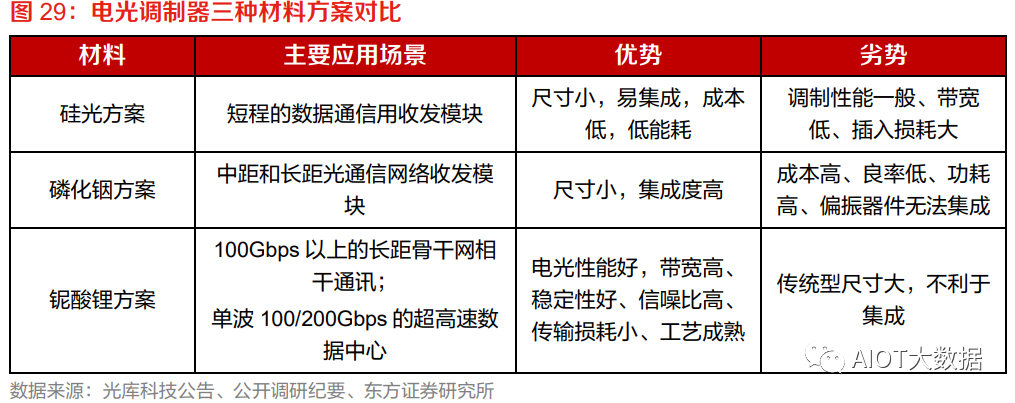

電光調制器是超高速數據中心和相干光傳輸的核心光器件,體材料鈮酸鋰具備優勢。電光調制器通過調制將通信設備中的高速電子信號轉化為光信號,是光通信系統中不可或缺的一環。目前光調制的技術主要基于硅光、磷化銦和鈮酸鋰三種材料平臺的電光調制器。其中鈮酸鋰電光系數顯著高于磷化銦,而硅沒有直接電光系數,因而鈮酸鋰調制器是大容量光纖傳輸網絡和高速光電信息處理系統中的關鍵器件。

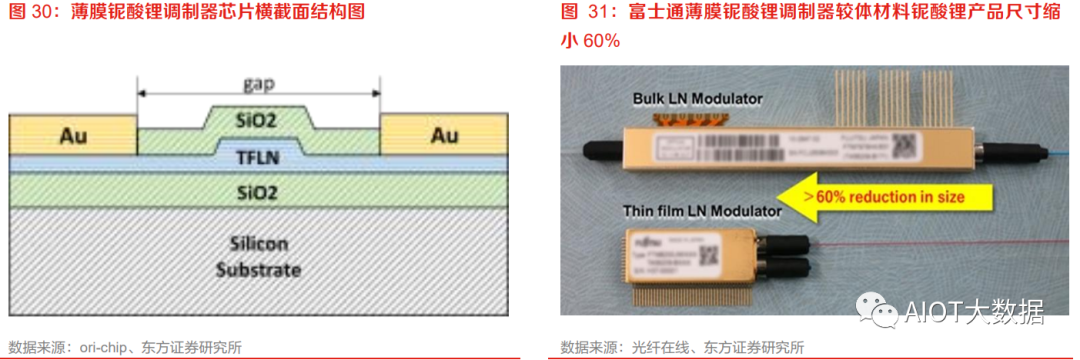

薄膜鈮酸鋰調制器芯片突破原有瓶頸,具有性能高、尺寸小、成本低的特性,有望成為高速光互聯新寵。新一代薄膜鈮酸鋰調制器芯片技術將解決尺寸大不利于集成的問題。鈮酸鋰材料通過新型微納工藝,在硅基襯底上蒸鍍二氧化硅(SiO2)層,將鈮酸鋰襯底高溫鍵合構造出解理面,最后剝離出鈮酸鋰薄膜。該工藝下制備出的薄膜鈮酸鋰調制器芯片具有高性能、低成本、小尺寸、可批量化生產且與CMOS工藝兼容等優點,是未來高速光互連極具競爭力的解決方案。

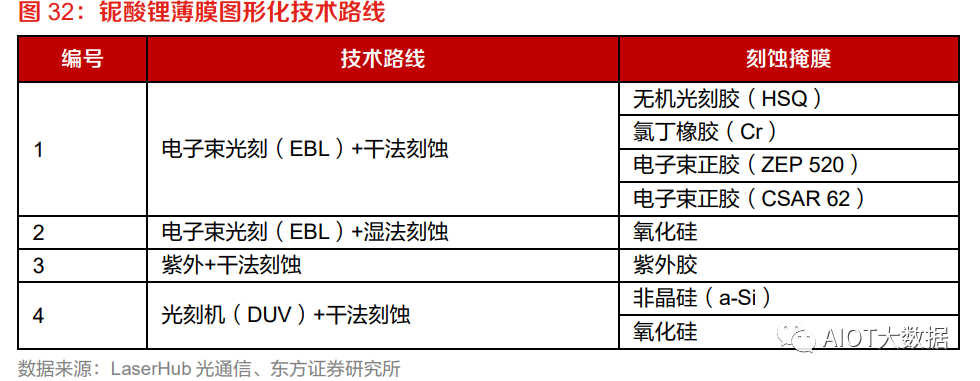

薄膜鈮酸鋰調制器芯片的關鍵制備技術為鈮酸鋰薄膜的圖形化。鈮酸鋰單晶薄膜相對較硬,組分特殊,難以刻蝕。目前已公開的鈮酸鋰薄膜圖形化技術路線中,主要包括電子束光刻(EBL)+干法刻蝕/濕法刻蝕、紫外+干法刻蝕、DUV+干法刻蝕四種。其中,相對于濕法刻蝕,干法刻蝕對薄膜鈮酸鋰的形貌和刻蝕速率的可控性更高,運用EBL+干法刻蝕的路線能夠充分發揮電子束光刻加工精度高、版圖設計靈活、無需掩膜版直接曝光等優點。

薄膜鈮酸鋰技術壁壘高,行業先發優勢或成卡位關鍵。電信級鈮酸鋰高速調制器芯片產品設計難度大,工藝非常復雜。根據智研咨詢數據,全球主要批量供貨體材料鈮酸鋰調制器的企業為富士通、住友和光庫科技三家。而薄膜鈮酸鋰在此基礎上通過上下分布二氧化硅壓縮光斑,拉近電極的距離,提高電場、射頻帶寬,技術壁壘再上一個臺階。目前在薄膜鈮酸鋰領域已有布局的廠商或可保持先發優勢,深度收益于超高速率電光調制器需求提升。

薄膜鈮酸鋰調制器產業鏈有望借勢打開局面,福晶科技、光庫科技等廠商具備關鍵核心能力。福晶科技是全球非線性光學晶體龍頭,開展獨立自主研發,能夠提供各種規格高質量的鈮酸鋰晶體,相關產品已成功推向Lumentum等光器件廠商。光庫科技在2019年收購Lumentum的鈮酸鋰高速率調制器生產線進入該領域,掌握了包括芯片設計、芯片制程、封裝和測試等核心技術,具備開發800G及以上速率的薄膜鈮酸鋰調制器芯片和器件的關鍵能力。

AI算力需求增長趨勢確定,預計直接提升高速率光模塊產業鏈市場增量,光芯片作為光模塊的核心器件有望深度受益,看好其在國產替代和技術創新趨勢下的表現。光賽道技術領先的供應商直接受益于市場增量,對于產業發展趨勢更具話語權。

1)光芯片領域有較強國產替代預期,建議關注源杰科技、華工科技、長光華芯、華西股份;

2)薄膜鈮酸鋰調制器芯片作為一種新的光電調制方式,有望成為高速光互聯更優解決方案,建議關注福晶科技、光庫科技;

3)MicroTEC是目前高速率光通信領域實現精準控溫的優質方案,建議關注富信科技。

來源:東方證券

什么是CPO?

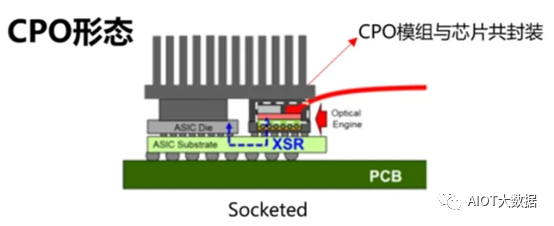

CPO,英文全稱Co-packaged optics,共封裝光學/光電共封裝。CPO是將交換芯片和光引擎共同裝配在同一個Socketed(插槽)上,形成芯片和模組的共封裝。

為了盡可能地降低網絡設備的自身工作功耗以及散熱功耗,在 OIF(光互聯網絡論壇)的主導下,業界多家廠商,共同推出了?——NPO / CPO 技術。

NPO,英文全稱 Nearpackaged optics,近封裝光學。

CPO,英文全稱Co-packaged optics,共封裝光學。

?

NPO / CPO 是將網絡交換芯片和光引擎(光模塊)進行“封裝”的技術。

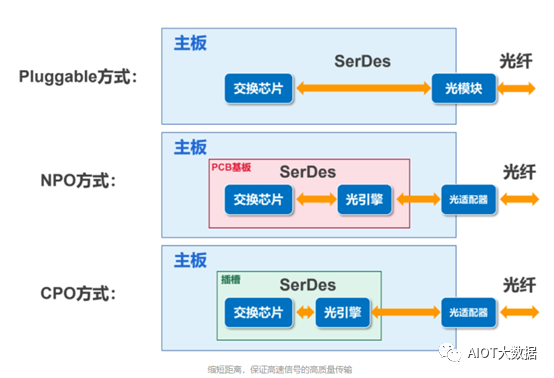

傳統的連接方式,叫做 Pluggable(可插拔)。光引擎是可插拔的光模塊。光纖過來以后,插在光模塊上,然后通過 SerDes 通道,送到網絡交換芯片(AISC)。

CPO 呢,是將交換芯片和光引擎共同裝配在同一個 Socketed(插槽)上,形成芯片和模組的共封裝。

NPO 是將光引擎與交換芯片分開,裝配在同一塊 PCB 基板上。

大家應該能看出來,CPO 是終極形態,NPO是過渡階段。NPO 更容易實現,也更具開放性。

之所以要做集成(“封裝”),目的很明確,就是為了縮短了交換芯片和光引擎間的距離(控制在5~7cm),使得高速電信號能夠高質量的在兩者之間傳輸,滿足系統的誤碼率(BER)要求。

NPO / CPO 技術的背后,其實就是現在非常熱門的硅光技術。

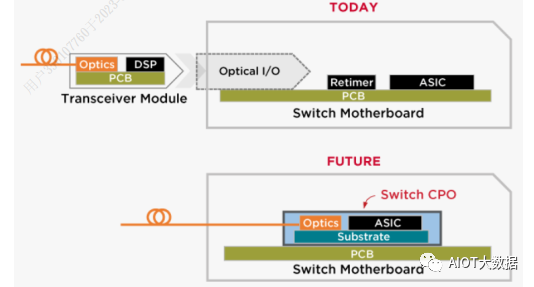

CPO的技術路線演化圖

CPO就是將交換芯片和光引擎共同裝配在同一個插槽上面,因此就形成了芯片和模組的共封裝,相較于傳統方案(可插拔光模塊模塊插在交換機前面板),CPO能縮短交換芯片和光引擎的距離,在提升集成度的同時降低功耗。

CPO示意圖

通過這種技術路徑,可以減少能量轉換的步驟,進而降低功耗。有報道甚至指出,相較于可插拔的光模塊,CPO的架構直接可以把功耗下降一半。再進一步說,超高算力背景下光模塊數量過載問題就有望得到解決。除了降低功耗之外,它也大大減小了光模板的尺寸、減小了電信號的延遲和失真。同時是不少投資者最為關心的成本。因為可以減少芯片與光模塊之間的連接器數量,這樣這一塊的成本就可以直接省略了,而且低功耗也同時意味著低成本。

此外,如果按照AIGC產業鏈劃分來看,CPO屬于上游的算法、算力層面。當前大算力應用場景的快速發展將加速推動光模塊從800G向1.6T演進,傳統的插拔光模塊的功耗問題就會逐漸顯露,CPO的作用就可以顯現。

從政策層面來看,高層對于6G技術的研發推進可謂全力支持。6G相較于5G本質上在速率、時延等方面都有著數量級級別提升的要求,進一步就意味著對光通信的傳輸速率有了更高要求,所以CPO也可以說是6G的好幫手。

目前光芯片已經形成了美中日三足鼎立的局面,只是美國在高端光芯片領域的優勢更為明顯,國內玩家也在奮起直追。比如源杰科技(688498)就已經構建了IDM全流程自主可控業務體系,2020年10G、25G激光器芯片系列產品的出貨量在國內均排名第一。

整體來看,25G光芯片的國產化率大約只有20%左右,25G以上的光芯片國產化率還不到5%,所以越往金字塔尖走,能看到自主品牌的玩家就越少。但換個方向想,這也是未來國產替代的主戰場。

所以,據專業機構的報告,預計2027年CPO整體市場收入將達到54億美元,上游的CPO光學組件將在三年后超過13億美元。CPO配套硅光有望在未來2-3年快速放量。

共封裝光學器件?(CPO):現狀、挑戰和解決方案

作者:譚敏1,2·姜旭3,4,5·劉思陽6??·馮俊博6??·張華7??·姚朝南7??·陳世熙3??·郭航宇8??·韓更始8??·溫占豪8?·?鮑辰8·余賀8·鄭旭強8??·大明1·涂耀文1??·付強1?·?南琦9??·李丹10·李庚10·宋文8??·楊鳳和11·何慧敏8??·劉鳳滿8??·薛海云8??·王宇航1??·邱慈元12·米光燦13·李彥博13·天海常13·賴鳴徹14·張羅14·郝沁芬15·秦夢遠15

摘要:5G、物聯網、人工智能和高性能計算應用的興起,數據中心流量以近30%的年復合增長率增長。此外,近四分之三的數據中心流量駐留在數據中心內。

傳統的可插拔光學器件的增長速度比數據中心流量的增長速度慢得多。應用要求與傳統可插拔光學器件的能力之間的差距不斷擴大,這是一種

不可持續的趨勢。光學協同封裝(CPO)??是一種顛覆性的方法,通過先進的封裝以及電子和光子學的協同優化顯著縮短電氣鏈路長度,從而提高互連帶寬密度和能源效率。? CPO被廣泛認為是未來數據中心互連的有前途的解決方案,而硅平臺是最有希望實現大規模集成的平臺。領先的國際公司(如? Intel、Broadcom ?和? IBM)對 C PO ?技術進行了大量研究,這是一個涉及光子器件、集成電路設計、封裝、光子器件建模、電子光子協同仿真、應用程序和應用程序的跨學科研究領域。標準化。

1簡?介

共同封裝光學器件(CPO)的重要性。隨著人工智能和高性能計算(HPC)??等數據密集型應用的擴展,數據中心流量不斷增長。傳統的可插拔光學器件無法滿足快速增長的帶寬密度和能效要求。共封裝光學器件?( CPO)??結合了光子器件通過先進封裝與高性能電子器件形成解決方案,可顯著縮短? SerDes 距?離,從而大大降低功耗。

目標和組織。本文的主要目的是概述? CPO ?的最新進展,并確定主要挑戰及其潛在解決方案。值得注意的是,對于這樣一個快速發展的領域,本文的內容絕非詳盡無遺。為了向讀者提供全面的概述,我們將本文分為十二個獨立的部分。在這里,我們簡要概述了這些部分。?2.器件制造。需要為? CPO ?開發先進的制造工藝和器件結構。以? 3D ?集成? CPO ?的形式,硅光子芯片用作中介層,以實現更短的走線和更低的功耗。此外,標準硅光子制造技術必須與封裝開發相配合。

3.外?部激光源。分析了對激光芯片的需求。事實證明,高功率激光器和? TEC ?是主要貢獻者。提出了降低激光功耗的潛在解決方案。

4.光功率傳輸。在最近的提案中,光功率傳輸系統經常被過度簡化甚至被忽略。本節試圖從三個方面解決光功率傳輸中的基本問題,具體而言,功率需求如何增長、需要哪些技術以及主要挑戰是什么。

5.C PO ?的DSP。? DSP芯片在CPO中起著重要的作用。本節總結了主機端和線路端鏈路的電氣要求,并提供了 D SP ?設計注意事項,包括收發器架構、時鐘方案和均衡實現。

6.用于? CPO?的基于微環的發射器陣列。微環形調制器具有面積小、功率效率高、兼容波分復用等優點,是CPO的有希望的候選者。然而,它面臨許多挑戰,例如波長控制和偏振靈敏度。本節總結了基于微環的收發器陣列的挑戰和最新進展,并提供了應對這些挑戰的建議。

7.基于? Mach–Zehnder ?調制器(MZM)的? CPO 發?射器。? MZM ?已經商業化,是替代現有可插拔光學模塊的有前途的解決方案。然而,MZM 驅?動器設計在電壓擺幅、帶寬、能效和其他方面提出了許多挑戰。本節概述? MZM 發?射器,重點介紹其驅動器設計。

8.CPO ?的光接收器前端。與BiC M OS相比,基于CMOS的光接收器在集成度、功率效率和成本方面更兼容CPO。本節將提供基于? CMOS ?的光接收器前端電子 I C ?設計的最新進展,有望為 C PO ?的未來全集成電子 I C ?鋪平道路。

9.C?PO??的2.5D??和3D??封裝。? 2.5D、3D封裝技術可為CPO實現高帶寬、高集成度和低功耗。本節主要討論IMECAS研發的2D/2.5D/3D 硅光子共封裝模組,2D ?MCM光子模組。封裝問題,以及硅光子晶圓級封裝的挑戰。

10.CPO 的電子?光子聯合仿真。電子?光子協同仿真是大規模電子?光子協同設計的先決條件。然而,這個領域相對不成熟,面臨著許多方法和工程方面的挑戰。主流方法是將光子器件集成到電子設計?動化平臺中。本節主要討論光子器件建模、時域仿真和頻域仿真的挑戰和解決方案。

11.HPC 光子互連的系統考慮。本節將光子互連鏈路分解為硬件和軟件組件,相應地討論它們的當前狀態、挑戰,以及它們如何影響光子鏈路和網絡的完整性。最后,本節評論了? HPC ?網絡光子互連未來的下一個里程碑。

12.HPC中的光電混合接口。出于兼容性方面的考慮,HPC 一?直不愿轉向新技術。迄今為止,光電混合集成未能真正發揮集成優勢。本節分析了? CPO ?的不同互連設計考慮因素,并為加速 C PO?在 H PC ?中的適配提供了建議。

13.CPO ?開發和標準化。中國計算機互連技術聯盟??(CCITA)?協?調學術界和工業界的努力,啟動了中國? CPO ?標準化工作。本節概述了中國原棕油標準化工作的技術和經濟考慮。

2先?進的硅光子制造CPO技術

2.1現狀,光學共封裝??(CPO)??是一種先進的光電器件封裝技術,涉及系統架構、芯片制造和封裝的升級。在本節中,我們將主要討論用于? CPO 應?用的硅光子芯片的制造技術。摩爾定律是微電子芯片制造中眾所周知的現象。在過去的幾十年里,每個芯片的晶體管數量每兩年翻一番。同樣,號稱受益于硅光子學的從現有和成熟的互補金屬氧化物半導體??(CMOS)?制?造技術來看,也應該遵循這種縮放趨勢,并通過規模經濟實現光子集成電路??(PIC)?的?低成本制造??[25]?。然而,與電子設備不同,光子設備的縮放在本質上是困難的。光子器件的尺寸主要由材料的折射率對比決定。硅光子器件的全球尺寸仍停留在微米級,很少會縮小到納米級。因此,當我們談論硅光子學的縮放時,我們是在談論先進的制造技術如何實現光子封裝的縮放。

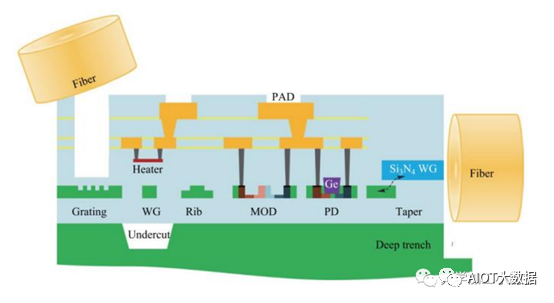

2.2當前和未來的挑戰臺積電、Global?Foundry、Tow ?erJazz、中芯國際等純晶圓代工廠和IMEC、AMF、AIM、CUMEC等開放式中試線正在提供硅光PDK,包括無源和有源器件的基礎組件庫,如如圖? 1 ?所示。雖然? CPO 應?用需要定制結構,但 C PO ?芯片的主要制造挑戰來?光纖耦合和光源集成。極高密度的光學? I/O ?需要高效的光纖耦合結構。耦合結構有兩種,光柵耦合器和邊緣耦合器。光柵耦合器通常通過簡單的兩步蝕刻工藝制造,從而實現垂直光耦合。光柵耦合器具有相對較寬的對準公差、較小的光學帶寬和較高的偏振靈敏度。因此,與邊緣耦合器不同,光柵耦合器通常用于晶圓級測試而不是商業產品。邊緣耦合器可實現較小的耦合損耗和較大的光帶寬,這對于實際應用來說是理想的。

然而,邊緣耦合器在制造過程中需要底切和深蝕刻工藝,從而導致器件穩定性和可靠性方面的問題。此外,開發了V 形槽結構用于光纖邊緣耦合的被動對準[26]。

片上光源集成是硅光子學的主要挑戰之一。硅基材料本身就很難形成高性能激光器。III?V族化合物材料在硅光子芯片上的異質集成或異質結構集成被證明是一種可行的方法,但硅光子制造工藝需要進行重大調整。

未來,從2 .5D ?CPO 到? 3 D ?CPO,CPO ?技術將不僅僅是一種封裝工藝,而是一種制造和封裝的結合,需要設計和工藝的共同優化。封裝概念需要與制造工藝流程深度融合。

圖1CUMEC硅光子PDK原理圖

2.3科?技進步迎接挑戰在大多數當前的CPO ?解決方案中,邊緣耦合器用于光入和光出路徑。邊緣耦合器經過精心設計,可同時滿足高對準公差和低插入損耗的需求。通過使用? V ?型槽結構的無源對準,典型的光纖到芯片損耗可以控制在?-1.5 ?dB ?以內[27]。使用熱移相器等結構有助于進一步提高對準容差

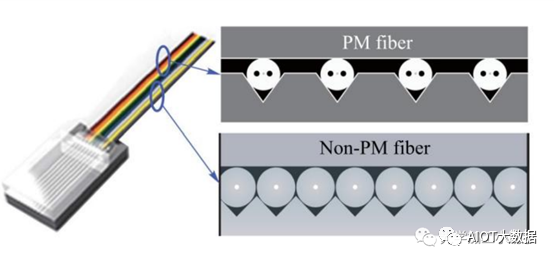

[28]。硅光子收發器是高速開關組件CPO?系統的重要組成部分,其中多個收發器模塊緊靠開關? ASIC 排?列。如圖? 2 ?所示,中央交換機? ASIC ?被成百上千個混合有保偏??(PM)??光纖和非保偏光纖的光纖所包圍,這對光纖布線和封裝的一致性和質量提出了相當大的挑戰。采用高階調制技術,片上光源集成,減少光纖數量,降低光纖封裝難度。

此外,波分復用方案或TeraPHY [ 29]可能是解決更大數據流的另一種解決方案。

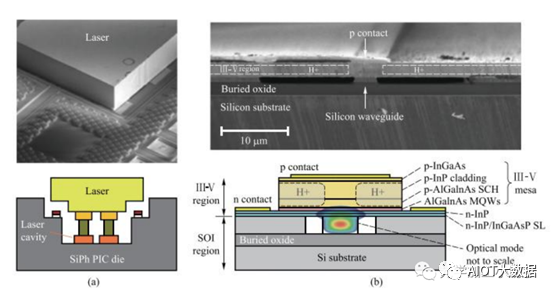

片上光源集成方法包括異質結構集成(例如激光二極管倒裝芯片鍵合)和異源集成(例如,晶圓級材料鍵合)(圖3)。

對于倒裝芯片接合方法,商用激光二極管通過共晶焊接接合在硅光子芯片上。

機械擋塊和基準標記用于激光芯片和硅光子芯片之間的高精度被動對準[33]。該方法利用成熟的激光二極管產品簡化開發和快速商業化。對于晶圓級材料鍵合方法,激光器是在硅光子芯片制造過程中一起形成的

[31?33]。III?V材料和硅波導之間的模式轉換器需要在生產線的前端進行工藝修改。激光電極制造導致后端工藝改變線。總體而言,硅光子生產線需要大規模改造以實現異質集成。對于這兩種方法,未來在? CPO 中?的應用都需要考慮散熱和應變引起的性能退化。

圖2用于光輸入的保偏光纖和用于光輸出的非保偏光纖的混合封裝

圖3a??Heterostructure??integration??[30]和b??heterogeneous??integration??[33]??of??on?chip?l?ight??source

?

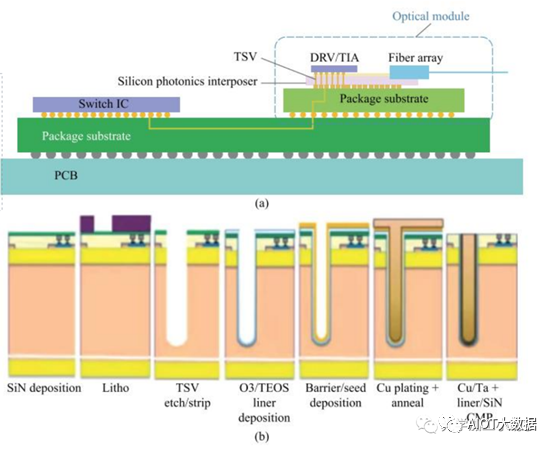

圖4使用具有? TSV?結構的硅光子中介層的混合組裝光學模塊[10]。b 硅光子中介層上的 T SV ?制造工藝[35]

以3 D ?集成?CPO 的?形式,硅光子芯片用作中介層,可縮短電路連接并降低功耗。最近,imec 展?示了一種嵌入硅通孔??(TSV)??結構的混合組裝光學模塊,射頻帶寬達到? 110? GHz 以?上,為下一代以 1 00Gbaud ?數據速率運行的硅光子模塊鋪平了道路,如圖? 1 所?示。? 4 ?[34]。在硅光子芯片上制造? TSV ?需要額外的工藝,包括高縱橫比博世深蝕刻和晶圓減薄,這會在產量和可靠性方面引發潛在問題??[35]?。

2.4結?束語順應集成化趨勢,標準硅光子制造技術必須適應封裝的發展。為了滿足CPO的要求,需要為硅光子學開發先進的制造工藝和器件結構。? CPO?應用程序設計人員與代工廠密切合作以實現設計流程協同優化會更加高效。

3用?于共同封裝光學器件的外部激光源

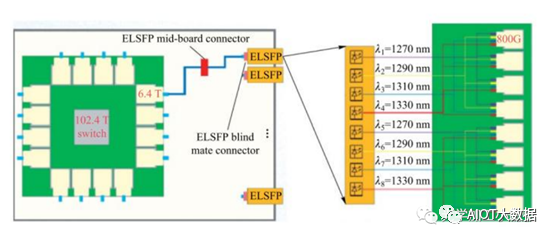

3.1現狀激光源是協同封裝光學器件??(CPO)??的使能技術之一。在基于硅光子學的光學引擎的背景下,正在討論和開發兩種類型的激光源,即片上激光器和外部激光器。每種方法都有其優點和缺點。本期側重于外部激光源??(ELS)??的選項,這主要是由于其更廣泛的行業可及性。據信,當數據中心網絡?( DCN)??應用的交換容量達到? 102.4 T bit/s?時,光連接將更有可能演變成? CPO 形?式。1 02.4 ?Tbit/s 交?換機需要具有 6 .4 T bit/s ?光輸入/輸出容量的? CPO t ile,如圖? 5 ?所示。

圖5??102.4??T??共封裝光學器件配置

6.4T bit/s C PO ?tile ?的實現方法仍在討論中,例如每通道數據速率和并行或? WDM 架?構。為便于討論,假設6.4 ?Tbit/s ?CPO t ile由8組800? Gbit/s c ell組成,由4×200Gbit/s ?FR4 ?配置。每個? 6.4?Tbit/s C PO ?塊都需要一個? ELS。如圖5 所示,每個ELS封裝由兩組CWDM4激光器組成,即總共8個激光器。每個激光芯片通過使用? 1×4 ?分離器為多達四個? 800 G bit/s ?電池供電。

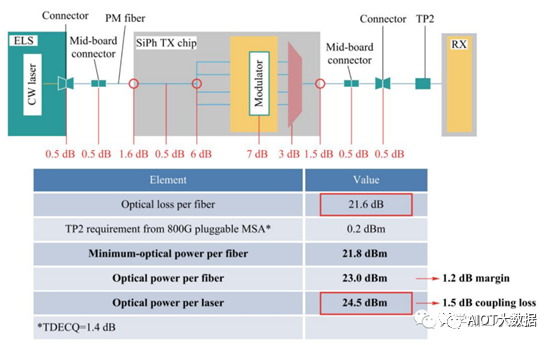

3.2當前和未來的挑戰輸出功率和功耗是?ELS 的?關鍵特性。E LS的輸出功率需求可以從光引擎的鏈路預算分析中推導出來。

表1顯示了輸出功率的鏈路預算分析。根據?800G ?FR4 [ 72]的規范,假設光引擎所需的最小輸出功率(在? TP2)為??0.2 d Bm 。硅光子芯片的總插入損耗為?21.6 d B,如表? 1 所?示。因此,ELS 封?裝所需的最小輸出功率為? 21.8 ?dBm。在考慮激光器與光纖的耦合損耗并留有余量的情況下,要求激光器芯片的輸出功率為24.5dBm。

表1?.光學引擎的鏈路預算分析

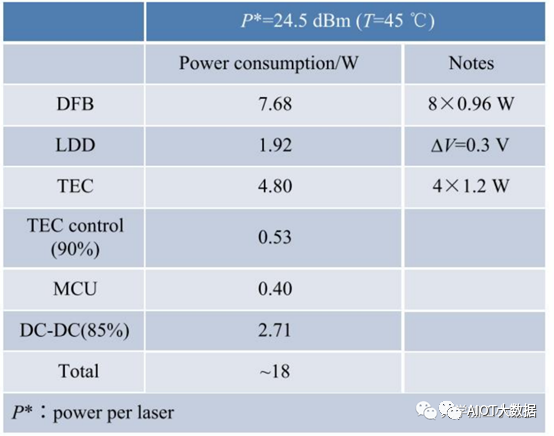

表2E?LS封裝的總功耗

ELS封裝的功耗是另一個關鍵參數。表2 顯示,用于? 6.4 T bit/s ?CPO 的?? ELS ?封裝的總功耗約為? 18?W。激光芯片和熱電冷卻器占總功耗的近 7 0%。

激光芯片的高輸出功率是造成大部分功耗的根本原因。激光芯片的電光轉換效率對功耗至關重要,定義為光輸出功率與消耗的電輸入功率之比。墻插效率表2 中?使用的功率約為??0.3,這意味著只有 3 0%??的電輸入功率可以轉換為光輸出功率,而剩余的功率則以熱量的形式耗散掉。此外,熱電冷卻器??(TEC)??消耗額外的電能來散發激光芯片產生的熱量。? 102.4Tbit/s交換機所需的16個ELS的總功耗為288W。

OIF[73]正在對 E LS 的?外形規格進行標準化,包括電氣和光學接口、封裝、管理接口等。

3.3科技進步迎接挑戰1、輸出功率大。現有的為可插拔收發器開發的CW激光器不能滿足CPO應用的高輸出功率要求。基于硅光子學的可插拔光收發器,例如? 400G ?DR4,通常需要輸出功率小于?100? mW 的?? CW ?激光器。相比之下,CPO 應?用需要更高的?CW ?激光器輸出功率。如表? 1 ?所示,所需的輸出

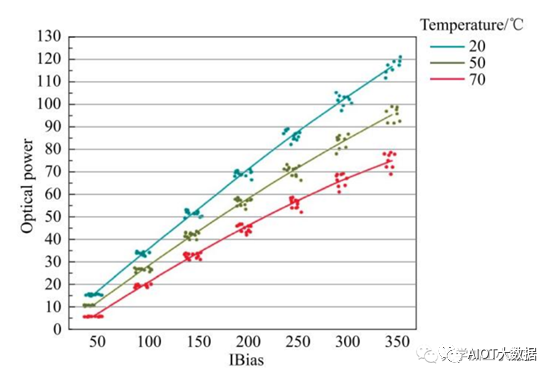

圖6高功率激光器性能

對于WDM ?架構,激光芯片的功率為 2 86 ?mW。盡管? DR ?架構的輸出功率要低得多,但至少仍需要 1 00? mW。對于工業應用,已報道了 C /C+?波?段的平板耦合光波導? DFB ?激光二極管,其無扭結 C W ?輸出功率超過? 100 m W ?[74]。然而,在? O 波?段,我們開發了一種? 1310? nm ?CW ?激光器,它在?50°C 時?只能達到 8 0? mW,如圖 6 ??所示。據報道,CWDM4 ?激光器的輸出功率僅為? 70? mW?左右?[ 75 ]?。因此,需要開發用于? CPO ?應用的高功率激光器。

2.插墻效率高。除了高輸出功率外,從能量效率的角度來看,高電光轉換效率是高功率? CW ?激光器的另一個理想特性。此外,熱效率高的TEC有助于降低ELS功耗。此外,非制冷高功率激光器可能是? CPO ?光源的最終解決方案。

3.單?片集成。硅光子平臺工藝已經很成熟,并且比? CMOS ?和??BiCMOS平?臺具有更高的整體傳輸和接收性能,但激光集成仍然是所有硅平臺和活躍研究主題的挑戰。在Si ?平臺上單片集成? III?V 激?光器之前的主要挑戰是由于材料差異導致的器件性能受損。最近,單片生長在? Si 襯?底上的?III?V ?QD ?激光器已經展示了非常有前途的結果,具有長壽命、高輸出功率和低閾值電流密度。然而,為了在? SOI 平?臺上實現? QD ?激光器的單片集成應用,必須解決與波導的光耦合問題。相比之下,基于 I nP ?的平臺可以輕松集成活性材料,依賴更強的電光??(EO)?克?爾和普克爾斯效應,并實現更高的? EO ?帶寬效率指標。可以實現? EO ?效應的進一步增強,與量子阱中的量子限制斯塔克效應,但以更高的溫度和波長依賴性為代價。

外部激光源是? CPO 光?源的有前途的解決方案

由于其易于維護和廣泛的可及性,外部激光源是? CPO 光?源的有前途的解決方案。? OIF ?中的? ELS ?標準化正在進行中,將加速該技術的成熟。需要具有至少 1 00mW?輸出功率的高功率? CW ?激光器來滿足鏈路預算要求。? CW ?激光器的電光轉換效率需要進一步提高以達到節能目的。外部激光源的單片集成得益于更小的寄生電容和更低的封裝成本,使其成為在硅芯片上實現可靠、節能、高密度激光二極管集成的最有前途的解決方案。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論