?

繼今年稍早宣布投入開發(fā) 3D IC 標準后, JEDEC 表示,最快今年12月底或明年一月初,將可公布首個 3D IC 接口標準。

在GSA的3D IC工作小組于上周舉行的會議中,英特爾(Intel)的Ken Shoemaker介紹了關于 WideIO 內存規(guī)格在電子和機械接口方面的細節(jié)。

JEDEC已開始釋出3D IC標準──在2009年11月,該機構便公布了針對采用硅穿孔(TSV)技術的3D芯片堆棧所制定的JEP158標準。而即將問世的WideIO標準,看來似乎可望在SEMI、Sematech和Si2等推動3D IC標準的競賽中取得領先。

業(yè)界人士普遍認為,LPDDR2的頻寬會在WideIO內存商用化以前便遭市場淘汰。而在此期間,預計LPDDR3 (即LPDDR2的下一代版本)將可支持更高的操作頻率,并提供比LPDDR2更低的功耗,以填補此一差距。800MHz的LPDDR3要比533MHz的LPDDR2多出50%以上的頻寬,但其接腳數(shù)卻與LPDDR2相當。

?

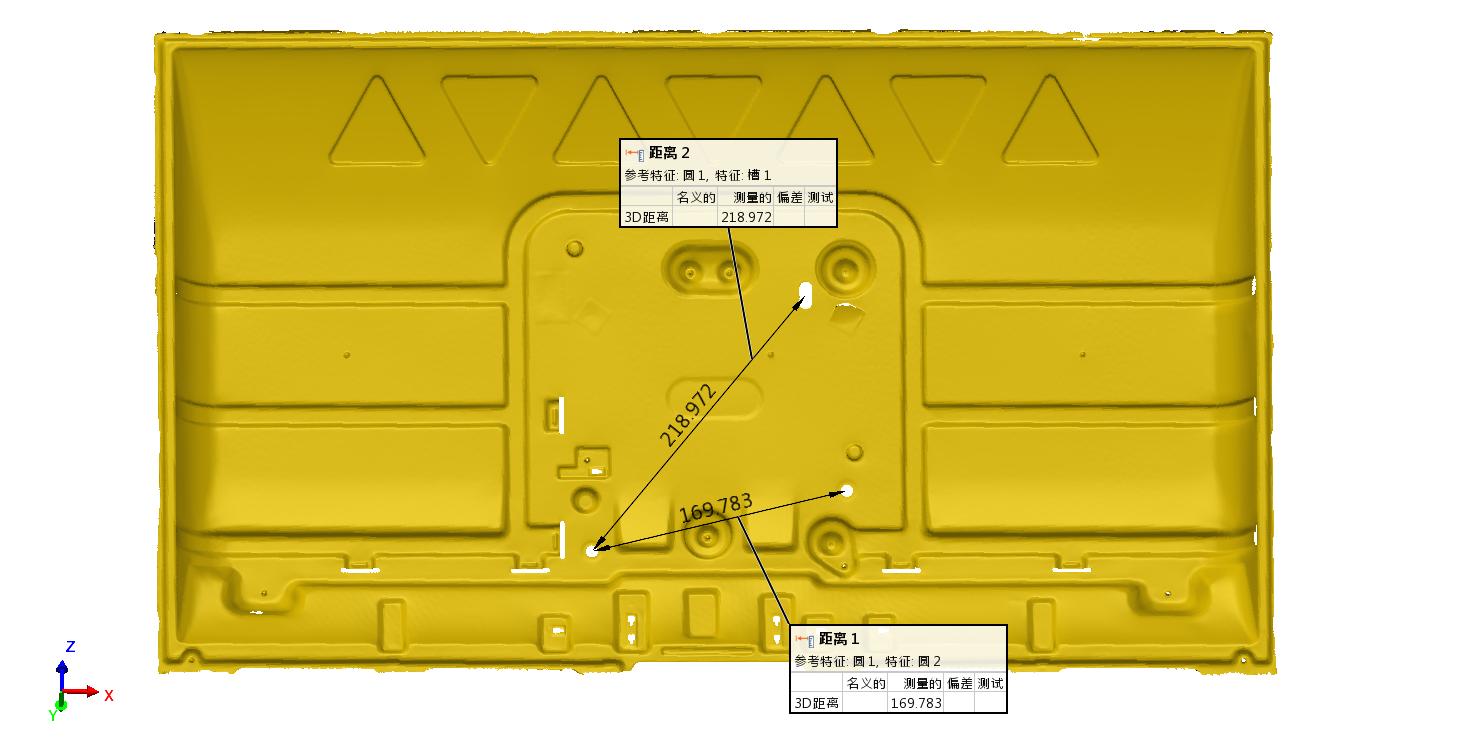

圖1:WideIO的市場定位。

WideIO是由JEDEC工作小組JC42.6于2008年12月著手開發(fā),主要是針對當前在同一封裝中整合邏輯和DRAM,以降低互連電容的3D標準所開發(fā)。即將公布的規(guī)格定義了最多4個晶粒堆棧而成的內存立方體,可連接邏輯SoC,最大封裝尺寸為10x10x1mm。

針對WideIO的JC42.6規(guī)范了邏輯到內存接口(logic to memory interface, LMI),是由JEDEC旗下JC42.6 (Low Power DRAM)和JC11兩個委員會所共同制定,其中JC11主要負責芯片封裝的機械標準部份。在內存邏輯和內存之間的機械接口一般稱之為微型圓柱門陣列(Micro Pillar Gate Array, MPGA)鏈接。

至于邏輯和內存之間的互連方式則并未指定,可以是微凸塊或微型圓柱(micro pillars)等。該標準還規(guī)范了用于測試互連連續(xù)性的邊界掃描、后組裝階段的直接存取內存測試、內存芯片中的熱傳感器位置,以及芯片到芯片間接口的精確機械布局等。

此一標準并未指定內存到邏輯的互連設計或組裝方法。同時無論在內存或邏輯芯片上,也都并未針對TSV的尺寸及位置指定互連的精確位置。另外,內存和邏輯芯片的厚度、組裝方法和后組裝測試方法也都未指定。

WideIO的詳細規(guī)格包括:

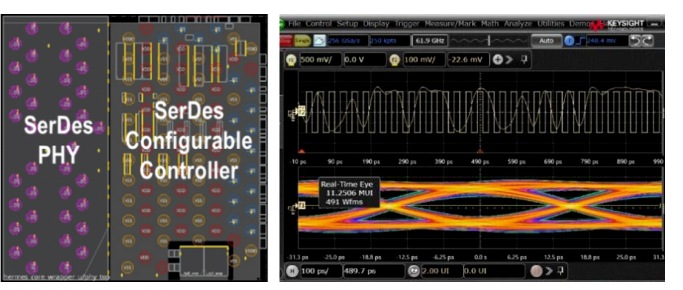

如圖2所示,WideIO定義了4個內存信道,在LMI上有1,200個連接:

- 每個通道都有6列和50行,共300個連接(193個訊號);

- 40nm的小型襯底/凸塊/TSV間距;

- 每信道寬128個數(shù)據(jù)位,總共512數(shù)據(jù)位;

- 每個通道均包含所有的控制、電源和接地通道

通道之間共享電源連接

- 每個通道均可獨立控制

獨立的控制、頻率和數(shù)據(jù)

- 信道之間的接腳地址對稱

- 數(shù)據(jù)傳輸速率266mtps,SDR

總頻寬:17GB/s(每通道4.26GB/s)

?

圖2:LMI界面細節(jié)。

WideIO的布局規(guī)劃(floor plan)同時描述了可在組裝中針對機械強度和晶粒的共面性選擇支持凸塊或微型圓柱。而兼容的底部填充膠則可用于減輕邏輯和內存晶粒之間的應力,同時將熱均勻地分布在晶粒表面上。也可以使用一個硅中介層(interposer)作為第四個晶粒與邏輯SoC連接的接口,以因應熱機械方面的挑戰(zhàn)。

?

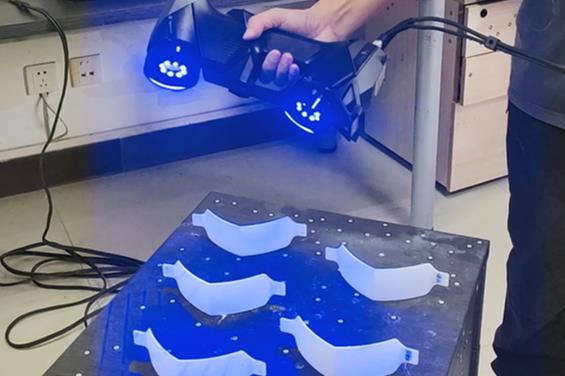

圖3:LMI接口的機械尺寸。

由于DRAM的自我刷新速率會隨溫度而變化,因此必須密切注意內存-邏輯堆棧的熱管理。為了提高產(chǎn)品可靠度,在邏輯芯片熱點和DRAM內的熱傳感器之間的溫度三角洲都必須設法最小化。由于其采用的制程不同,DRAM和邏輯SoC設計小組必須緊密合作,在制造‘堆棧’芯片時互相交流信息。這個設計小組可能必須要對熱點設計進行權衡,然而,這部份交換信息的方法卻由于JEDEC并未涉及而缺乏標準化。

三星的內存立方體

2011年2月,三星(Samsung)公布了首個用TSV實現(xiàn)的mobile DRAM,該內存帶有WideIO接口(鏈接),目前看來,該內存已經(jīng)符合了由JC42.6工作小組定義的JEDEC標準。事實上,三星也是JC42.6 WideIO工作小組的會員之一。

?

圖4:三星采用TSV實現(xiàn)的mobile DRAM,具備WideIO接口。

其晶粒面積為64.34mm2,比1GB的LPDDR2大了25%。整顆芯片是由4個對稱的4×64Mb數(shù)組、周邊電路和微凸塊所構成。為了降低功耗并支持高傳輸頻寬,該設計藉由采用44×6微凸塊襯底來減少I/O驅動器加載。其微凸塊尺寸20 ×17μm,間距250μm。該公司的TSV孔徑7.5μm,電阻值0.22~0.24Ω,電容值47.4fF。

三星并未公布其WideIO DRAM的可靠性資料。依目前生產(chǎn)TSV的成本結構來看,要制造WideIO接口的組件顯然更加昂貴,不過,這個問題或許可藉由大量生產(chǎn)來解決。長遠看來,該技術確實具備著降低成本及提供更高性能的潛力。

本文小結

對整合邏輯和內存的3D IC而言,首個針對WideIO的商用化標準至關重要。盡管技術上的創(chuàng)新從不停歇,但現(xiàn)階段在異質堆棧組件的設計團隊之間仍然缺乏可交換設計信息的標準。此外,降低成本和改善制程也是未來必須努力的主要方向。

電子發(fā)燒友App

電子發(fā)燒友App

評論