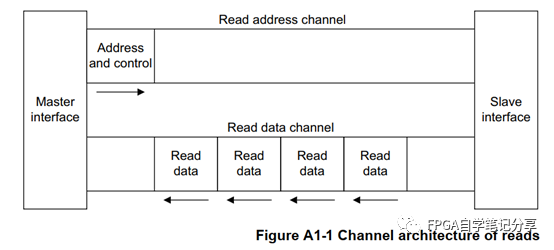

上文FPGA IP之AXI4協(xié)議1_信號說明把AXI協(xié)議5個通道的接口信息做了說明,本文對上文說的信號進行詳細說明。

1.時鐘和復位

每個AXI接口使用一個時鐘信號ACLK。所有輸入信號都在ACLK的上升沿上采樣,所有輸出信號的變化都必須發(fā)生在ACLK上升沿之后。在主接口和從接口上,輸入和輸出信號之間不能出現(xiàn)組合邏輯路徑。

AXI協(xié)議使用低有效的復位信號:ARESETn。復位信號可以異步使能,但是去使能必須與ACLK的上升邊同步。在復位信號被拉低后,接口信號要做以下動作要求:

?主端必須驅動ARVALID, AWVALID和WVALID 為低

?從端必須驅動RVALID和BVALID 為低

?所有其他信號都可以被驅動到任意值。

復位信號拉高后,主控制器被允許開始驅動ARVALID、AWVALID或WVALID 變高的最早時間點是在ARESETn為HIGH后的上升ACLK邊緣。

2.基本的讀寫操作

握手過程

所有五個事務通道都使用相同的VALID/READY握手過程來傳輸?shù)刂贰?shù)據(jù)和控制信息。這種雙向流控制機制意味著主端和從端都可以控制信息在主和從之間移動的速率。當?shù)刂贰?shù)據(jù)或控制信息可用時,源端生成VALID信號。目的地生成READY信號,表示它可以接受該信息。只有當VALID和READY信號都為HIGH時,才會發(fā)生傳輸。

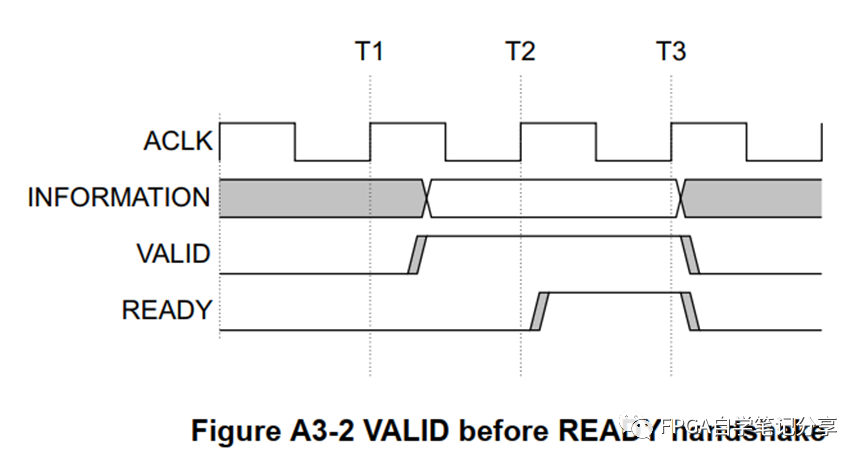

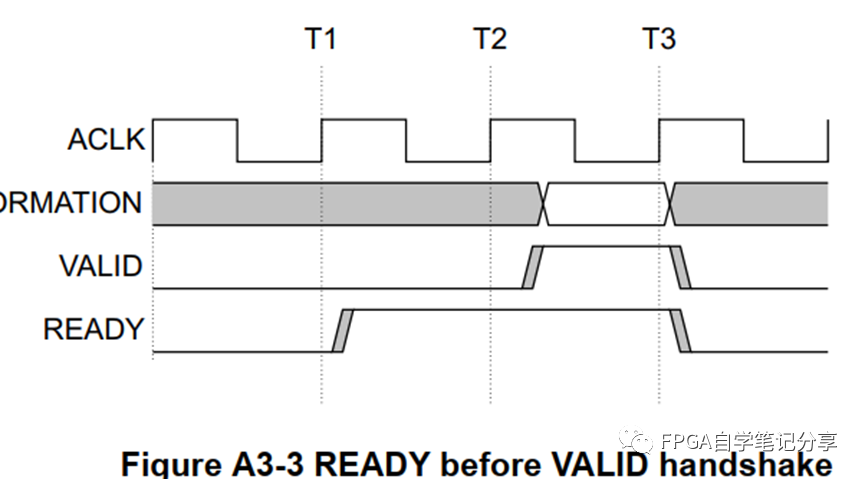

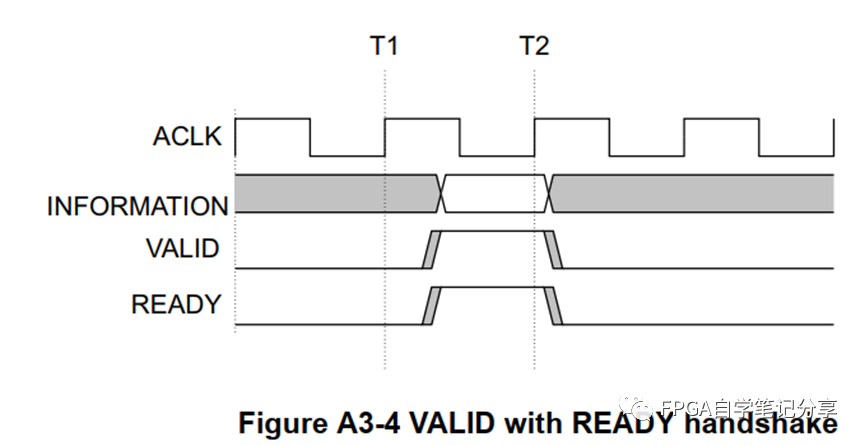

握手過程中的VALID/READY信號支持三種模式:VALID在READY之前、VALID在READY之后、VALID和READY同時到達:

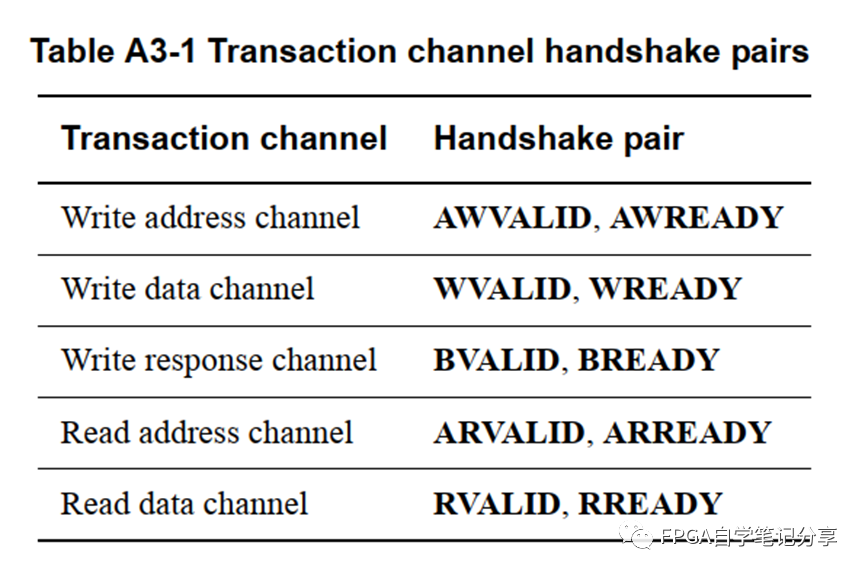

VALID和READY信號的握手過程是AXI協(xié)議最基本的要求,AXI協(xié)議5個通道均有自己的VALID和READY信號:

寫地址通道 :只有當主端準備好有效的地址和控制信息后AWVALID信號才會被拉高,并將持續(xù)為高保持到從端的AWREADY信號拉高后才會拉低。AWREADY信號的默認狀態(tài)可以是高或者低,協(xié)議推薦默認狀態(tài)為高,當AWREADY為高時,slave必須能夠接收有效的地址或者控制信號。(協(xié)議不推薦AWREADY信號默認狀態(tài)為0是因為,默認狀態(tài)為0時,完成一次握手至少需要2個clk才能完成)

寫數(shù)據(jù)通道 :只有當主端準備好有效的地址和控制信息后WVALID信號才會被拉高,并將持續(xù)為高保持到從端的WREADY信號拉高后才會拉低。同樣推薦WREADY信號的默認狀態(tài)為高。當進行一個burst的最后一次傳輸時WLAST信號要被置高。

寫響應通道、讀地址通道、讀數(shù)據(jù)通道的VALID和READY要求與上邊的相同。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605984 -

控制器

+關注

關注

112文章

16445瀏覽量

179433 -

接口

+關注

關注

33文章

8691瀏覽量

151911 -

信號

+關注

關注

11文章

2804瀏覽量

77098 -

AXI4

+關注

關注

0文章

20瀏覽量

8914

發(fā)布評論請先 登錄

相關推薦

看看在SpinalHDL中AXI4總線互聯(lián)IP的設計

SoC Designer AXI4協(xié)議包的用戶指南

AMBA 4 AXI4、AXI4-Lite和AXI4-流協(xié)議斷言用戶指南

AXI3與AXI4寫響應的依賴區(qū)別?

AXI4-Lite協(xié)議簡明學習筆記

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

漫談AMBA總線-AXI4協(xié)議的基本介紹

SoC設計中總線協(xié)議AXI4與AXI3的主要區(qū)別詳解

AMBA AXI4接口協(xié)議概述

FPGA AXI4協(xié)議學習筆記(三)

FPGA AXI4協(xié)議學習筆記(三)

評論