FPGA是非常有用的器件,通常與ADI公司的ADC或功率IC等一起設計到客戶的設計中。FPGA 可以實現微控制器和所需的任何膠水邏輯。在這篇博客中,我將討論一些與功能安全和FPGA相關的問題。

首先,什么是FPGA?FPGA(現場可編程門陣列)是一種集成電路,但它不是專用的片上邏輯,它由可重新配置的邏輯和通常包括 uC 的硬宏組成,例如 ARM Cortex 或 A9 系列(某些 uC 也提供 HDL/軟格式)。可重構邏輯通常采用邏輯塊數組的形式。FPGA制造商包括Xilinx,Altera(現為英特爾的一部分),萊迪思半導體和Microsemi。可重新配置意味著使用FPGA可以為您的硬件提供靈活性,這通常只能在軟件解決方案中找到,包括能夠快速更改“硬件”,如果使用分立IC將需要數周或更長時間,如果使用ASIC則需要幾個月的時間。但是,從安全的角度來看,這意味著您也會遇到一些令人頭疼的軟件問題。

對于某些FPGA,FPGA的配置存儲在片上閃存或EEPROM中,但對于較大的FPGA,則存儲在片外閃存中,并在啟動時加載到FPGA上的RAM中。FPGA上的可重構邏輯通常使用HDL(硬件描述語言)完成,例如Verilog或VHDL,它看起來非常像軟件(我必須將“Verilog軟件嗎?”添加到我即將發布的博客列表中)。

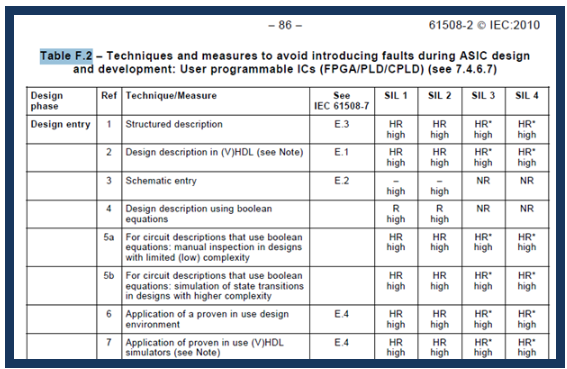

IEC 61508-2:2010的附錄F為在設計數字ASIC(表F.1)和FPGA(表F.2)時避免系統錯誤提供了指導。實際上,表 F.1 與設計 FGPA 芯片的人員相關,例如 Xilinx 或 Micro-semi 的工程師,表 F.2 與設計將在 FPGA 中實現的內容的客戶相關。

圖 1 - IEC 61508-2:2010 表 F.2 的摘錄

這兩個表都給出了類似的度量列表,根據 SIL 排名為 HR 或 R。HR 標準為強烈推薦,R 為推薦。R或HR的含義似乎被不同的人有不同的解釋,但對我來說,這意味著如果一個問題被標記為“R”,你應該提供一個簡短的理由來不實施該措施,對于標記為“HR”的東西,理由需要更詳細地解釋為什么你的智慧比編寫標準的專家更清楚。有些項目實際上被標記為“HR*”,這可以解釋為沒有借口只是這樣做(我們將忽略這樣一個事實,即這是一個信息豐富的附件,不應該包含任何“應”聲明)。“R”、“HR”等下的參考文獻。旨在表示實施此技術的工作量,但該標準沒有明確的指導,說明在這方面應該意味著什么。

FPGA 實現的設計流程包括如下步驟。

在HDL中創建所需電路的描述(也可以基于模型的輸入)

選擇具有足夠可重配置邏輯的目標 FPGA 來處理您的 HDL

使用軟件工具將行為代碼合成到 FPGA 中可用的可重新配置資源上

使用軟件工具生成上述配置的比特流表示,該表示可以加載到FPGA中

現在我想談談我認為在安全應用中使用FPGA的最大問題,即“軟錯誤”。

軟錯誤已在之前的“安全問題”博客中介紹過。這些是由包裝材料中存在的α粒子或來自太空的中子粒子引起的誤差,導致RAM單元和FF中存儲的值改變狀態。雖然ASIC和FPGA都可能包含RAM,軟錯誤問題相似,但FPGA的問題是,當可編程邏輯的配置存儲在RAM單元中時,單個位的擾動會有效地改變硬件。對于硬連線ASIC,邏輯功能是凍結的,不受α和中子粒子的影響,但對于FPGA來說,這是一個真正的問題。如果軟錯誤率為 1000 FIT/兆位(參見 IEC 61508-7:2010),則具有 1 萬配置位的 FPGA 的軟 FIT 將為 1000。

我注意到IEC 62380:2004允許計算FPGA的硬FIT,甚至在那里λ1每個晶體管的 20e-5/h 值高于 uC 和 DSP 的 3.4e-6。

FPGA在安全應用中的其他問題包括:

過時 – FPGA 通常設計在技術的最前沿,可能會過時 - 為了實現 65nm 上 ASIC 的性能,您可能需要在 20nm 上設計 FPGA,因為可重新配置邏輯帶來的開銷

如何實現片上硬件容錯(參見IEC 13-61508:2中的注釋2010)

實現高數字故障覆蓋率。表F.1要求數字ASIC>98.5%,但FPGA一旦編程,就沒有最低要求

IEC TS 61508-3-1:2016的相關性

與實現類似功能的ASIC相比,FPGA很可能很昂貴

FPGA用戶在HDL編碼可能不是公司核心競爭力的情況下實現HDL代碼的額外責任

與專用工業或汽車IC相比,溫度范圍有限

相對較高的功率(如果沒有別的,可能會導致更差的可靠性數字)

“宇宙的基本規則之一是沒有什么是完美的。完美根本不存在...沒有不完美,你和我都不會存在。

~斯蒂芬·霍金

盡管存在這些擔憂,但FPGA的靈活性,特別是對于快速原型設計和快速上市時間,一個硬件解決方案可以針對多個終端應用進行定制而無需重新設計PCB的事實,以及幾乎可以連接到任何東西的能力,這使得它們非常有用。對于小批量和概念驗證設計尤其如此。例如,嘗試找到一個帶有MIPI接口的漂亮工業處理器,這并不容易,但對于FPGA,您只需在HDL中實現膠水邏輯即可。

審核編輯:郭婷

-

微控制器

+關注

關注

48文章

7649瀏覽量

152108 -

FPGA

+關注

關注

1630文章

21796瀏覽量

606003 -

adc

+關注

關注

99文章

6533瀏覽量

545753

發布評論請先 登錄

相關推薦

題目出來了,但沒有什么資料

對新手非常有用的電子器件基礎資料

沒有源代碼可以過時的FPGA設計遷移?

Vim中默認未啟用但實際非常有用的選項

谷歌獲新專利 對創建沉浸式VR體驗非常有幫助

為什么蘋果手機無法顯示完美的屏幕顯示功能?

17個非常有用的Python技巧

一個簡單但非常有用的小前置放大器電路

沒有什么是完美的,但FPGA可能非常有用

沒有什么是完美的,但FPGA可能非常有用

評論