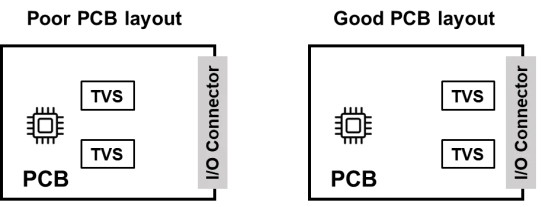

1TVS器件要盡可能布局在緊鄰干擾源的輸入端(端口靠近面板處)。

2連接TVS器件的導線要盡可能短且粗,以減小導線的寄生電感和低阻抗回路。并且保證TVS器件走線要比被保護對象的走線短,確保外界脈沖干擾通過TVS器件釋放。

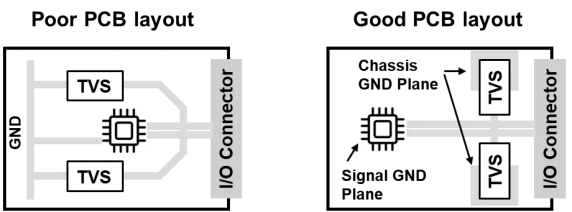

3TVS器件保護電路應該將能量直接泄放到保護地,不建議將其直接與工作信號地相連,以避免引起工作地平面信號反彈。

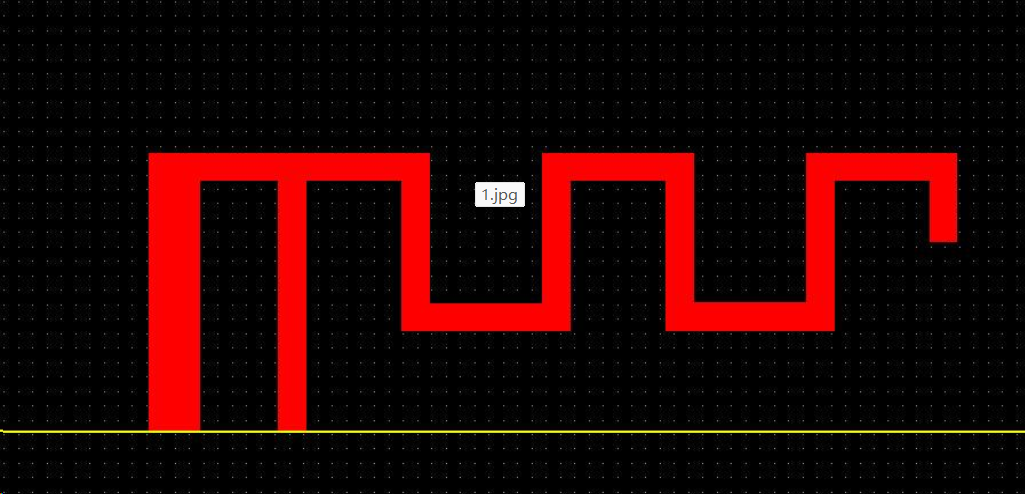

4繪制差分線的長度差應盡量小(控制在5mil以內),與其它信號網絡以及地的距離盡量在20mil以上,且兩側的測試點、串聯的電阻電容、上下拉電阻的擺放盡量避免直角。

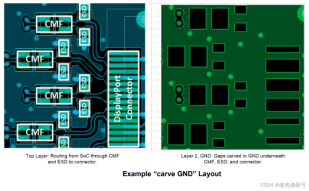

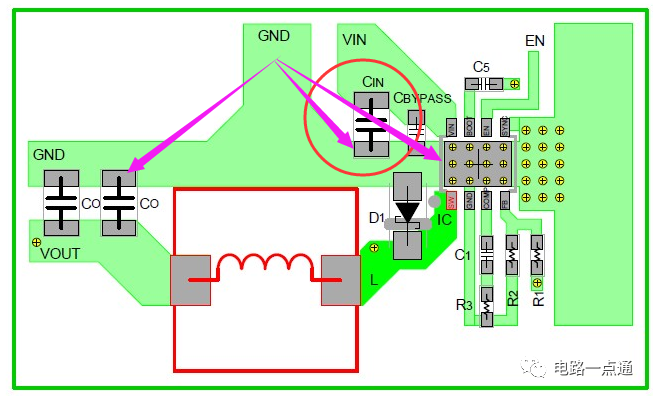

5建議在信號線換層孔附近添加回流孔,盡量減少換層孔;信號走線優先參考GND層,并保證參考平面完整。如果設計中無法避免跨平面參考,建議再跨平面分割處用旁路電容將回流信號連接起來;差分耦合電容、共模電感和ESD等器件盡量靠近DP座并對稱放置;DP座上機殼地與數字地完全分開單點連接;

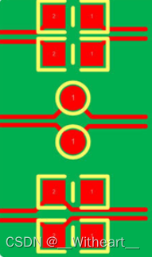

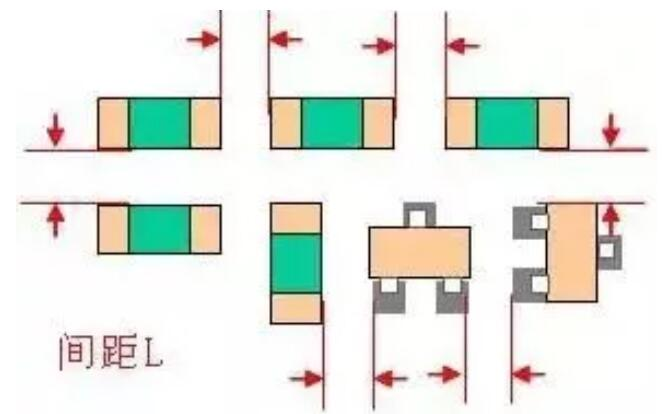

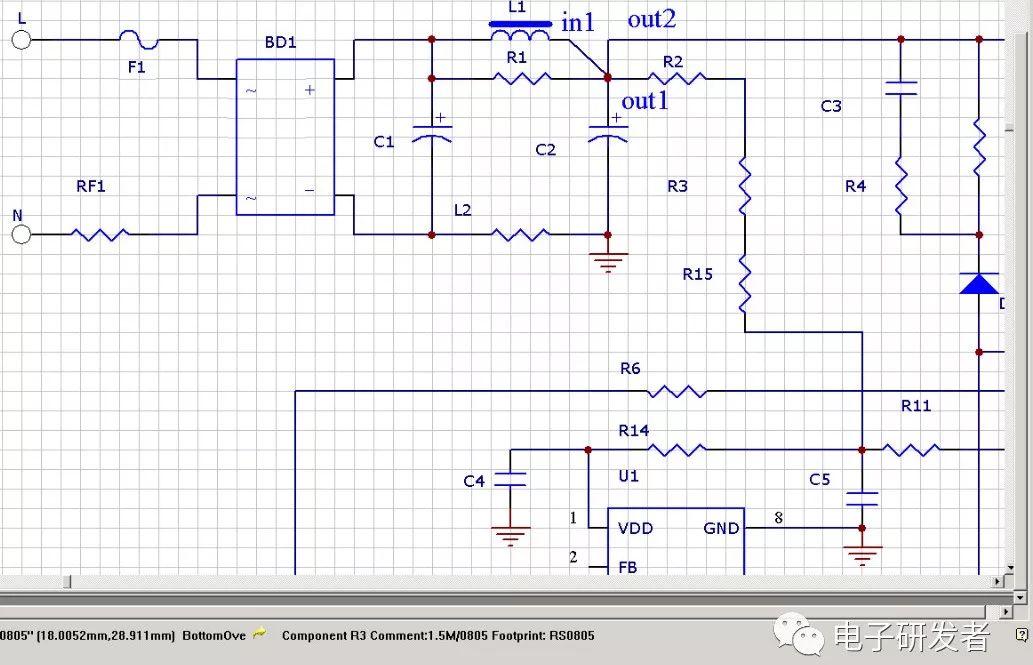

由于元器件的PAD width會導致阻抗不連續,因此建議在元器件pad下方的參考層挖空以減小阻抗的不連續性。下圖為Layout的一個例子。

晶揚電子 | 電路與系統保護專家

深圳市晶揚電子有限公司成立于2006年,是國家高新技術企業、國家專精特新“小巨人”科技企業,是多年專業從事IC設計、生產、銷售及系統集成的IC DESIGN HOUSE,擁有百余項有效專利等知識產權。建成國內唯一的廣東省ESD保護芯片工程技術研究中心,是業內著名的“電路與系統保護專家”。

-

元器件

+關注

關注

113文章

4747瀏覽量

92828 -

Layout

+關注

關注

14文章

406瀏覽量

61958 -

寄生電感

+關注

關注

1文章

156瀏覽量

14631 -

TVS器件

+關注

關注

0文章

20瀏覽量

6973

原文標題:晶揚小課堂|Layout設計注意事項

文章出處:【微信號:晶揚電子,微信公眾號:晶揚電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

藍牙2.4G倒F天線的layout注意事項

emi emc pcb layout注意事項

WiFi模塊應用選型參考及布局走線Layout注意事項

WiFi模塊應用選型參考及布局走線Layout注意事項

RF設計天線 PI型匹配layout注意事項

PCB電源板layout的設計注意事項說明

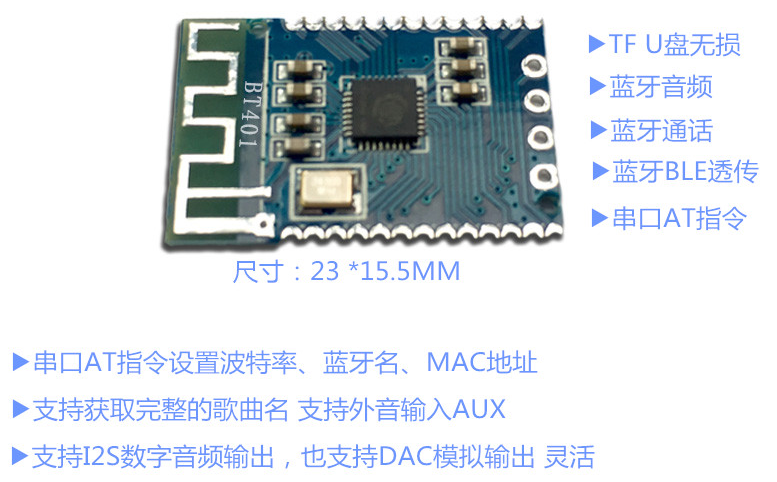

藍牙模塊BT401音頻BLE串口數傳的layout注意事項

Layout設計注意事項

Layout設計注意事項

評論