利用FPGA實現雙口RAM的設計及應用

概述:為了在高速采集時不丟失數據,在數據采集系統和

2010-04-16 14:08:36 11323

11323

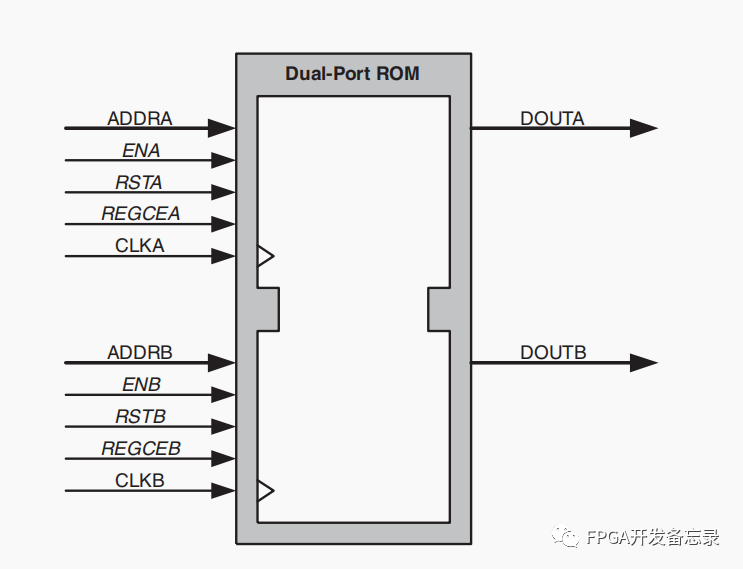

真雙口RAM給設計帶來很多便利。在高速存儲中,需要對連續的數據同時處理,使用簡單雙口RAM只能讀取一個數據,而使用真雙口RAM可以同時讀取兩個數據,這樣明顯提高讀取速度以及處理速度。

2018-06-29 08:54:07 32478

32478

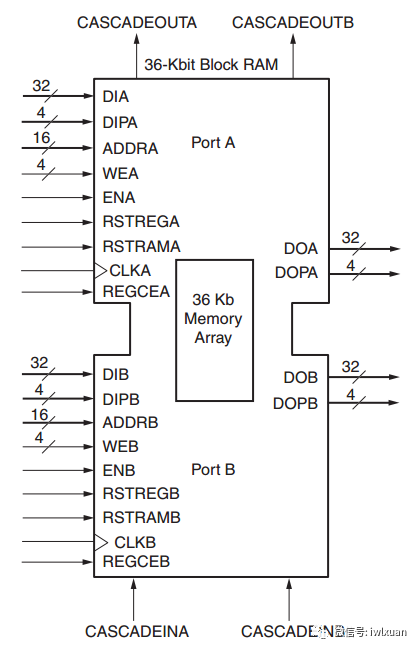

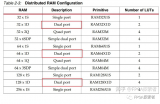

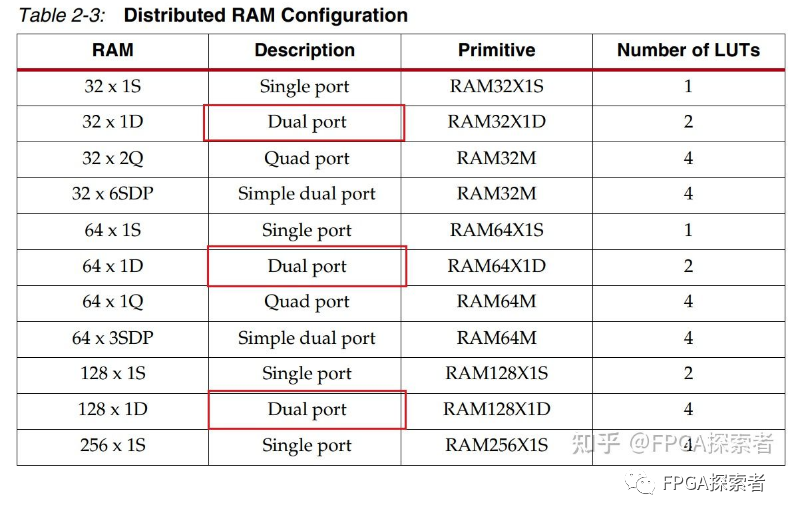

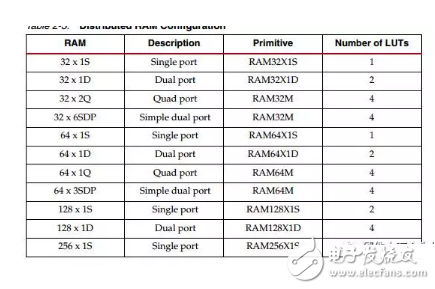

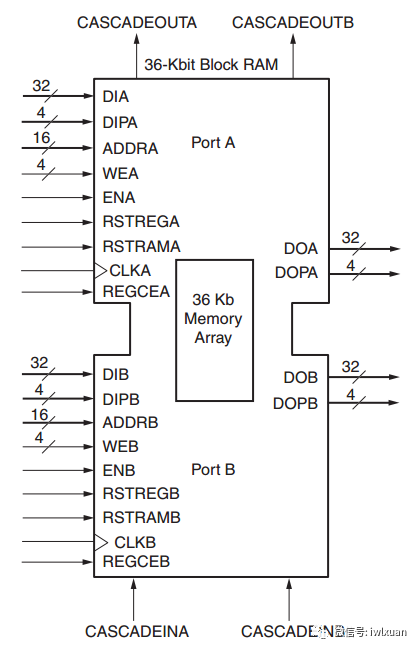

FPGA內嵌的存儲器單元包括塊RAM(BRAM)和分布式RAM。

2023-08-15 16:11:05 567

567

在選擇FPGA時,關注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因為它們是FPGA架構中的兩個核心資源,對于設計的性能和資源利用至關重要。

2023-11-21 15:03:06 548

548

你好,根據Atrix7數據手冊ds181,DRAM的最小時鐘周期為2.10 ns,因此最大工作頻率為479 MHz(參見第22頁)。其中,由于切片路由,DRAM的頻率將隨著其深度的增加而減小。但是,BRAM的最大工作頻率表示為509 MHz(參見第24頁)。我的問題是,BRAM作為慢組件和基于切片的邏輯作為快速組件,這些值是矛盾的。根據這些值,根據我的理解,BRAM比DRAM更快。如果是,那怎么樣?如果沒有那么為什么?請盡快回復。[R3] ds181_Artix_7_Data_Sheet.pdf 1963 KB

2020-03-19 09:13:44

大家好。我設計并模擬了簡單的RTL with Block RAMin Kintex 7。在合成和實現之后,vivado用于功率估計。當我使用分布式RAM時,會正確報告每個RAM的功耗。但是

2019-03-13 14:21:13

本系列將帶來FPGA的系統性學習,從最基本的數字電路基礎開始,最詳細操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業學生、初入職場小白及打算進階提升的職業開發者都可以有

2023-03-14 17:38:29

;MEM [15] = 8'hf;結束永遠@(posedge clk1) if(mem_we)開始 MEM [mem_waddr [3:0]]正如您所看到的,這是簡單而傳統的分布式RAM描述,具有全寬

2019-06-12 14:17:08

我打算在Virtex7器件中使用分布式RAM作為單端口RAM,用于我的濾波器設計。 RAM將初始配置,然后只有讀取將從RAM開始。我的讀地址生成來自CLK2,與寫時鐘CLK1異步。我可以像這樣

2019-04-16 09:52:29

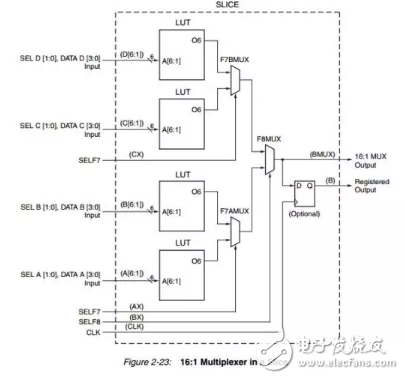

您好!分布式RAM和Block RAM之間究竟有什么區別?兩者都只是芯片內存,對吧?但我不知道兩者之間的區別。和..下一個問題.. isaboutMUX ..根據7系列概述,7系列FPGA支持全范圍

2020-07-19 06:37:51

喜我是這個社區的新手,所以如果這種話題不符合該部分或者我濫用論壇,我會提前道歉。我有一個項目,我需要實例化2000個分布式rams,由2000個數據文件初始化。問題是,當我嘗試使用iSim模擬我

2019-03-12 13:01:59

大家好 ...我在實現大小為65535 * 3的分布式RAM時出現問題,在大約2小時內合成時發生了很大的延遲并且沒有停止,對這個問題有什么解釋嗎?提前致謝以上來自于谷歌翻譯以下為原文Hello

2019-06-25 11:03:45

幾種分布式發電簡介2.分布式發電與配電網互聯問題3.微型電網技術4.分布式發電(電源)技術應用的障礙和瓶頸5.分布式發電(電源)技術發展方向6.結語

2011-03-11 13:37:39

分布式聲波傳感系統DAS

2020-12-21 07:48:43

當討論分布式系統時,我們面臨許多以下這些形容詞所描述的 同類型: 分布式的、刪絡的、并行的、并發的和分散的。分布式處理是一個相對較新的領域,所以還沒有‘致的定義。與順序計算相比、并行的、并發的和分布式的計算包括多個PE問的集體協同動作。這些術語在范圍一卜相互覆蓋,有時也交換使用。

2020-03-31 09:01:18

分布式軟件系統分布式軟件系統(Distributed Software Systems)是支持分布式處理的軟件系統,是在由通信網絡互聯的多處理機體系結構上執行任務的系統。它包括分布式操作系統

2009-07-22 14:53:12

我今天正在實現FIFO,我想知道FIFOPrimitive和Block RAM實現之間的區別是什么。根據我的理解,它們使用相同的底層RAM原語,但FIFOPrimitive不能有不同的R / W方面

2019-02-27 14:16:45

設計理念HarmonyOS 是面向未來全場景智慧生活方式的分布式操作系統。對消費者而言,HarmonyOS 將生活場景中的各類終端進行能力整合,形成“One Super Device”,以實現

2020-09-22 17:11:07

Quartus II 中定制的RAM是分布式的還是塊的

2014-03-10 17:51:45

嗨,為了調試系統,我需要在系統運行時動態讀取Block-RAM內容....我只有JTAG線,我不能在FPGA中制作一個特定的塊用于讀取內容并通過JTAG等發送它們。我可以使用ISMP 13.2作為

2019-06-11 07:36:08

TSP分布式控制有什么優勢?TSP分布式控制提高了測試速度并且降低了測試成本。

2021-05-12 06:19:56

Vivado綜合可以理解多種多樣的RAM編寫方式,將其映射到分布式RAM或塊RAM中。兩種實現方法在向RAM寫入數據時都是采取同步方式,區別在于從RAM讀取數據時,分布式RAM采用異步方式,塊RAM

2020-09-29 09:40:40

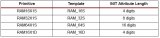

`Xilinx FPGA入門連載48:FPGA片內RAM實例之RAM配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1新建源文件打開

2016-01-22 13:39:24

《無線通信FPGA設計》分布式FIR的并行改寫,結果與matlab仿真結果基本吻合

2017-02-26 09:09:47

之前我們分享過分布式軟總線和分布式數據管理,今天主要說一下OpenHarmony的分布式任務調度,分布式任務調度是建立在分布式軟總線和分布式數據管理基礎之上,目標是為了構建統一的分布式服務管理(發現

2022-07-18 17:06:45

我正在運行Spartan 6 block ram的模擬。時鐘速度為100Mhz。塊ram的寫作運作良好。我可以在內存中看到數據。但是當我讀取數據時,輸出有2個時鐘的延遲。在塊ram用戶guidt中

2019-07-25 08:15:27

有讀取和/或寫入數據總線。 寫入RAM通常是同步完成的。閱讀通常是同步進行的,但有時可以異步進行。 Blockram與分布式RAM現在,FPGA中有兩種內部RAM:Blockrams和分布式RAM。通常

2020-09-10 11:11:57

嗨,我在使用BRAM時出現溢出問題(110%)有沒有辦法使用tcl命令,我說某些單元格,實現它們作為分布式RAM而不是BRAM?修改一些屬性或什么?謝謝,以上來自于谷歌翻譯以下為原文Hi, I'm

2018-10-31 15:23:19

大家好,我正在嘗試用VHDL中的初始值實現分布式RAM。我的目標是Virtex-5- 某處有一個例子嗎?我知道有些Virtex組件確實有一個可以使用泛型傳遞的初始值 - 我應該將它與全局重置或其他

2019-02-26 11:15:14

在我的一個FPGA類中,我被要求使用coregen創建一個blcok ram(8dx16w),單端口ram IP。我在Windows XP,Service Pack 3上使用Xilinx ISE

2019-06-05 13:39:14

您好,我正在Virtex7上實現(127x8)即(深度x寬度)內存。我有以下問題1.使用速度,效率和功率使用的分布式ram或block ram interms來實現它是否可行。2.他們使用分布式

2020-03-23 07:17:45

。塊RAM(BRAM),容量較大,數量少,速度較快。分布式RAM:容量小,數量多,速度不如BRAm快。一般使用方法和接口是一樣的。

2018-08-23 09:14:59

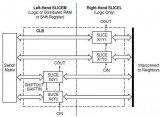

一、查找表LUT就是查找表,對于4輸入的LUT而言,實際上就是4位地址位,一位數據位的存儲器,能夠存儲16位數據,所以我們在FPGA設計中可以用LUT組建分布式的RAM。這樣也可以解釋我們在設計中

2021-07-28 08:42:17

一種基于ZigBee和ModBus的分布式電子警察系統設計

2021-05-31 06:24:15

RAM是FPGA中常用的基礎模塊,可廣泛用于緩存數據的情況,同樣它也是ROM,FIFO的基礎。本實驗將為大家介紹如何使用FPGA內部的RAM以及程序對該RAM的數據讀寫操作。1.實驗原理Xilinx

2021-01-07 16:05:28

使用 Jmeter 進行分布式測試;檢索日志

2023-05-10 13:00:46

我們如何使用Virtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-27 06:43:47

我們如何使用Virtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-29 09:16:36

我們如何使用Virtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = [1 2 3 45 6 7 8 9 1 4 5 232 1]

2020-05-29 14:41:56

的選擇無線分布式采集來進行。現有的無線分布式采集系統中,往往使用單片機、DSP等作為系統的主控控制單元。但是由于其自身工作特點,往往對于精確的定時控制以及并行處理能力上比FPGA弱。

2019-10-14 07:10:38

分布式車身控制系統的結構是怎樣構成的?分布式車身控制系統有哪些功能?

2021-05-13 07:03:30

如何在第17和第20頁上安裝clb用戶指南(ug384 v1.1)中描述的RAM32X2Q或RAM64X1Q。這些不會出現在用于hld或原理圖輸入的spartan庫中。他們也沒有在軟件的13/2版本中顯示分布式內存生成器。這是額外的成本項目還是我還缺少另一件事?

2019-10-25 09:34:48

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一個單獨的奇偶校驗寫使能位,但在FPGA RAM中沒有單獨的Pariaty寫使能位。 如何實現ASIC RAM奇偶校驗寫入啟用ino FPGA RAM。謝謝娜文G K.

2020-04-24 09:37:05

什么是分布式天線系統?如何對分布式天線系統(DAS)進行優化?

2021-05-24 06:03:56

什么是分布式干擾系統?分布式干擾系統是一種綜合化、一體化、小型化、網絡化和智能化系統,是將眾多體積小,重量輕,廉價的小功率偵察干擾機裝置在易于投放的小型平臺上,撒布在接近***擾目標空域地,通過指令

2019-08-08 06:57:44

作者:liuxun,HarmonyOS測試架構師HarmonyOS是新一代的智能終端操作系統,給開發者提供了設備發現、設備連接、跨設備調用等豐富的分布式API。隨著越來越多的開發者投入到

2021-12-13 18:07:58

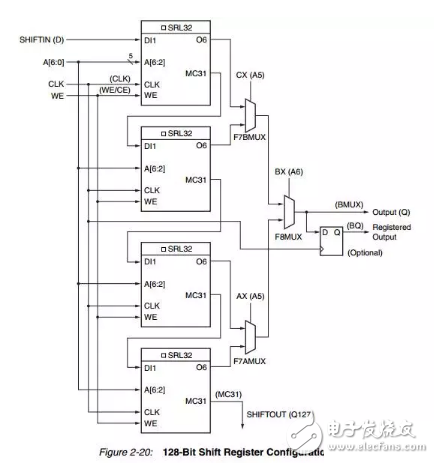

嗨,我正在xilinx virtex7上使用分布式RAM實現((深度)128x(寬度)8)位存儲器結構。從理論上講,它應該占用128x8 = 1024; 1024年至1064年= 16; 16/4

2020-04-06 07:19:30

我正在嘗試使用virtex 5上的Block RAM來實現延遲線。延遲線需要將數據延遲一個時鐘周期。這可能使用Block RAM嗎?我嘗試使用簡單的雙端口RAM,“先讀”作為操作模式。我正在寫一個

2020-06-18 15:40:33

你好,我正在開發一個在VC709開發板上使用Virtex7 FPGA的系統。該應用程序使用32Mb的板載Block RAM作為設計中的存儲元件。 FPGA配置序列完成后,有沒有一種方法可以使用PC上的JTAG / USB接口直接寫入和讀取Block RAM的內容?謝謝,

2019-09-29 14:00:01

分布式的濾波器算法是什么?一種基于FPGA分布式算法的濾波器設計實現

2021-04-29 07:13:23

,維克多Rdp_fifo3.v 3 KB以上來自于谷歌翻譯以下為原文I am trying to use the block ram on Xilinx Spartan 3AN (XC3S400AN

2019-06-04 09:08:32

嗨,我想為我的設計使用比特流加密,我遇到了一個關于9K Block RAM的問題,在答案記錄39999中描述了r然后我決定在我的設計中刪除所有9k Block RAM并將它們更改為16k Block

2019-06-06 07:23:18

嗨!我有一個關于分布式RAM和Block RAM的問題。芯片中有menexternalmemory或內存嗎?請詳細告訴我。謝謝!

2019-11-07 09:07:16

一個關于分布式RAM時序的問題。你可以看到Attchments。在藍線中,如果CLK將0更改為1. AI / BI / CI / DI將被復制到輸出。在這種情況下,藍色十字架的意思是什么?我不知道它

2019-11-07 09:31:52

我想知道“邏輯單元”的意思..我知道“Block RAM”,“分布式RAM”“CLB”......以及ETC ..但是,我不知道“Logic Cell”..請讓我知道..謝謝!

2019-11-08 16:38:38

為了在高速采集時不丟失數據,在數據采集系統和CPU之間設置一個數據暫存區。介紹雙口RAM的存儲原理及其在數字系統中的應用。采用FPGA技術構造雙口RAM,實現高速信號采集系

2010-02-11 11:20:27 69

69 基于Actel FPGA 的雙端口RAM 設計雙端口RAM 芯片主要應用于高速率、高可靠性、對實時性要求高的場合,如實現DSP與PCI 總線芯片之間的數據交換接口電路等。但普通雙端口RAM 最大

2010-11-15 17:44:19 82

82 RAM,RAM工作原理是什么?

RAM (Random Access Memory隨機存貯器)是指通過指令可以隨機地、個別地對每個存儲單元進行訪問、訪問所需時間基本固定、且與存

2010-03-24 16:03:02 10297

10297 GD32-Colibri-F207實驗板RAM-RAM,很好的GD32資料,快來學習吧。

2016-04-21 10:49:49 2

2 帶有異步寫/同步讀的SRAM,其中的同步讀取可以使用與分布式RAM相關聯的觸發器實現。

2017-02-11 13:54:59 2160

2160

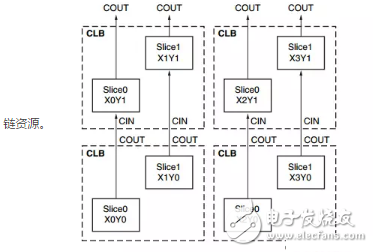

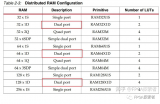

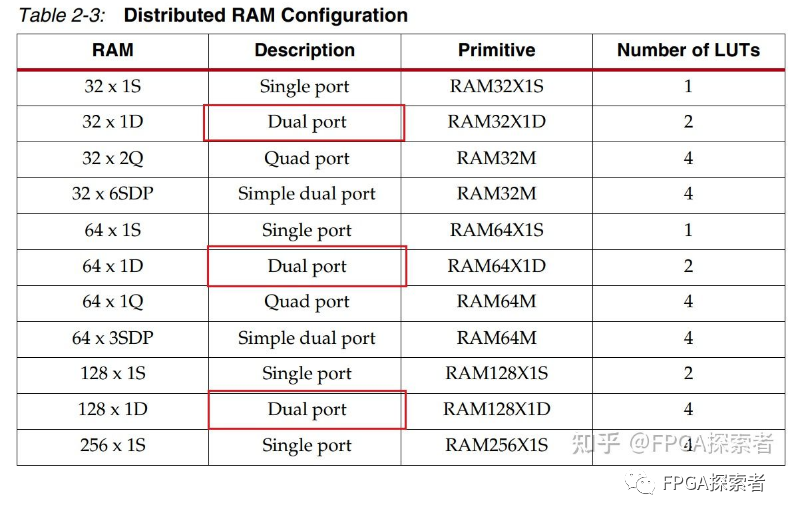

在賽靈思Spartan-3、3E等系列的FPGA中,其邏輯單元CLB中一般含有不同數量的單端口RAM(SRAM)或者雙端口RAM(DRAM),這里的“單”或者“雙”是由我們開發人員定義的。

2017-02-11 13:56:11 6348

6348

前面簡要介紹了Spartan-3系列FPGA中分布式RAM的基本特性。為什么不從更高級的Virtex系列入手呢?我仔細看了一下各個系列的介紹、對比,Spartan系列基本就是Virtex系列的精簡版,其基本原理是一樣的,所以從簡單的入手來融會貫通未嘗不是一個好辦法。

2017-02-11 13:57:40 1176

1176

前面講了分布式RAM的方方面面,下面以RAM_16S為例,分別給出其在VHDL和Verilog HDL下面的模板代碼(在ISE Project Navigator中選擇 Edit---

2017-02-11 13:59:33 1323

1323 FPGA內部的RAM M9K

2017-04-07 11:40:04 4

4 FPGA中RAM的使用探索。以4bitX4為例,數據位寬為4,深度為4。

2018-03-28 17:07:28 9726

9726

大家好,又到了每日學習的時間了,今天我們來聊一聊在FPGA設計中RAM的兩種使用方法,RAM是用來在程序運行中存放隨機變量的數據空間,使用時可以利用QuartusII的LPM功能實現RAM的定制

2018-06-08 11:30:28 19562

19562 本文介紹了如何在FPGA 中利用Block RAM 的特殊結構實現HDTV視頻增強算法中灰度直方圖統計。

2019-07-10 08:10:00 2578

2578 了解新的Block RAM級聯功能,如何使用它,以及如何利用其功能和性能優勢。

2018-11-23 06:56:00 4470

4470 些大材小用,因此xilinx公司在其FPGA內部專門集成了很多存儲器模塊,稱作Block RAM,其猶如slice海洋當中的一顆顆明珠,專門實現數據暫存功能,且每個時鐘區域都布置了若干個Block

2020-11-23 14:08:43 7379

7379

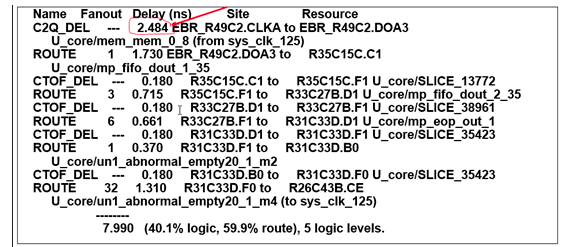

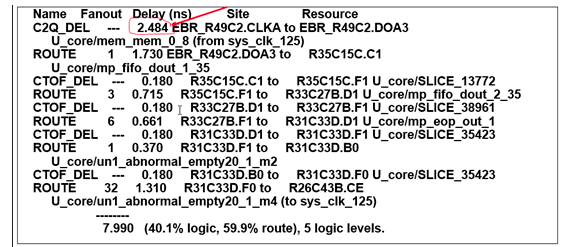

關于Block RAM的寄存器輸出,我們在《通過RTL改善時序的技巧之Block RAM的輸出》中介紹過。如果我們在時序報告中關鍵路徑上看到這樣一條信息: 在第一級的C2Q delay(clock

2021-03-26 15:50:27 1570

1570

本文檔的主要內容詳細介紹的是FPGA的RAM存儲資源詳細資料說明包括了:1、 FPGA存儲資源簡介,2、 不同廠家的 Block RAM 布局,3、 塊 RAM 和分布式 RAM 資源,4、 Xilinx Block RAM 架構及應用

2020-12-09 15:31:00 10

10 在FPGA中block ram是很常見的硬核資源,合理的利用這些硬件資源一定程度上可以優化整個設計,節約資源利用率,充分開發FPGA芯片中的潛在價值,本文結合安路科技FPGA做簡單總結,說明基本原理。

2020-12-24 14:28:09 916

916 FPGA可以調用分布式RAM和塊RAM兩種RAM,當我們編寫verilog代碼的時候如果合理的編寫就可以使我們想要的RAM被綜合成BRAM(Block RAM)或者DRAM(Distributed

2020-12-30 16:27:52 9

9 RAM是FPGA中常用的基礎模塊,可廣泛用于緩存數據的情況,同樣它也是ROM,FIFO的基礎。本實驗將為大家介紹如何使用FPGA內部的RAM以及程序對該RAM的數據讀寫操作。

2022-02-08 15:50:49 12183

12183

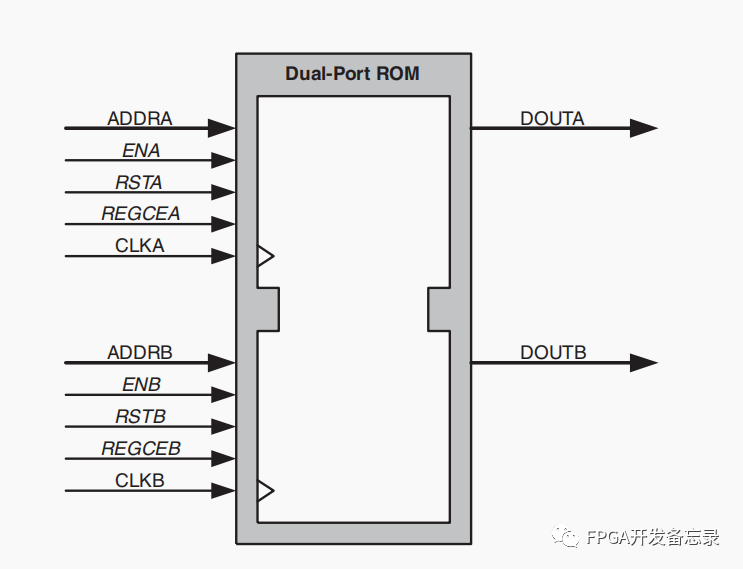

單口 RAM(Single RAM)、雙口 RAM(Dual RAM)、簡單雙口 RAM(Simple-Dual RAM)、真雙口 RAM(True-Dual RAM)有什么不同? 對于 分布式

2021-05-03 09:47:00 7234

7234

RAM :隨機存取存儲器(random access memory,RAM)又稱作“隨機存儲器”。

2023-04-25 15:58:20 5064

5064

單口 RAM(Single RAM)、雙口 RAM(Dual RAM)、簡單雙口 RAM(Simple-Dual RAM)、真雙口 RAM(True-Dual RAM)有什么不同?

2023-06-25 17:47:11 1970

1970

本文主要講述了Speedster7t FPGA的片上SRAM,也就是Block RAM針對傳統的結構所做出的一些優化。

2023-07-13 17:24:15 302

302

設計都涉及到對RAM的讀寫操作。在FPGA芯片中,RAM也叫做存儲塊(Block RAM),可以存儲大量的數據。 FPGA中的RAM可以一次讀取多個數據,這是因為RAM的結構是一個多列的數據表格,其中每一列都是一個包含多個存儲單元的塊。通過在時鐘的一次上升沿來讀取RAM中的數據,這個操作必須在一個

2023-10-18 15:28:20 598

598 FPGA雙口RAM的使用主要涉及配置和使用雙端口RAM模塊。雙端口RAM的特點是有兩組獨立的端口,可以對同一存儲塊進行讀寫操作,從而實現并行訪問。

2024-03-15 13:58:14 81

81

電子發燒友App

電子發燒友App

評論